Method for improving stress on IGBT (insulated gate bipolar translator) back surface

A technology of stress and stress distribution, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., and can solve problems such as easy cracking of silicon wafers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

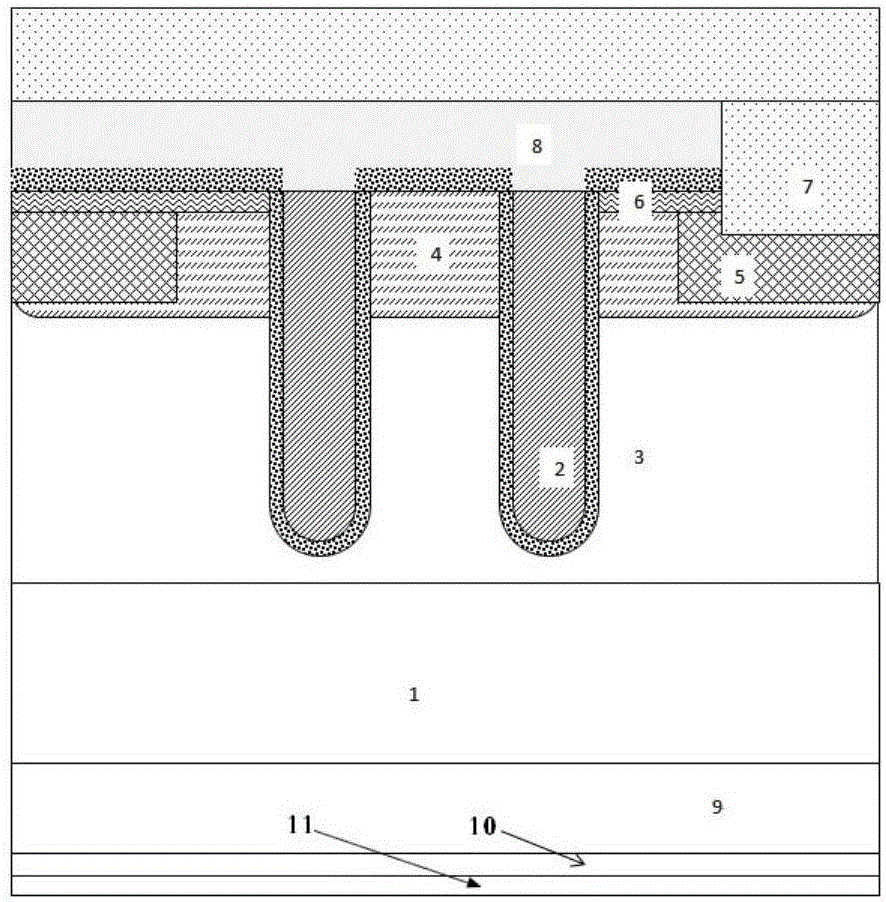

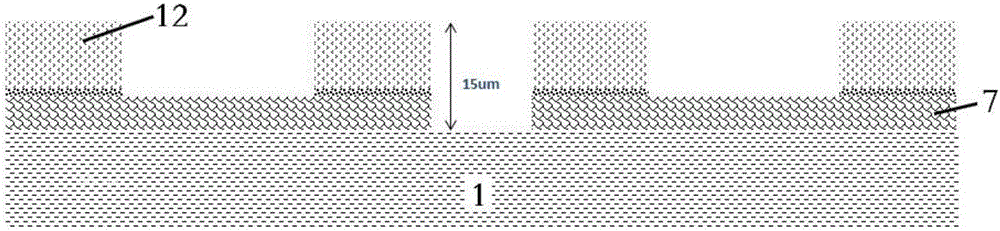

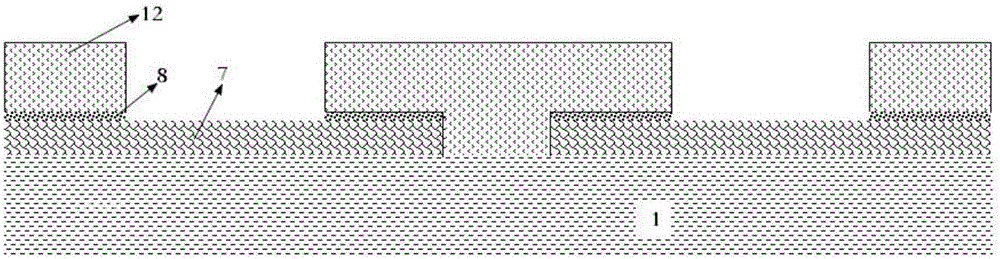

[0016] The method for improving the IGBT stress of the present invention, for the polyimide covered on the passivation layer on the front side of the silicon chip, when the scribe groove is defined by photolithography, the exposure of the scribe groove on the polyimide is determined by Light is changed to dark, and after exposure, the polyimide in the scribe groove area remains. The polyimide retained in the scribe groove area can disperse the stress of the silicon chip and improve the stress distribution of the silicon chip.

[0017] Another way is, for the polyimide covered on the passivation layer on the front side of the silicon wafer, when the scribe groove is defined by photolithography, the exposure of the scribe groove on the polyimide is still kept bright, appropriate Add some virtual graphics, which are defined as dark during exposure, and these virtual graphics can be transferred to the polyimide layer. After exposure, the polyimide layer can be evenly distributed o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More