High-precision low-jitter clock recovery system

A clock recovery, low jitter technology, applied in the direction of automatic power control, electrical components, etc., can solve the problems of receiver clock lockout, high-speed code stream inter-symbol interference, communication system interruption, etc., to improve phase detection accuracy, debugging Low difficulty and good consistency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

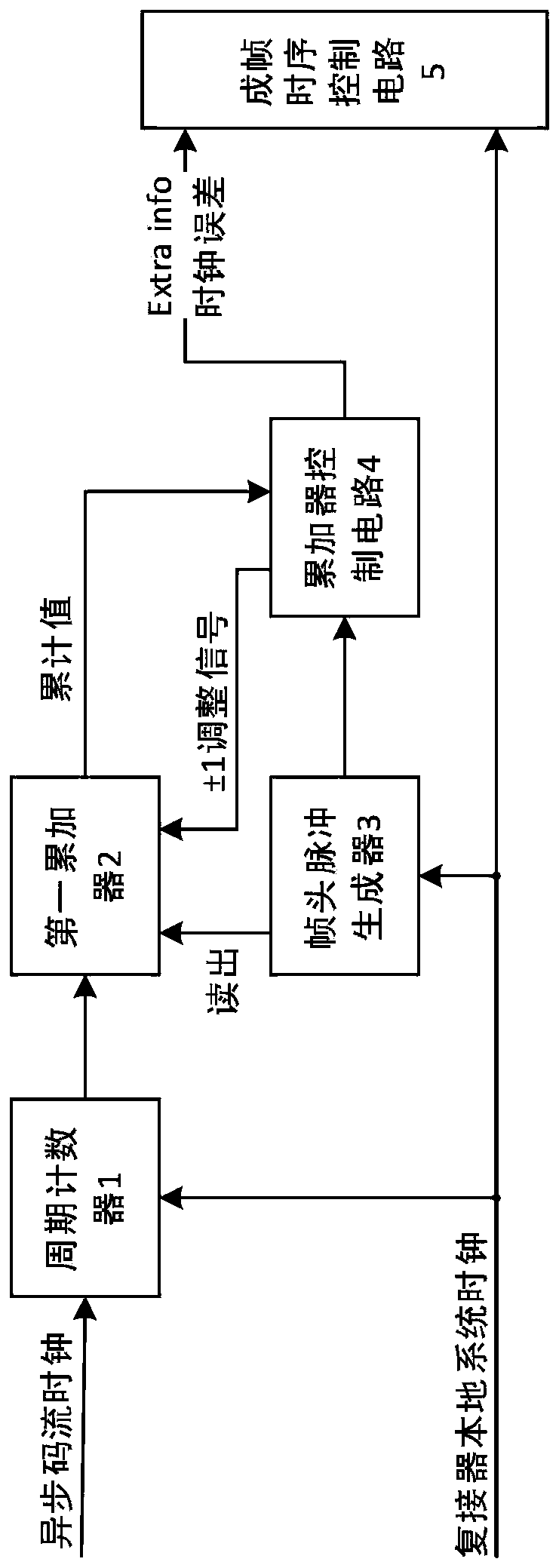

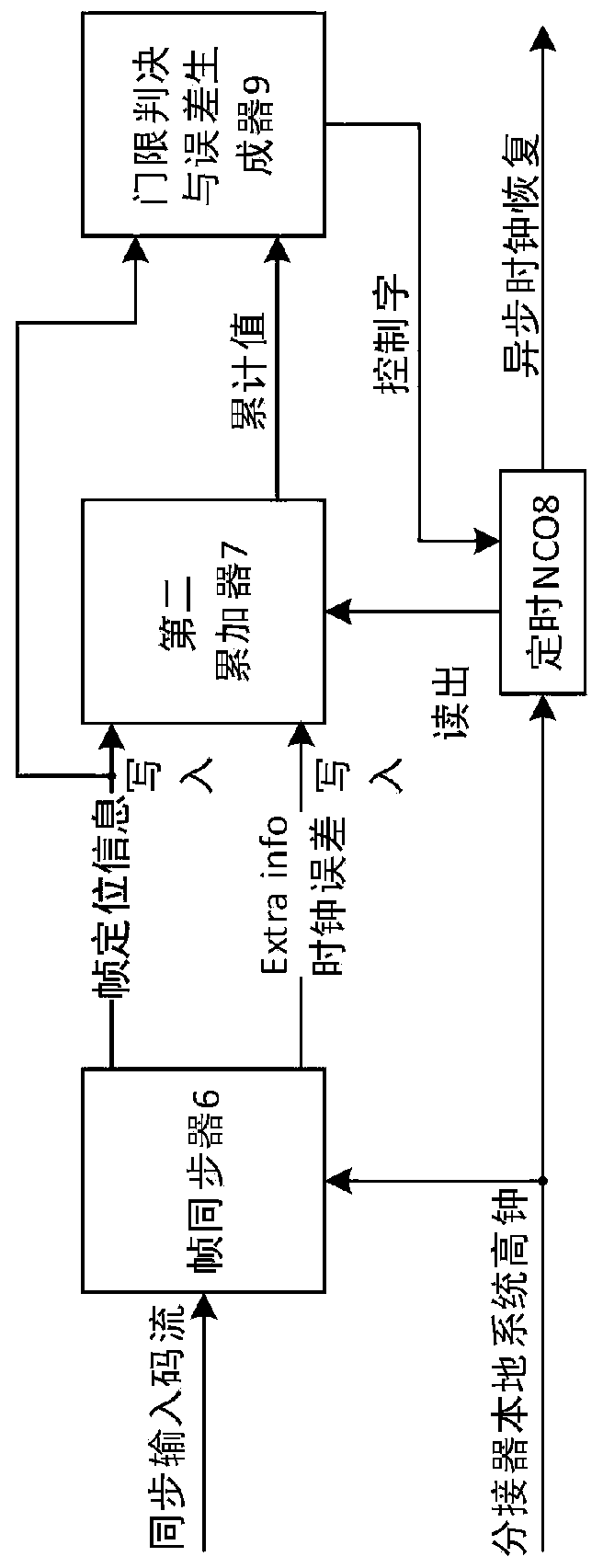

[0024] refer to Figure 1 to Figure 3 To further explain the present invention

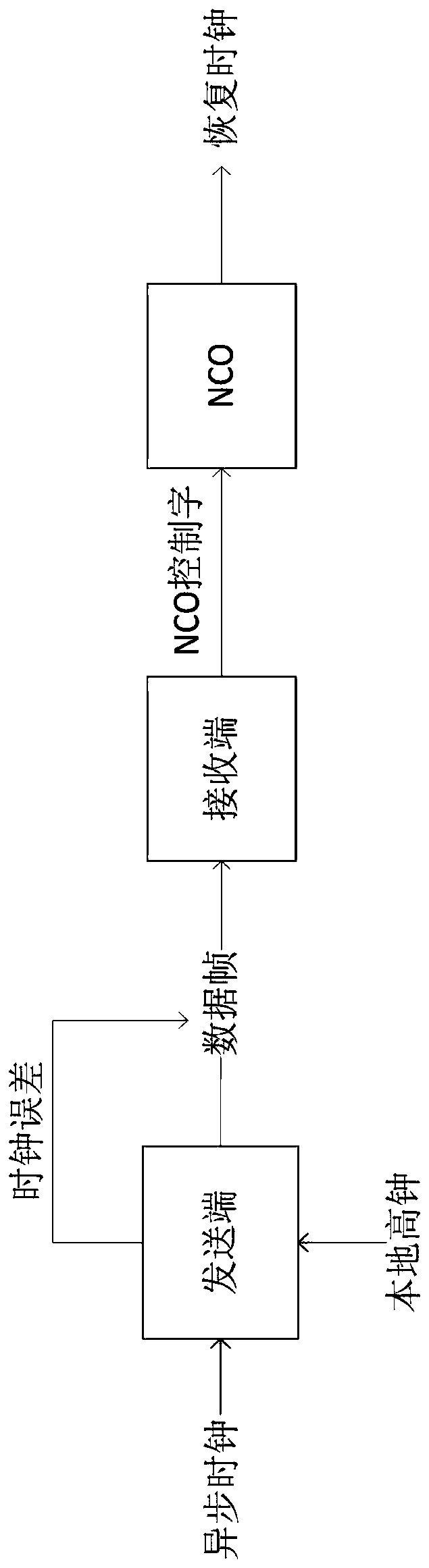

[0025] figure 2 It is a block diagram of the clock error generation principle at the sending end of the present invention, which includes each main processing module for generating the clock error.

[0026] Cycle counter 1 is used to sample and count the input asynchronous code stream clock according to the high clock of the local system, and obtain the cycle count value of the asynchronous code stream based on the local clock of the sending end. When each cycle of the asynchronous code stream clock ends, write the cycle count value to into the first accumulator 2;

[0027] The first accumulator 2 is used to read the accumulated value after receiving the read instruction;

[0028] The frame head pulse generator 3 is used for generating the pulse of marking the frame head position according to the high clock of the local system, and sends a read instruction to the first accumulator 2 when gener...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com