Multi-power-domain multi-clock-domain first-in first-out queue, integrated circuit chip and computer equipment

A first-in-first-out queue, multi-clock domain technology, applied in the field of first-in, first-out (FIFO) queues, can solve problems such as increasing signal transmission delay, reducing system operating frequency, affecting logic design delay, etc., to improve clock frequency, eliminate Effects of Signal Propagation Delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

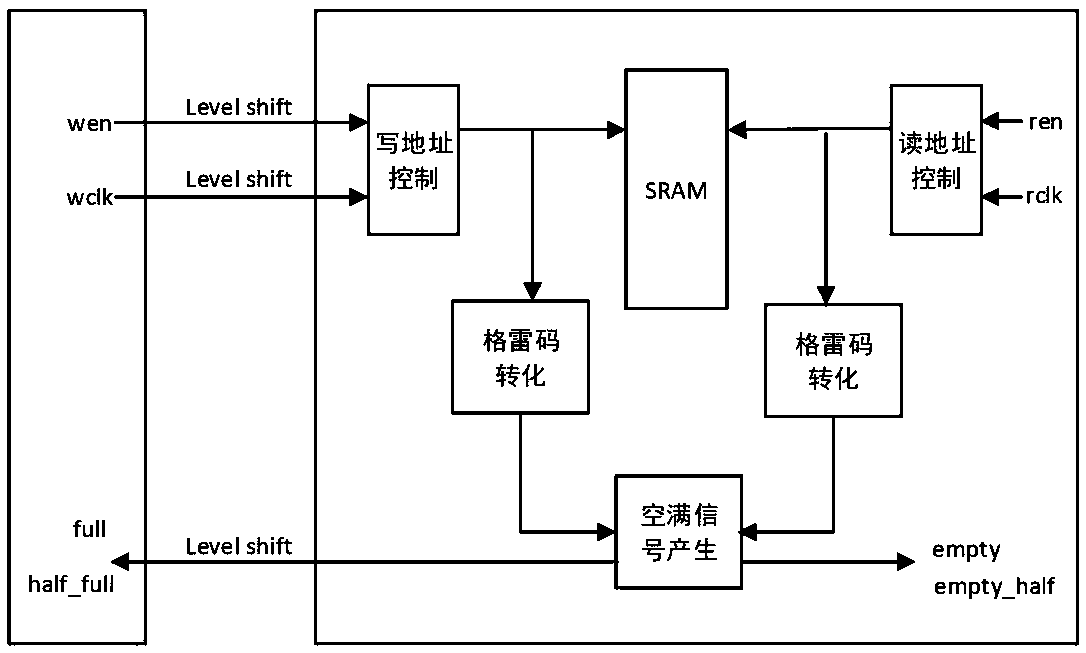

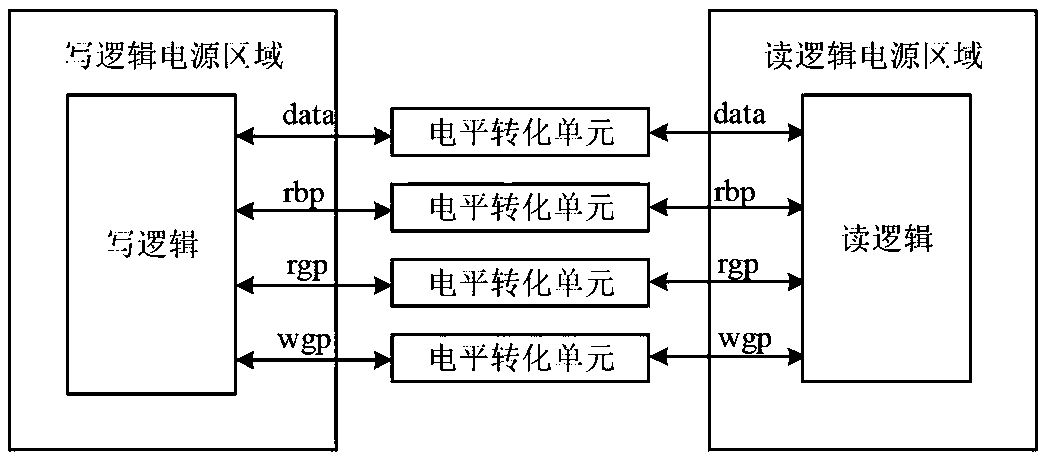

[0024] Such as figure 2 As shown, the multi-power domain multi-clock domain FIFO queue in this embodiment includes write logic, read logic, write logic power domain and read logic power domain, the write logic is in the write logic power domain, and the read logic is in the read logic power domain In the power domain, the write logic power domain and the read logic power domain are provided with a plurality of level conversion units for completing the conversion of the power domain, and the write logic and the read logic are in different clock domains.

[0025] Such as figure 2As shown, in this embodiment, there are four sets of signal transmission channels between the write logic and the read logic, and the four sets of signals include buffer data data, binary read pointer rbp, gray code read pointer rgp, and gray code write pointer wgp, And each group of signals is connected in series with a level shift unit (Level Shift). Since the power domain conversion is completed th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More