Photoelectric integrated device and preparation method thereof

A photoelectric integration and device technology, applied in the direction of electrical components, semiconductor devices, circuits, etc., can solve the problems of long process cycle, high production cost, incompatible Si process, etc., and achieve low process cost, high device integration, and device structure novel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

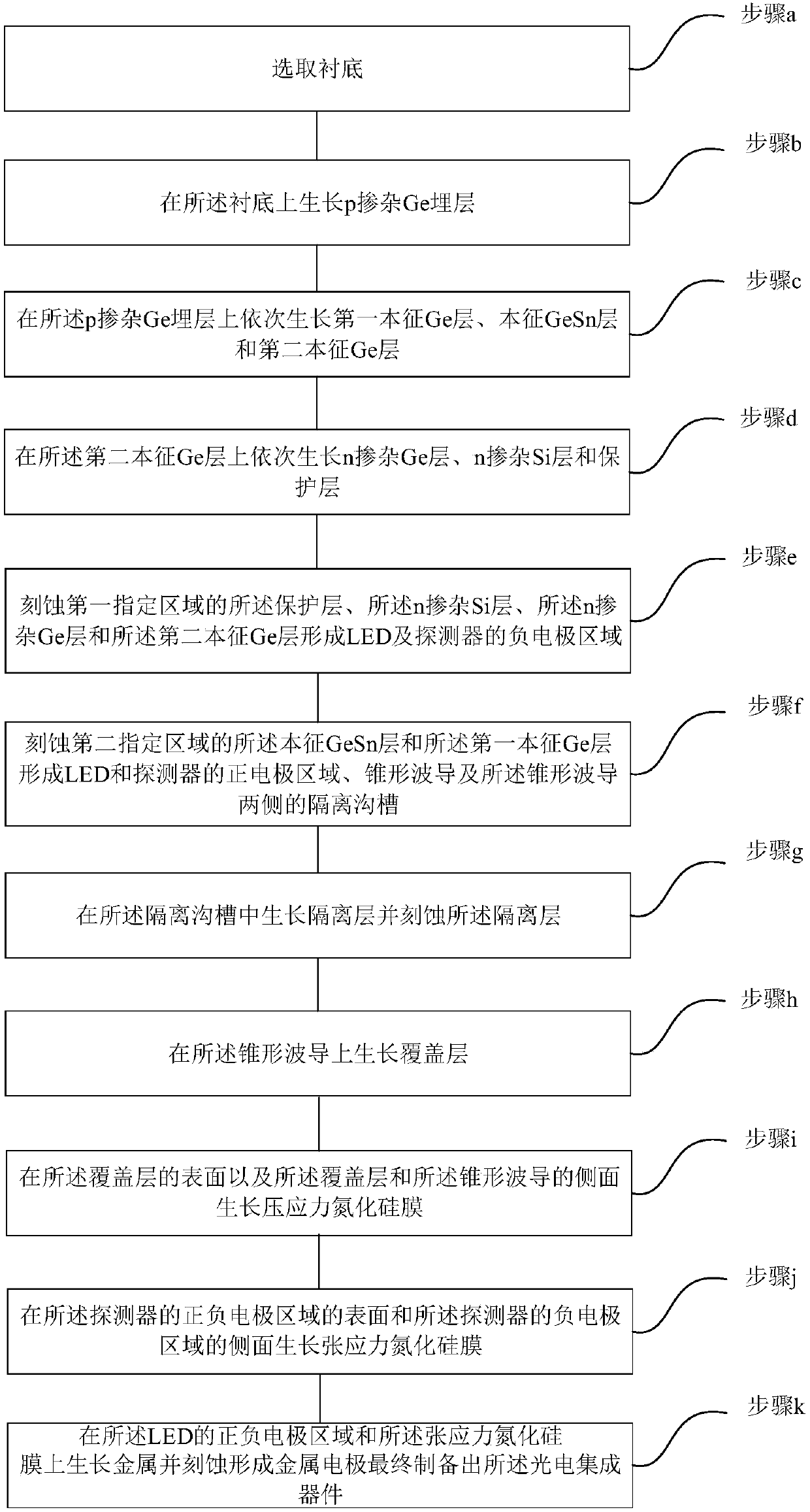

[0065] See figure 1 , figure 1 It is a schematic flowchart of a method for preparing an optoelectronic integrated device provided by an embodiment of the present invention. The method comprises the steps of:

[0066] Step a, select substrate;

[0067] Step b, growing a p-doped Ge buried layer on the substrate;

[0068] Step c, sequentially growing a first intrinsic Ge layer, an intrinsic GeSn layer and a second intrinsic Ge layer on the p-doped Ge buried layer;

[0069] Step d, growing an n-doped Ge layer, an n-doped Si layer and a protective layer sequentially on the second intrinsic Ge layer;

[0070] Step e, etching the protection layer, the n-doped Si layer, the n-doped Ge layer and the second intrinsic Ge layer in the first designated area to form the negative electrode area of the LED and the detector, respectively;

[0071] Step f, etching the intrinsic GeSn layer and the first intrinsic Ge layer in the second specified area to form the positive electrode area of...

Embodiment 2

[0106] See Figure 2a ~ Figure 2n , Figure 2a ~ Figure 2n A schematic diagram of the preparation process of an optoelectronic integrated device provided by the embodiment of the present invention. On the basis of the above-mentioned embodiments, this embodiment will introduce the preparation process of the optoelectronic integrated device proposed by the present invention in detail. The method includes:

[0107] S101. Substrate selection

[0108] like Figure 2a As shown, the p+ silicon (Si) substrate 01 is selected as the initial material, and the doping concentration is 10 18 cm -3 ;

[0109] S102, buried layer growth

[0110] like Figure 2b As shown, at a temperature of 330°C, epitaxial growth with a thickness of 50 nm and a doping concentration of 10 20 cm -3 The p++ doped Ge buried layer 02;

[0111] S103. Growth of the first intrinsic Ge layer

[0112] like Figure 2c As shown, at a temperature of 275° C. to 325° C., a first intrinsic Ge layer 03 with a thick...

Embodiment 3

[0151] See image 3 , image 3 It is a schematic diagram of an optoelectronic integrated device provided by an embodiment of the present invention. On the basis of the above embodiments, the present invention also provides an optoelectronic integrated device, wherein the optoelectronic integrated device is formed by the method described in the above embodiment.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More