High-speed DDR single event effect evaluation system and method based on FPGA

A single event effect and evaluation system technology, applied in the field of high-speed DDR4 single event effect evaluation system, can solve the problems of cumbersome process, single application object, and control logic is difficult to be compatible with advanced memory, etc., to reduce costs and reduce hardware and software resources. effect used

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

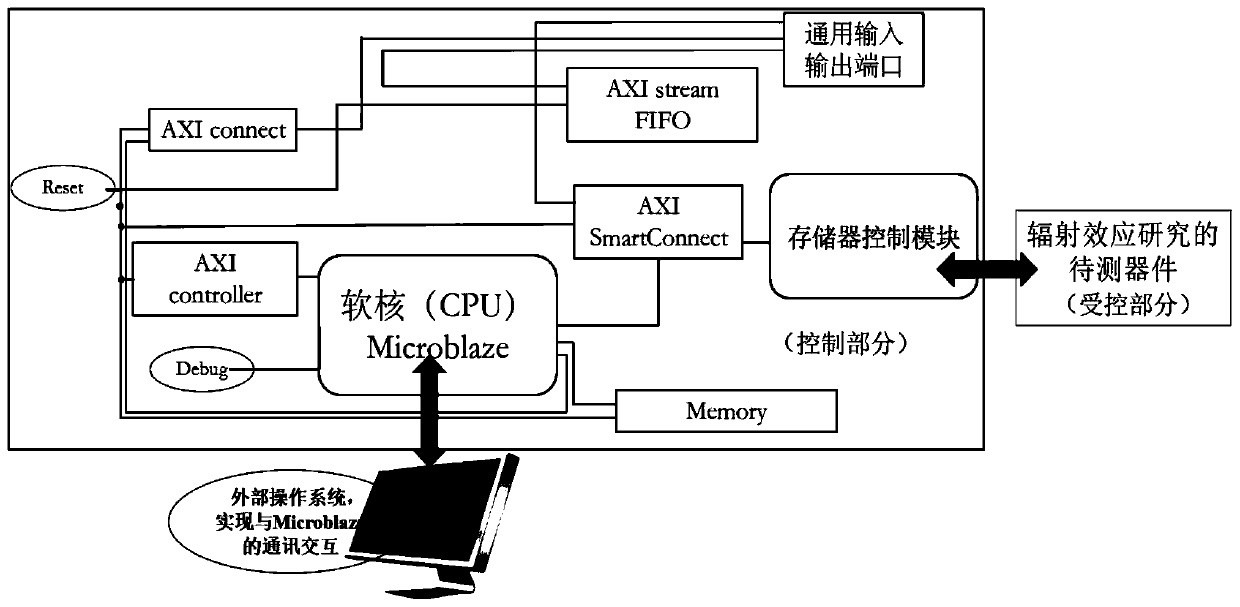

[0061] Such as figure 1 As shown, the development of the DDR4 radiation effect test system to be tested is completed based on the Xilinx Ultrascale+FPGA development board in this embodiment. Through the patented method, the pin configuration, resource location and other information and steps such as read and write operations are obtained. Combined with C code, the writing and comparison of accumulated data is realized on the host computer. It can be effectively used in single event effect experiments in single event irradiation tests.

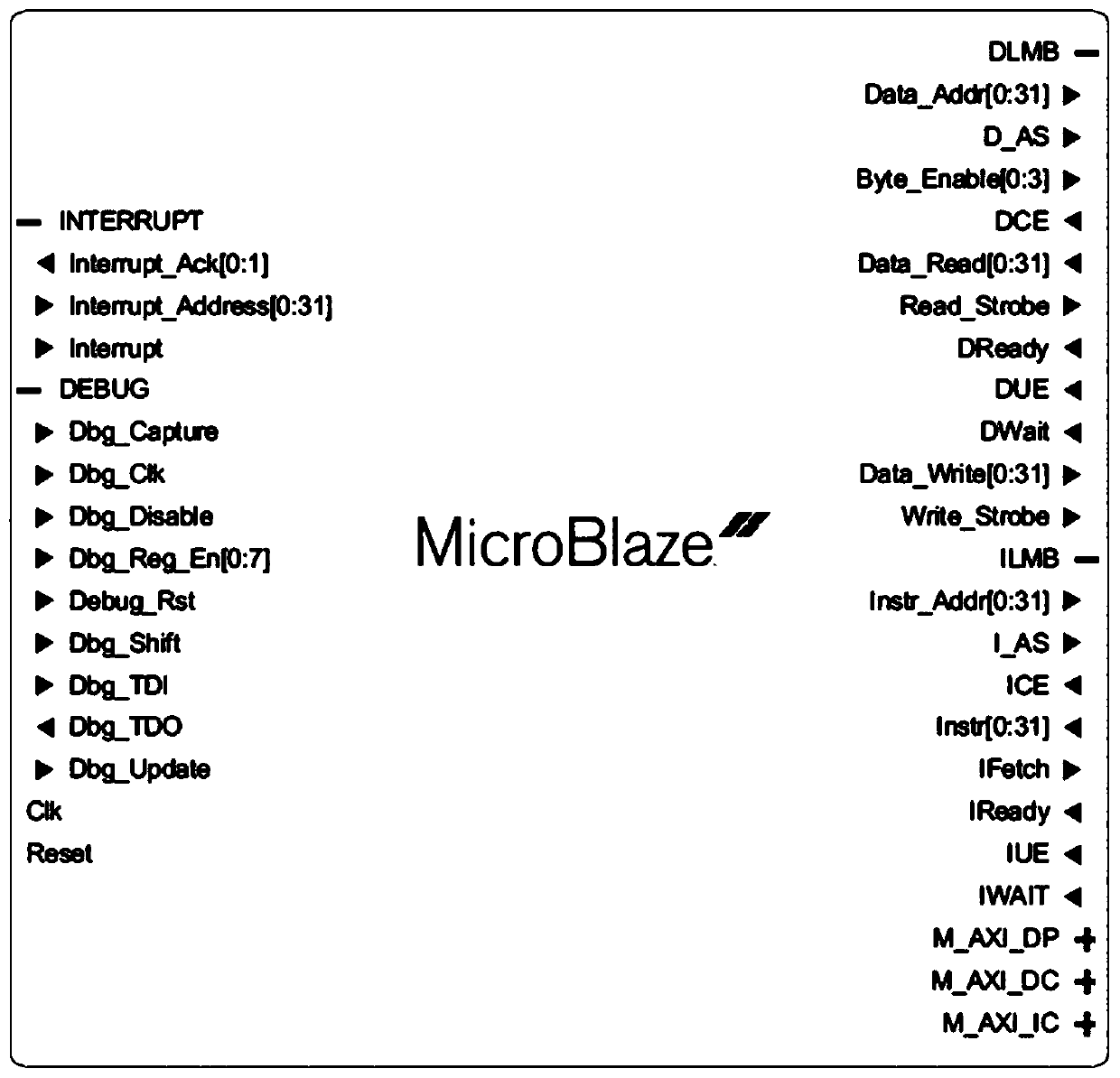

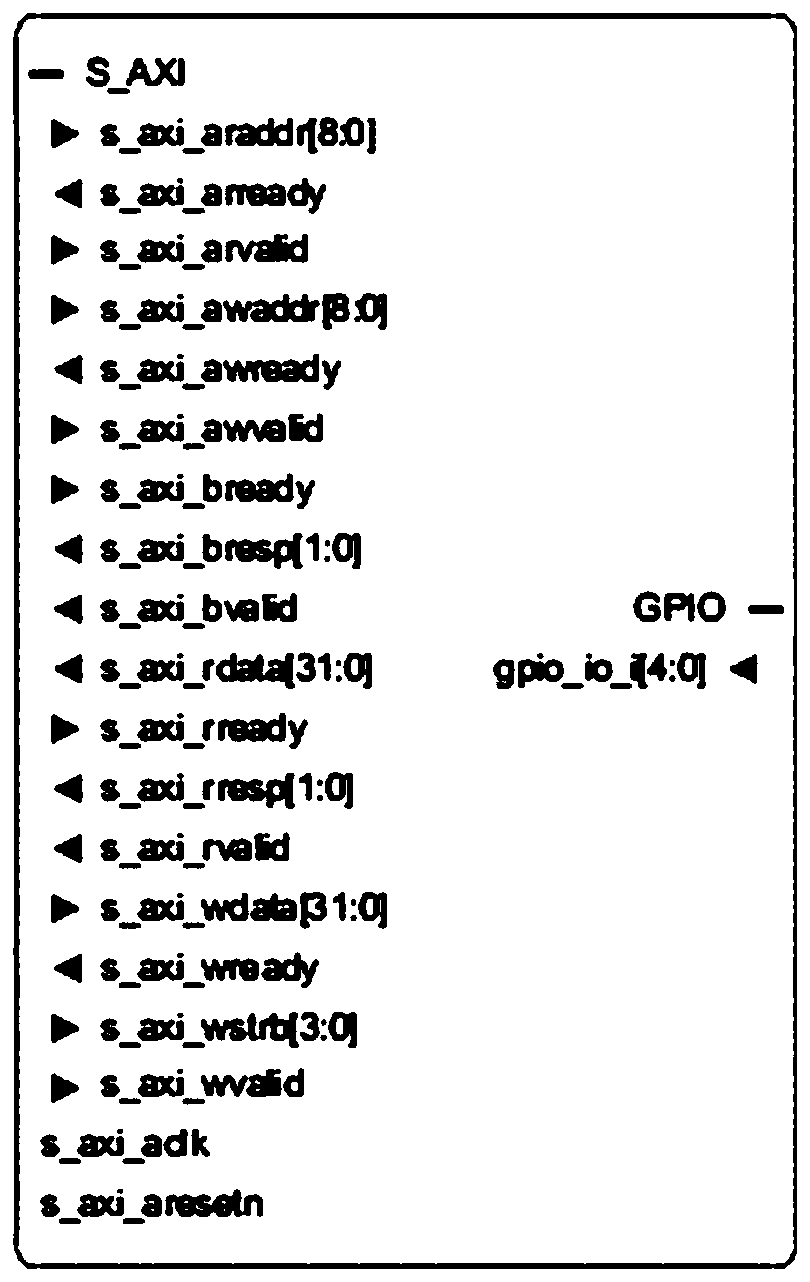

[0062] Such as Figure 4 ~ Figure 7 As shown, it is the development of the DDR4 single event test system based on the Xilinx Ultrascale+FPGA development board.

[0063] Such as Figure 4 As shown, it is the IP type associated with the embedded processor, which is the statistics of the address and other information used to control the resources used by the FPGA in Xilinx's EDK (Embedded Development Kit), and can complete the control of diffe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More