BIST (Built-in Self-test) automatic test circuit and test method aiming at PHY (Physical Layer) high-speed interface circuit

A high-speed interface and automatic test technology, applied in electrical digital data processing, error detection/correction, instruments, etc., can solve problems such as high test cost, complexity, and difficulty in capturing interface output signals, and achieve control of test cost and hardware overhead Effects of smallness, reduced complexity and test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Certain terms are used throughout this document to refer to particular system components. As those skilled in the art will recognize, the same components may often be referred to by different names, and thus this document does not intend to distinguish between those components that differ only in name but not in function. In this document, the terms "including", "comprising" and "having" are used in an open form and should therefore be construed to mean "including but not limited to...".

[0036] The present invention will be further described in detail below in combination with preferred embodiments of the present invention.

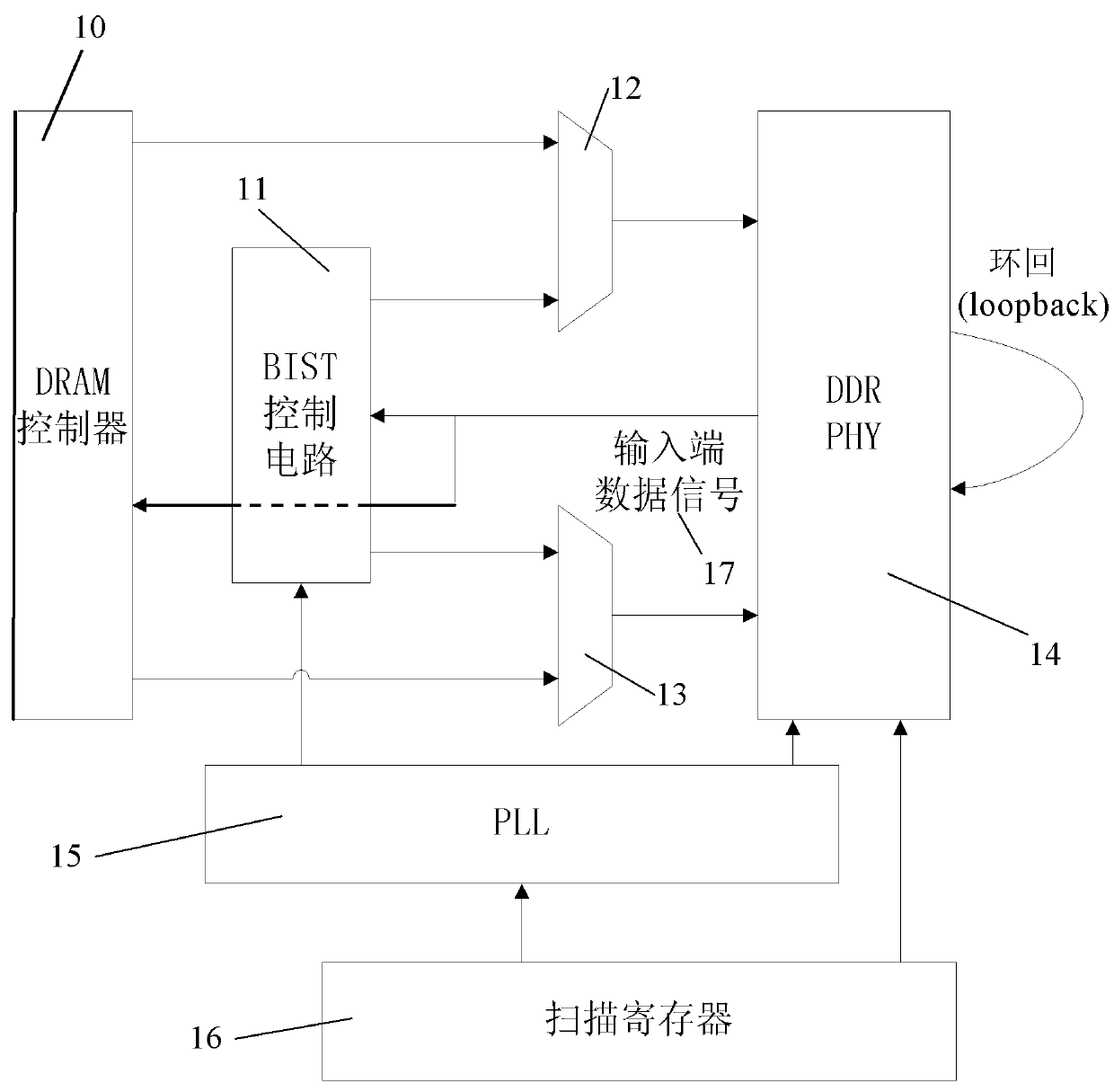

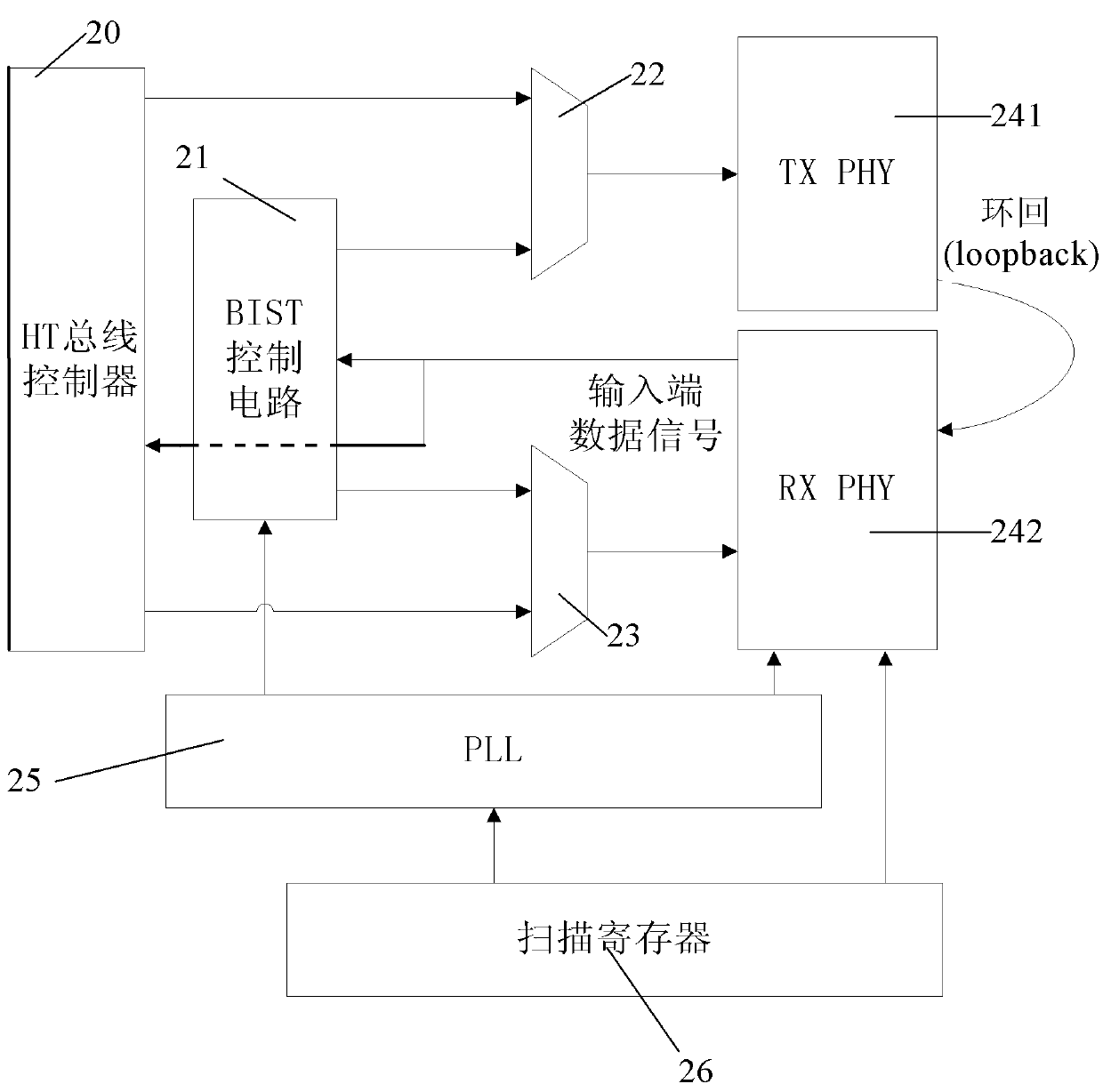

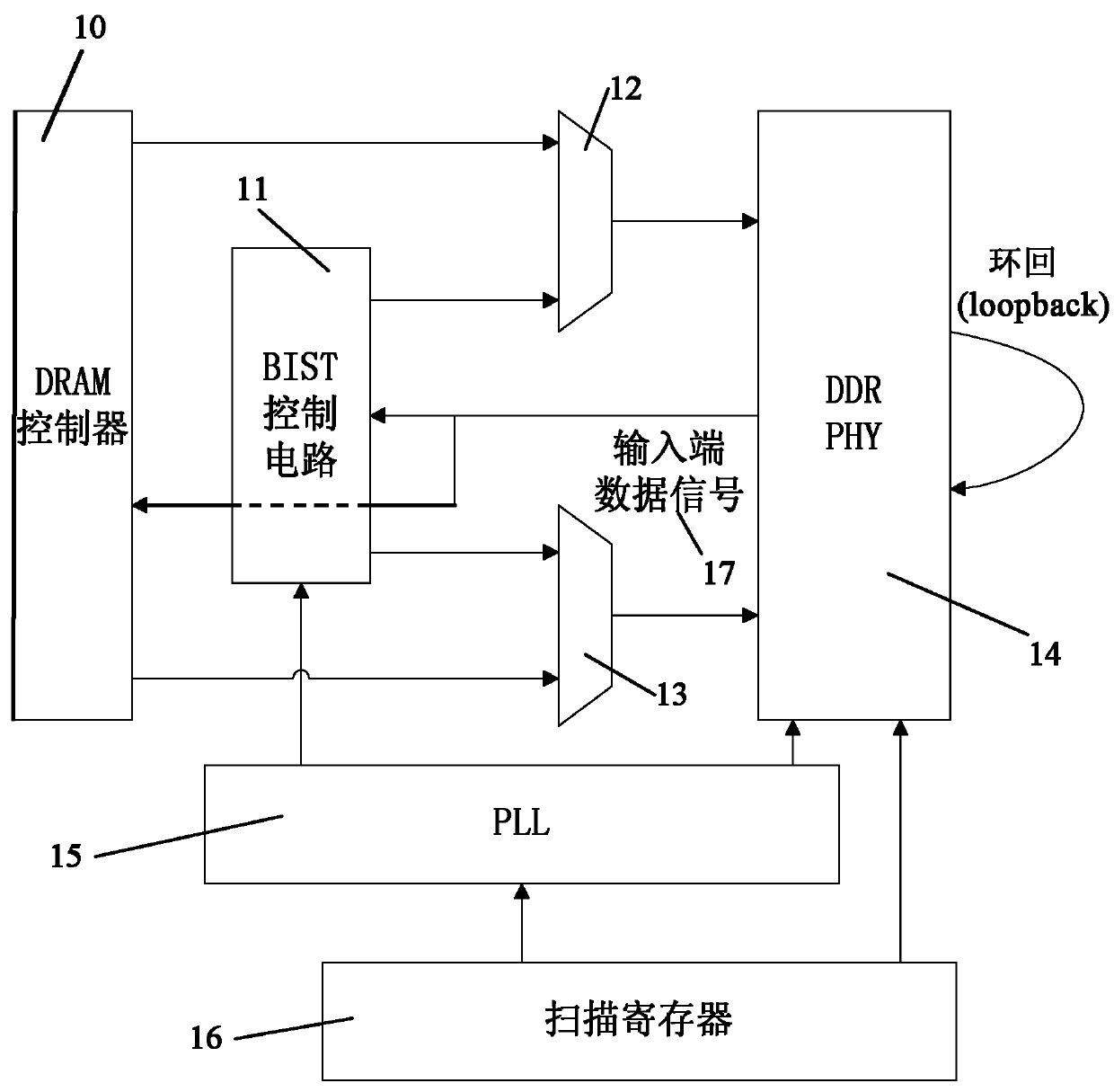

[0037] As mentioned above, the present invention aims to provide a BIST automatic testing circuit and testing method for PHY high-speed interface circuits.

[0038]BIST automatic test is to implant the built-in self-test circuit in the circuit when designing the circuit (that is, integrate the built-in self-test circuit and the functional circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More