Coarse-grained reconfigurable array structure design method based on data flow decoupling

A technology of array structure and design method, applied in the direction of program control design, electrical digital data processing, calculation, etc., can solve the problems that spatial mapping is difficult to resist dynamic delay, performance degradation, and decrease of computing unit utilization, and achieve abstract consistency Hardware Utilization, High Hardware Utilization, Effect of Improved Performance and Resource Utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The following describes several preferred embodiments of the present invention with reference to the accompanying drawings, so as to make the technical content clearer and easier to understand. The present invention can be embodied in many different forms of embodiments, and the protection scope of the present invention is not limited to the embodiments mentioned herein.

[0037] Similar numerals indicate. The size and thickness of each component shown in the drawings are shown arbitrarily, and the present invention does not limit the size and thickness of each component. In order to make the illustration clearer, the thickness of parts is appropriately exaggerated in some places in the drawings.

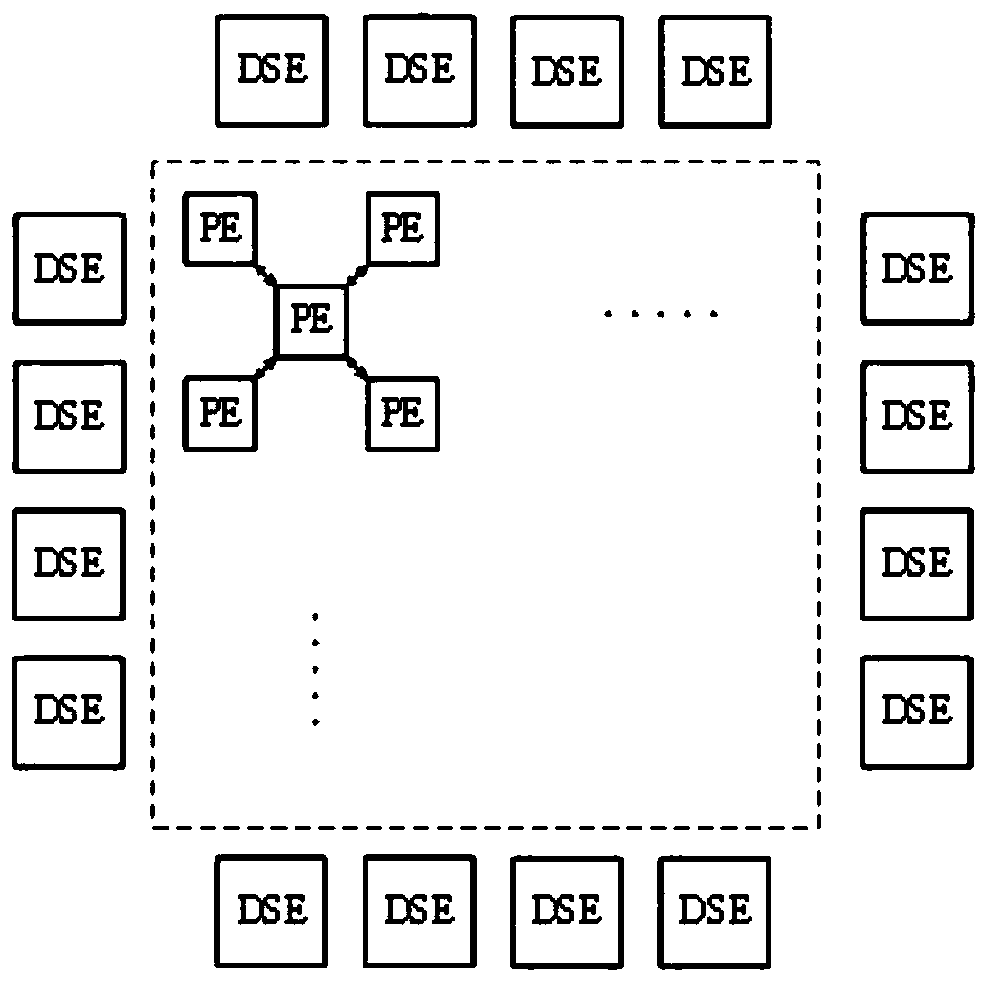

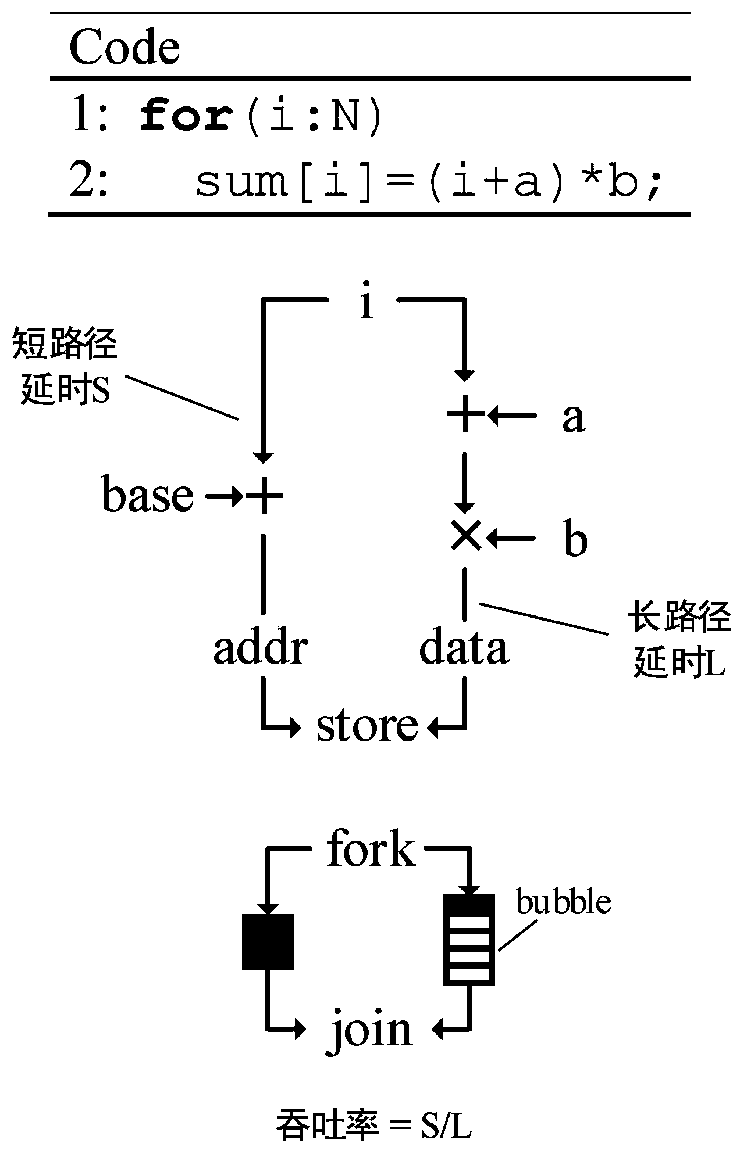

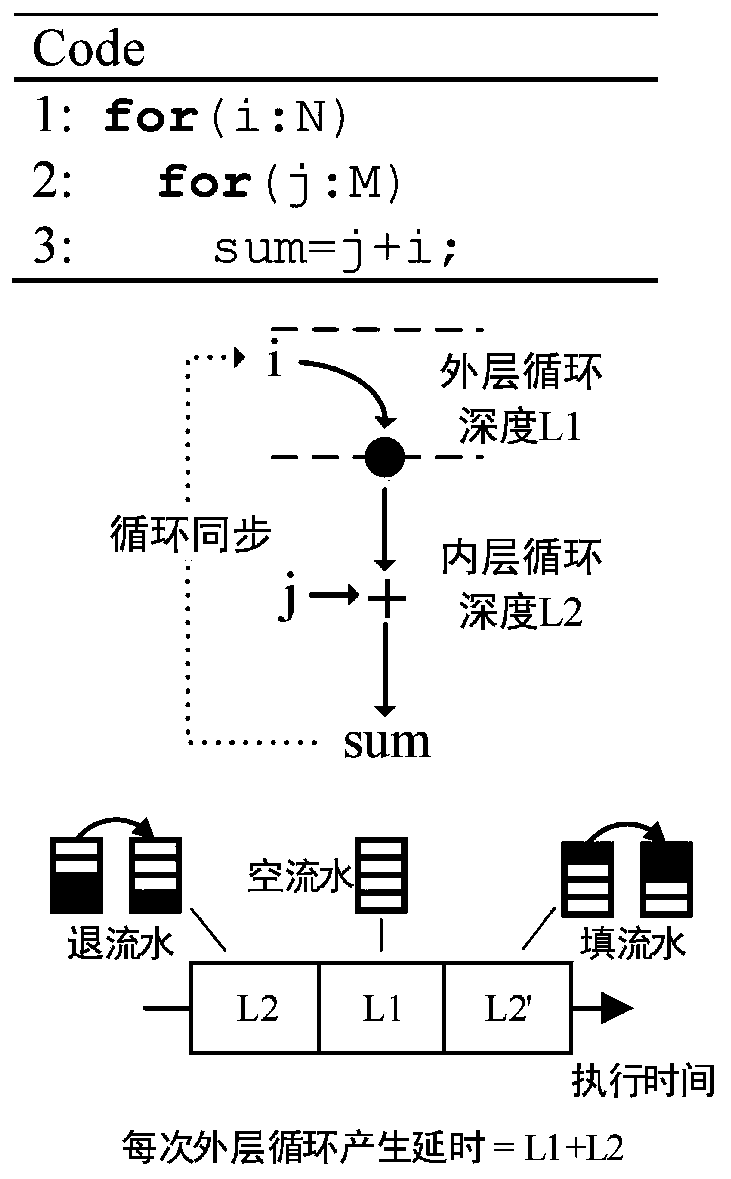

[0038] CGRA uses data flow graph (DFG) as an intermediate product between software code and hardware mapping. Data flow graph can effectively express the dependencies between operations, and can remove non-data-related dependencies to achieve higher parallelism. .

[0039]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More