Multi-board synchronous acquisition circuit and method based on JESD204B

A technology of synchronous acquisition and circuit, applied in the field of signal processing, can solve problems such as difficulties, multi-board multi-chip ADC deterministic delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

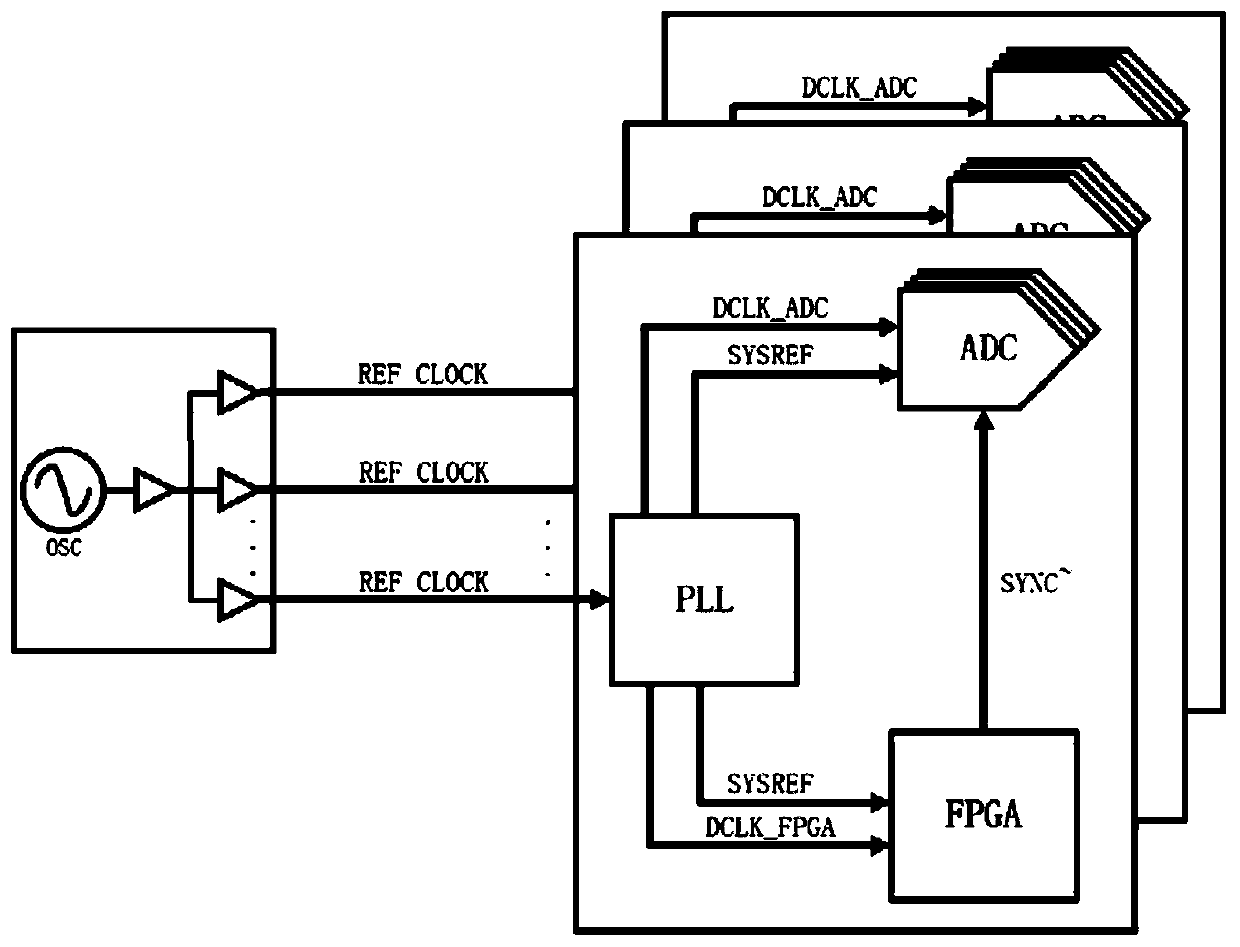

[0016] The embodiment of the present invention provides a multi-board synchronous acquisition circuit based on JESD204B, such as figure 1 As shown, it mainly includes: multiple signal acquisition boards;

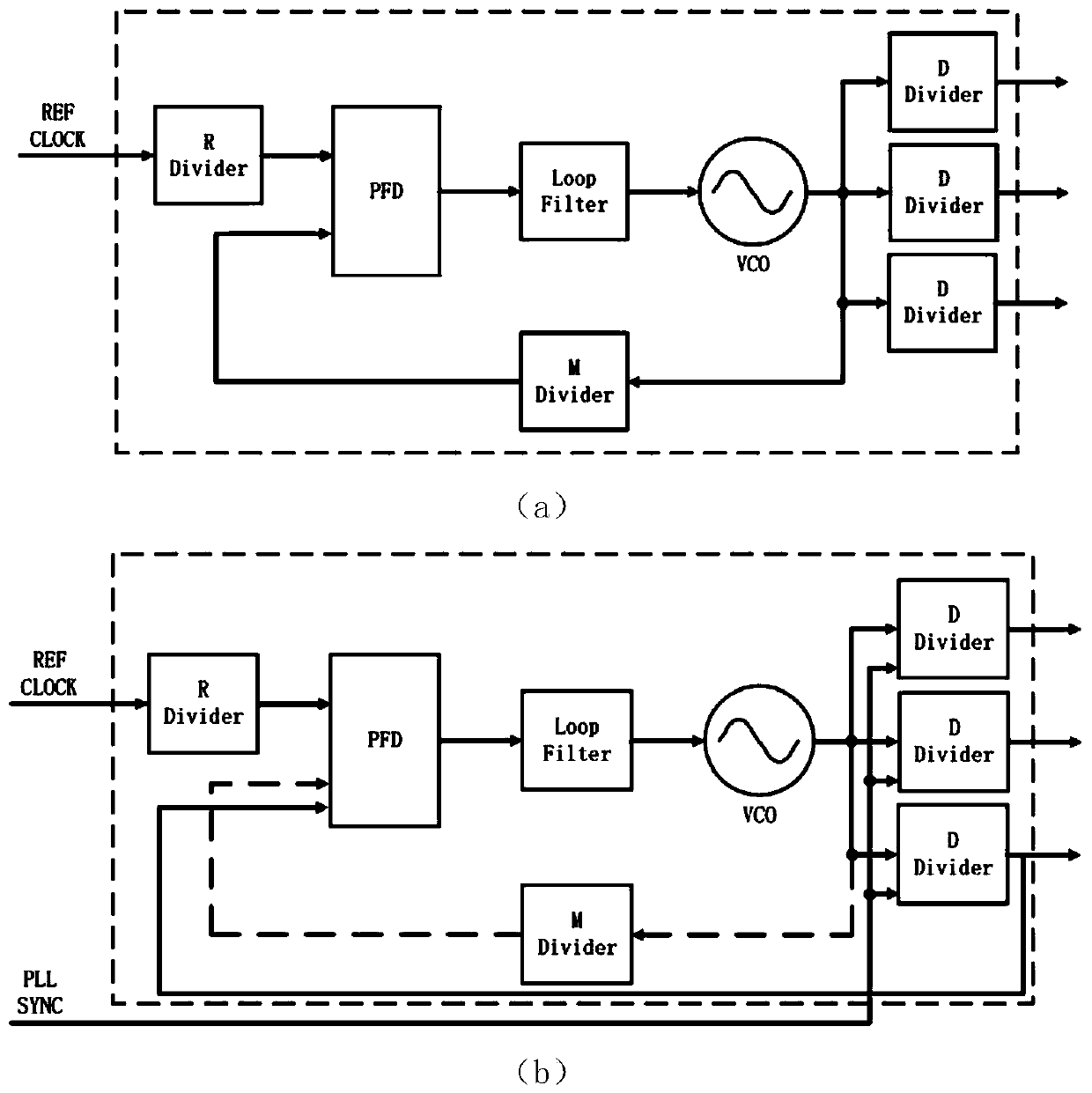

[0017] All signal acquisition boards have the same internal structure, including interconnected PLL modules, FPGA modules, and multiple ADC modules based on the JESD204B protocol; the ADC module is used to receive external analog signals, and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More