Universal FPGA array loading, updating and maintaining system and method

A technology for maintaining systems and arrays, applied in program loading/starting, software deployment, program control design, etc., to solve problems such as inconvenient maintenance, inability to change, program memory redundancy, etc., to achieve power consumption control and reduce hardware costs , to achieve the effect of reuse

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

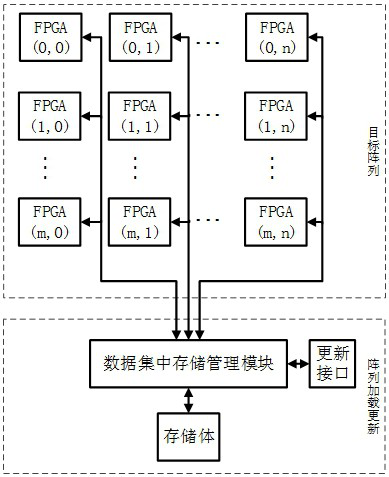

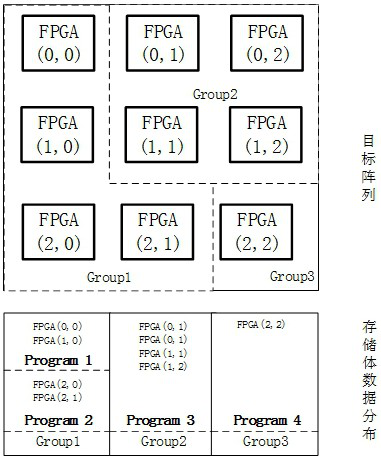

[0055] Such as figure 1 As shown, the overall structure diagram of the general-purpose FPGA array loading update maintenance system provided for this example.

[0056] In this example, the FPGA array loading update maintenance system mainly includes an array loading module, which is connected to the FPGA array.

[0057] The array loading module is specifically connected to the FPGA array through a parallel Flash interface, a serial Flash interface or a SelectMap interface.

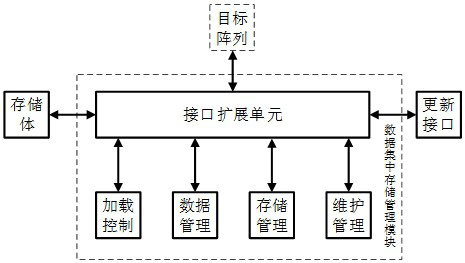

[0058] Specifically, the array loading module includes: an update interface, a centralized data storage management module connected to the update interface, and a storage body connected to the centralized data storage management module. The centralized data storage management module is connected to the FPGA array.

[0059] The memory banks are used to store program load data for the FPGA array.

[0060] The update interface is used to connect with the outside to obtain program update data from the outsi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More