fpga device with adjustable power-on reset signal waveform

A reset signal and signal waveform technology, applied in the FPGA field, can solve the problems of not being able to reach the working voltage immediately, poor flexibility, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

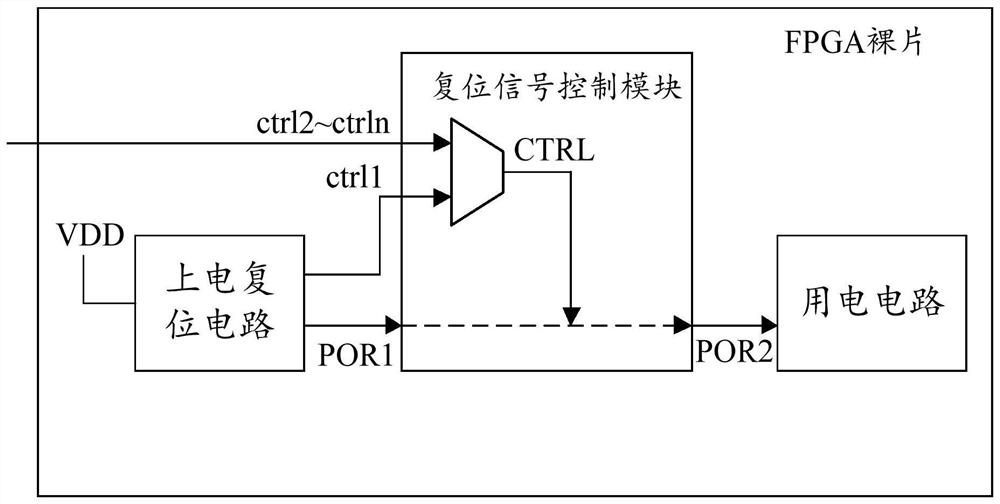

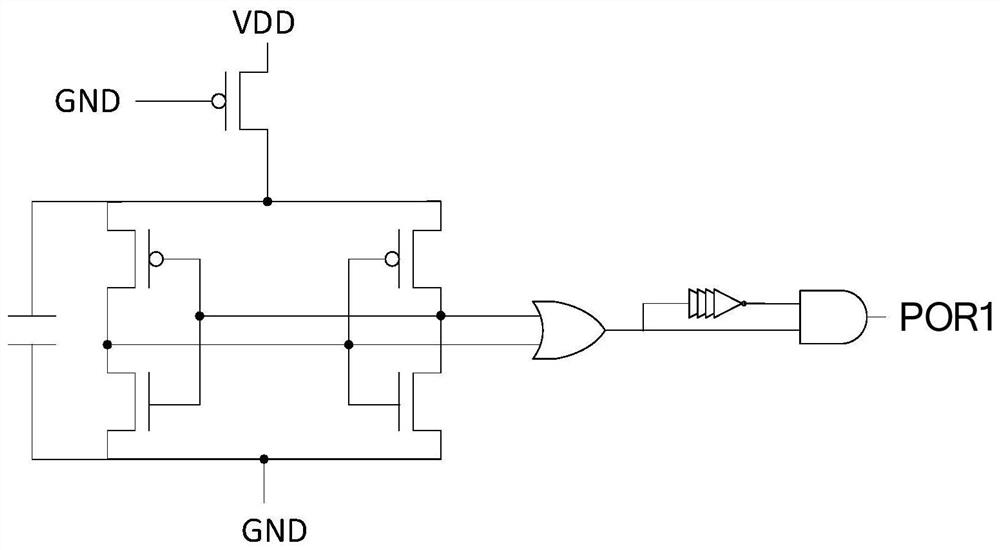

[0018] The present application discloses an FPGA device having a power-up reset signal waveform adjustable function including an FPGA die, please refer to figure 1 The FPGA dies include a power-on reset circuit, an electric circuit, and a reset signal control module. The input terminal of the power-on reset circuit is connected to the power supply VDD. The output is output, the first upper voltage reciprocating pulse signal POR1, the power-on reset circuit detectable The power-on-electric power supply of the internal power supply VDD and outputs the first upper voltage reciprocating pulse signal POR1 to reset restart and other power-on, the power-on reset circuit is an existing conventional circuit, and its specific circuit structure can be refer to figure 2 This application is not described in detail. The input of the reset signal control module connects the output of the power reset circuit and acquires the first upper v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More