Method for eliminating current overshoot and switching circuit

A switching circuit and current technology, applied in the method and switching circuit to eliminate the current overshoot field, can solve the problems of system reliability damage, current overshoot, etc., so as to reduce the output current overshoot phenomenon, reduce the damage, and eliminate the current overshoot. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

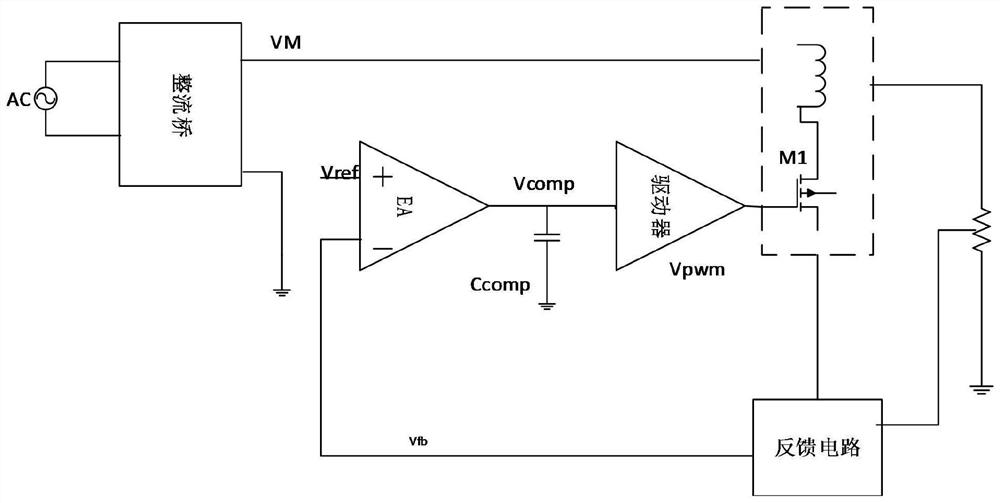

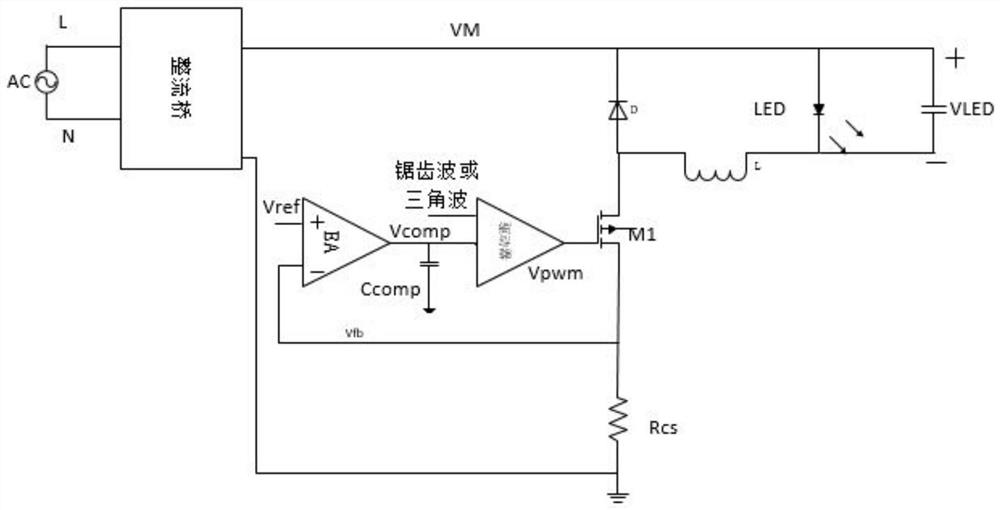

Method used

Image

Examples

Embodiment 1

[0047] Such as Figure 5 , a method for eliminating current overshoot provided by the present invention comprises the following steps:

[0048] Determine whether the system enters the power-down state;

[0049] When the system enters the power-off state, the power-off protection device is activated, and the power-off timer starts to record the power-off time;

[0050] When the power-off time reaches a preset time, the integrator stops integrating, wherein the preset time is longer than the cycle time of the bus voltage VM.

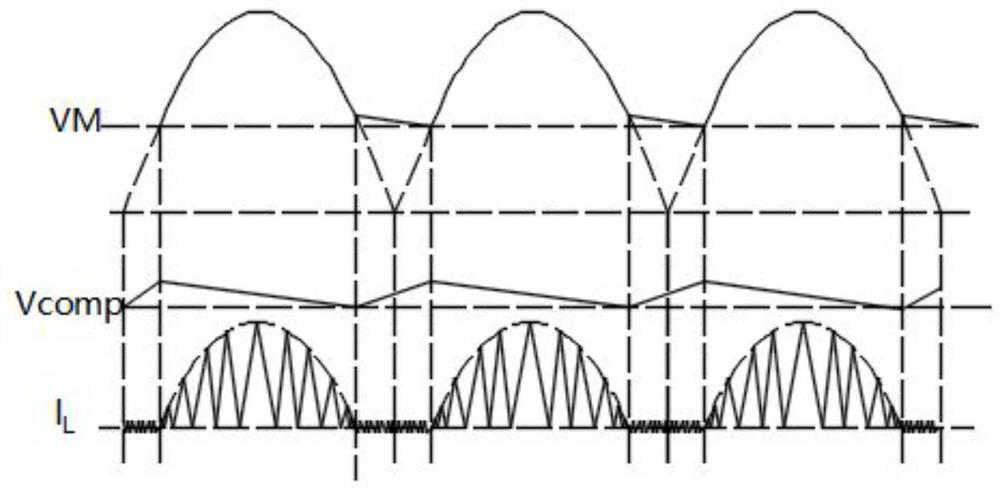

[0051]Due to the power-off, the bus voltage drops, which makes the voltage of the sampling resistor drop, which in turn causes V ref and V fb As the difference increases, the integrator produces an error signal V comp will increase, causing the driver to generate a PWM signal that exceeds the steady-state value, and the output current I L Increasing the current beyond the steady state creates an overshoot.

[0052] Therefore, in this embodiment, the ...

Embodiment 2

[0059] Such as Figure 7 As shown, a method for eliminating current overshoot includes the following steps:

[0060] Get bus voltage parameters, when the bus voltage is less than the power-off threshold voltage, and the bus voltage continues to drop (such as Figure 6 As shown), at this time, it is determined that the system has entered a power-off state.

[0061] Start the power-down protection device, and the power-down timer starts to record the power-down time;

[0062] When the power-off time reaches a preset time, the integrator stops integrating, wherein the preset time is longer than the cycle time of the bus voltage VM.

[0063] Due to the power-off, the bus voltage drops, which makes the voltage of the sampling resistor drop, which in turn causes V ref and V fb As the difference increases, the integrator produces an error signal V comp will increase, causing the driver to generate a PWM signal that exceeds the steady-state value, and the output current I L Incr...

Embodiment 3

[0068] Such as Figure 8 As shown, a method for eliminating current overshoot includes the following steps:

[0069] Obtain the electrical parameter of the sampling resistor. When the electrical parameter of the sampling resistor is less than the threshold and continues to drop, it is determined that the system has entered a power-off state. The electrical parameters of the sampling resistor include current or voltage of the sampling resistor.

[0070] Start the power-down protection device, and the power-down timer starts to record the power-down time;

[0071] When the power-off time reaches a preset time, the integrator stops integrating, wherein the preset time is longer than the cycle time of the bus voltage VM.

[0072] Due to the power-off, the bus voltage drops, which makes the voltage of the sampling resistor drop, which in turn causes V ref and V fb As the difference increases, the integrator produces an error signal V comp will increase, causing the driver to g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com