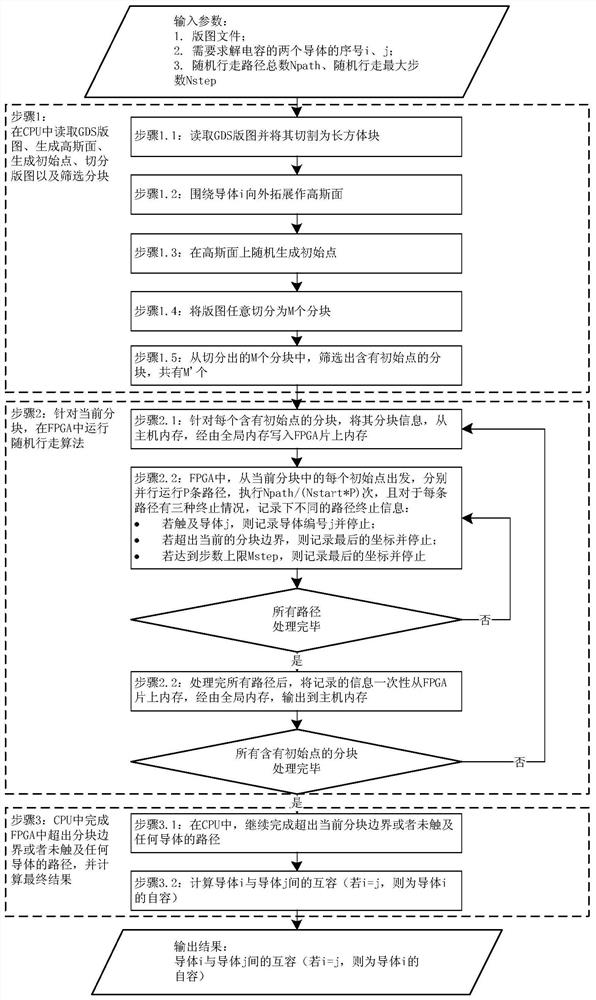

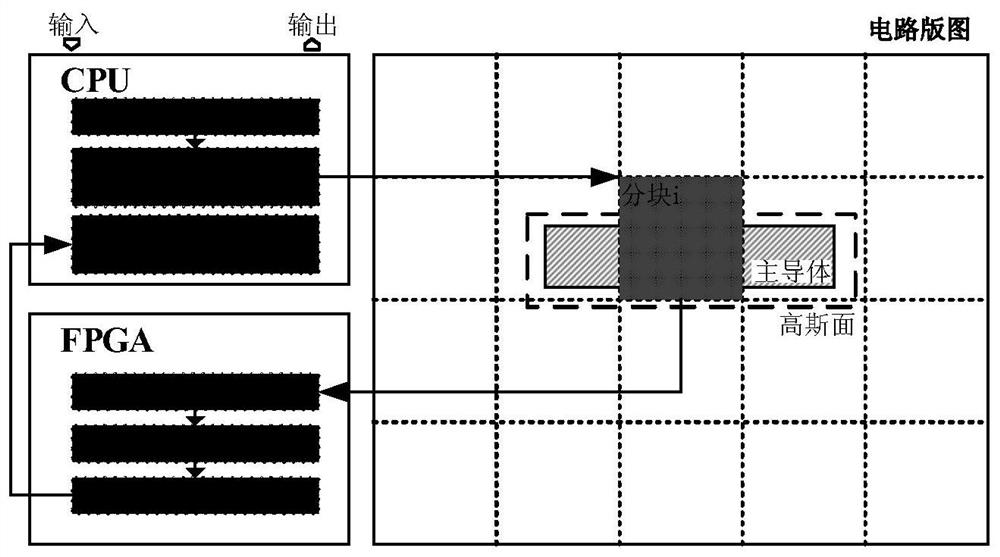

Random walk parasitic capacitance parameter extraction method based on FPGA and CPU heterogeneous calculation

A random walk algorithm and random walk technology, applied in computer, computer-aided design, digital computer components, etc., can solve problems such as limited FPGA chip resources and weak circuit control capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0142] Through the implementation process of specific examples, the method of the present invention is further described.

[0143] In the random walk capacitance parameter extraction algorithm of the present invention, the FPGA-CPU heterogeneous computing platform uses an AWS (Amazon Web Services) EC2F1 instance, wherein the CPU is an Intel Xeon E5-2686 8-core processor with a main frequency of 2.3GHz and a memory of 122GB , The FPGA development board is equipped with Xilinx Virtex UltraScale+VU9P FPGA and 64GB onboard memory. At the same time, the FPGA development tool is Xilinx SDAccel tool version 2017.1, using 32-bit floating point numbers.

[0144] Implementation example 1

[0145] This example uses the Figure 10 The circuit shown is similar to the examples used in [11], [12].

[0146] This calculation example includes three layers of 41 conductors, including 3 conductors in M2 layer, 19 conductors in M1 and M3 respectively. In this calculation example, the conductor s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com