Image compression hardware accelerator device based on convolution automatic coding algorithm

A hardware accelerator and image compression technology, applied in image communication, electrical components, digital video signal modification, etc., can solve the problems of computing power constraints, image reconstruction quality cannot be improved to the maximum extent, single compression method, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Further description will be made below in conjunction with the accompanying drawings and the specific implementation of the present invention. Where the same name is used throughout to refer to modules with the same or similar functionality. The present device will be specifically described below by referring to the implementation examples described with reference to the accompanying drawings. The implementation example selects an image with a resolution of 4K (3840*2160) and utilizes the periodic parallel convolution acceleration capability of the device to process the compression task, which is intended to explain the present invention, but should not be construed as a limitation of the present invention.

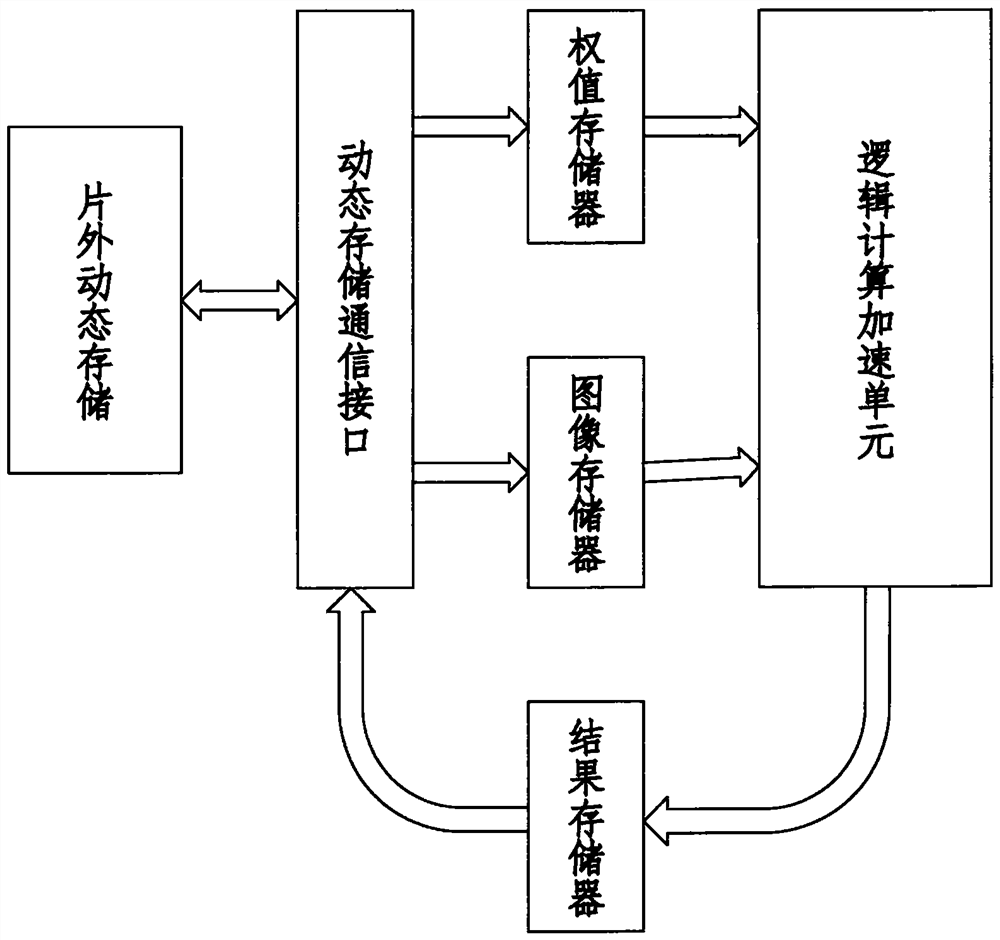

[0017] Such as figure 1 Shown is the top-level hardware architecture diagram of the device of the present invention. The image compression hardware accelerator device based on the convolutional auto-encoding algorithm includes:

[0018] 1. Control unit: responsi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com