Patents

Literature

115results about How to "The acceleration effect is obvious" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

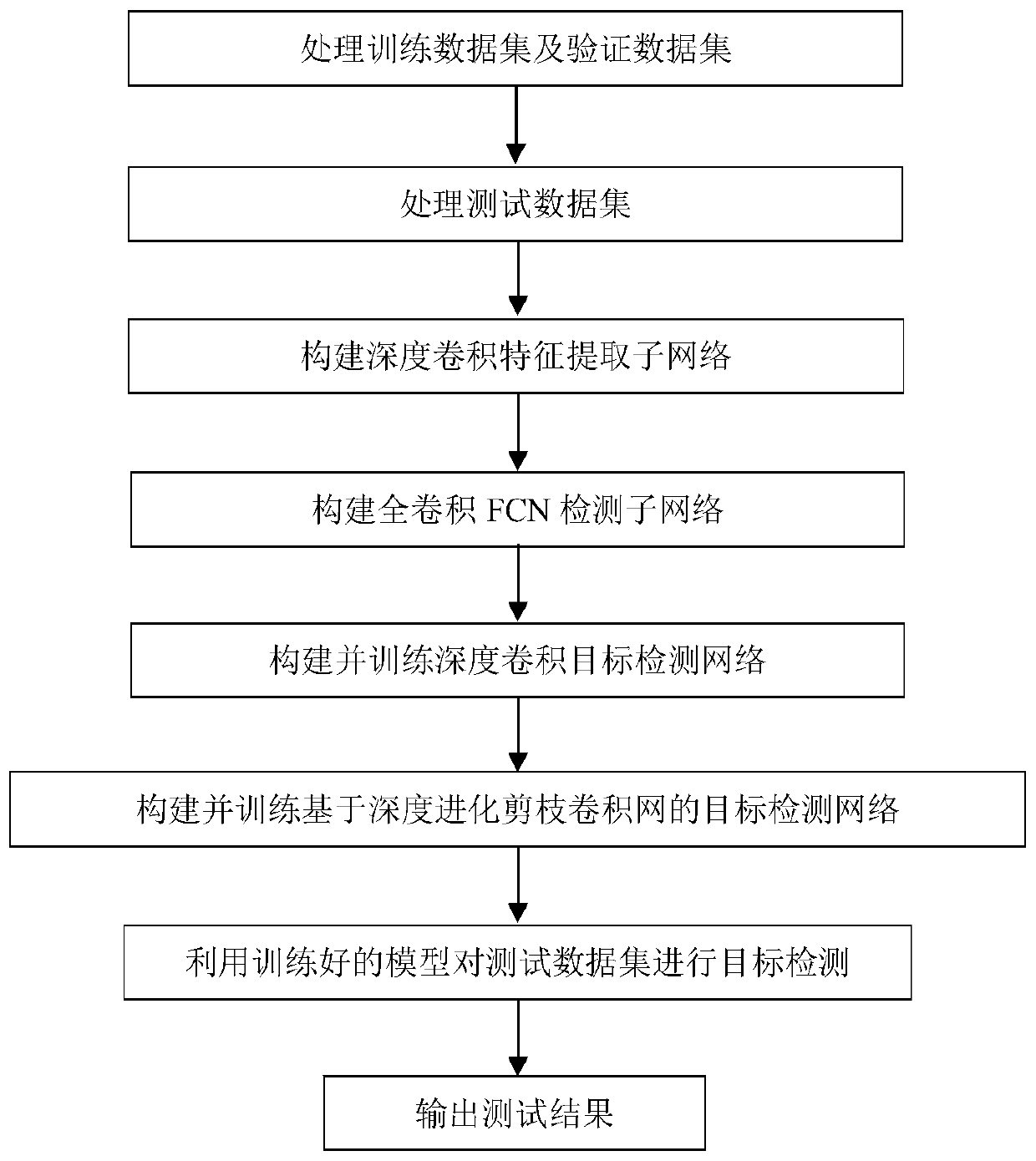

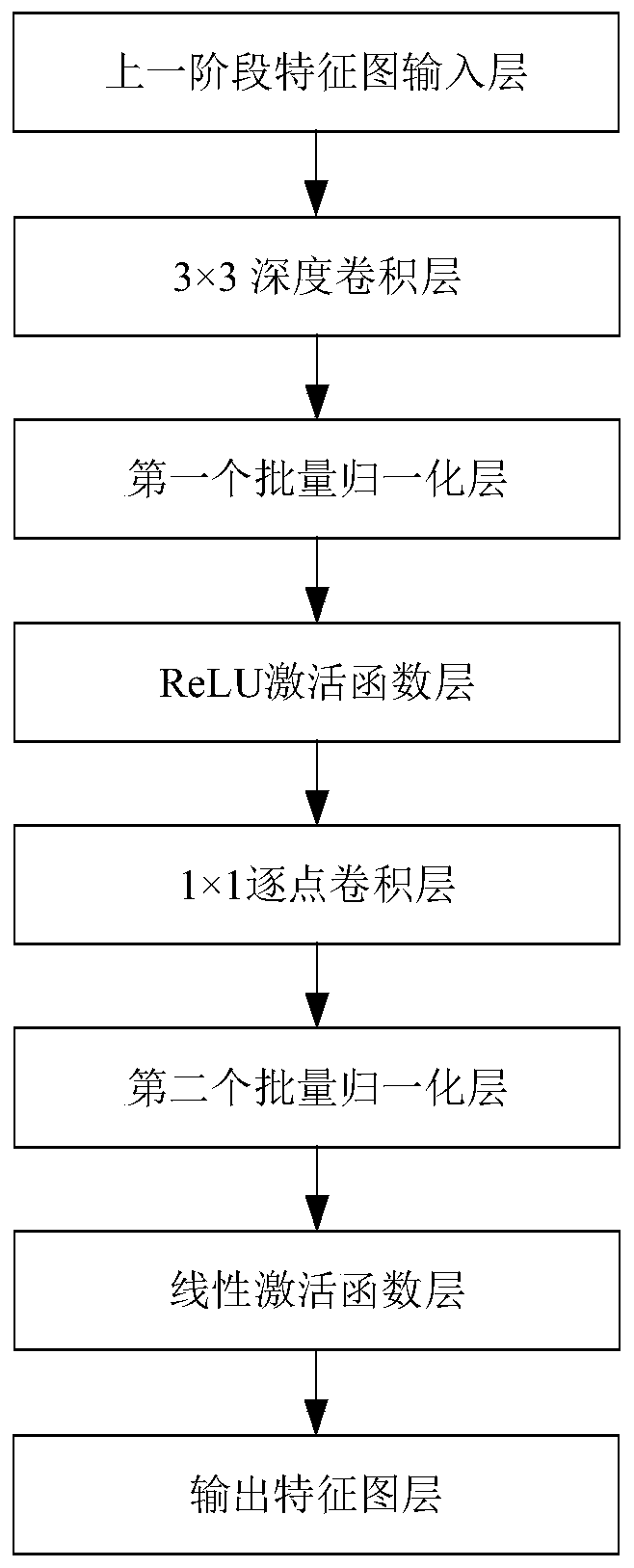

Remote sensing image target detection method based on deep evolution pruning convolutional network

ActiveCN110532859AGuaranteed detection accuracyAvoid destructionScene recognitionNeural architecturesFeature extractionData set

The invention discloses a remote sensing image target detection method based on a deep evolution pruning convolutional network. The problem that the detection speed and the detection precision are notglobally and effectively optimized at the same time in existing remote sensing image target detection is solved. The method comprises the specific steps of processing a data set; constructing a deepconvolution feature extraction subnet; constructing a full convolution FCN detection subnet; constructing and training a deep convolution target detection network; constructing and training a target detection network based on a deep evolution pruning convolutional network; performing target detection on the test data set by using the trained model; and outputting test results. According to the method, a reverse residual structure is constructed by using depth separable convolution, so that the model parameter quantity is greatly reduced while the detection precision is high; the target detection network is combined with evolutionary pruning to realize global acceleration. The method greatly reduces the calculation amount, remarkably improves the target detection speed, is high in detectionprecision, and is used for the quick and accurate detection of small targets in a remote sensing image, such as an airplane and a ship.

Owner:XIDIAN UNIV

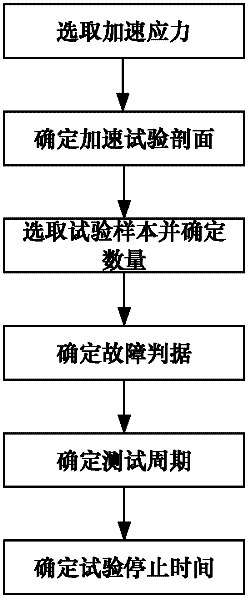

Combined stress acceleration life test method of spaceflight drive assembly

The invention, which belongs to the spaceflight drive assembly reliability and life evaluation field, relates to a combined stress acceleration life test method of a spaceflight drive assembly. According to the method, an acceleration stress is selected; an acceleration testing profile is determined and as a result, a combined stress acceleration life testing profile is employed; testing samples are selected and the number of samples is determined; fault determination and a testing period are determined; testing stop time is determined; and according to data obtained by the above-mentioned testing process, a life characteristic value of the spaceflight drive assembly is evaluated. According to the method, a combined stress is employed to carry out acceleration life testing and an acceleration effect is obvious; therefore, rapid evaluation on reliability and life of the spaceflight drive assembly is realized.

Owner:BEIHANG UNIV

BGA position back bore manufacture method

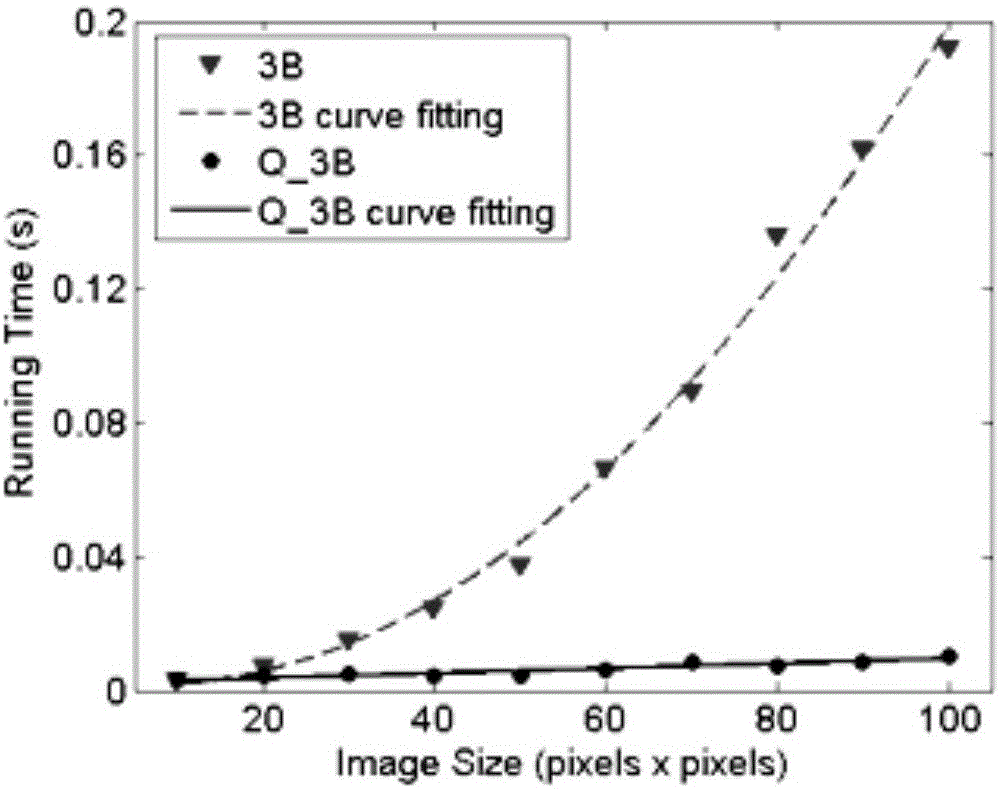

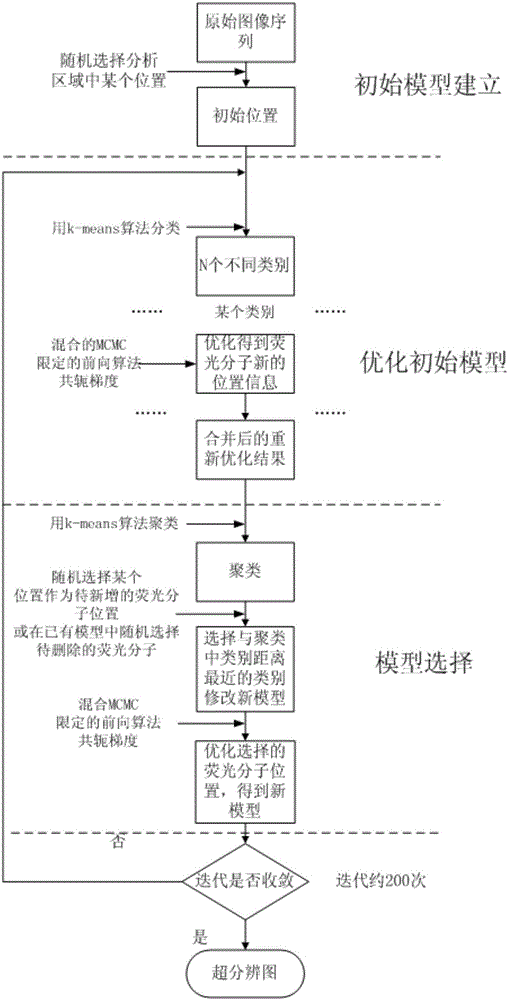

ActiveCN106023121AImprove time resolutionHigh positioning accuracyImage enhancementImage analysisImage resolutionMechanical engineering

The invention discloses a BGA position back bore manufacture method. According to the invention, a back bore process is optimized; the problem of debris adhesion in the bore wall due to the high temperature during back bore processing is effectively avoided; a back bore is prevented from bad contact, short circuit and the like; the accuracy of back bore processing is improved; and the quality of a manufactured PCB is effectively improved.

Owner:INSITUTE OF BIOPHYSICS CHINESE ACADEMY OF SCIENCES +1

Quick reconstruction method of double-camera spectral imaging system based on GPU

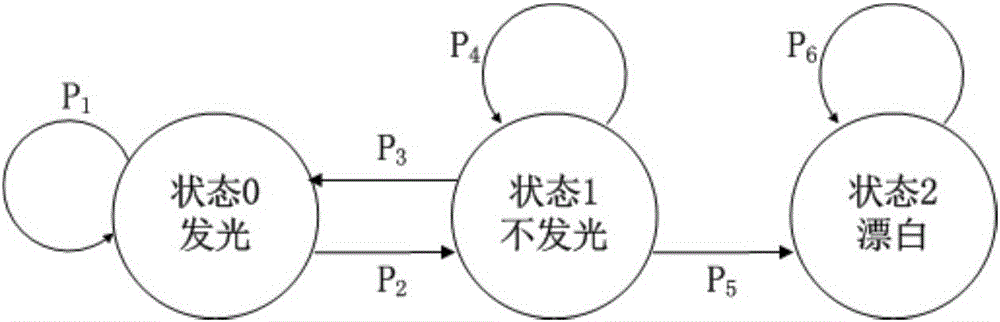

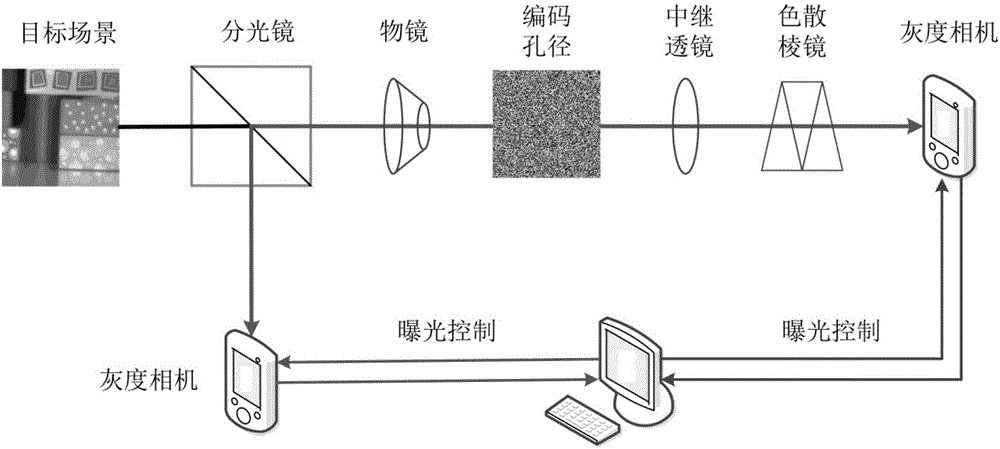

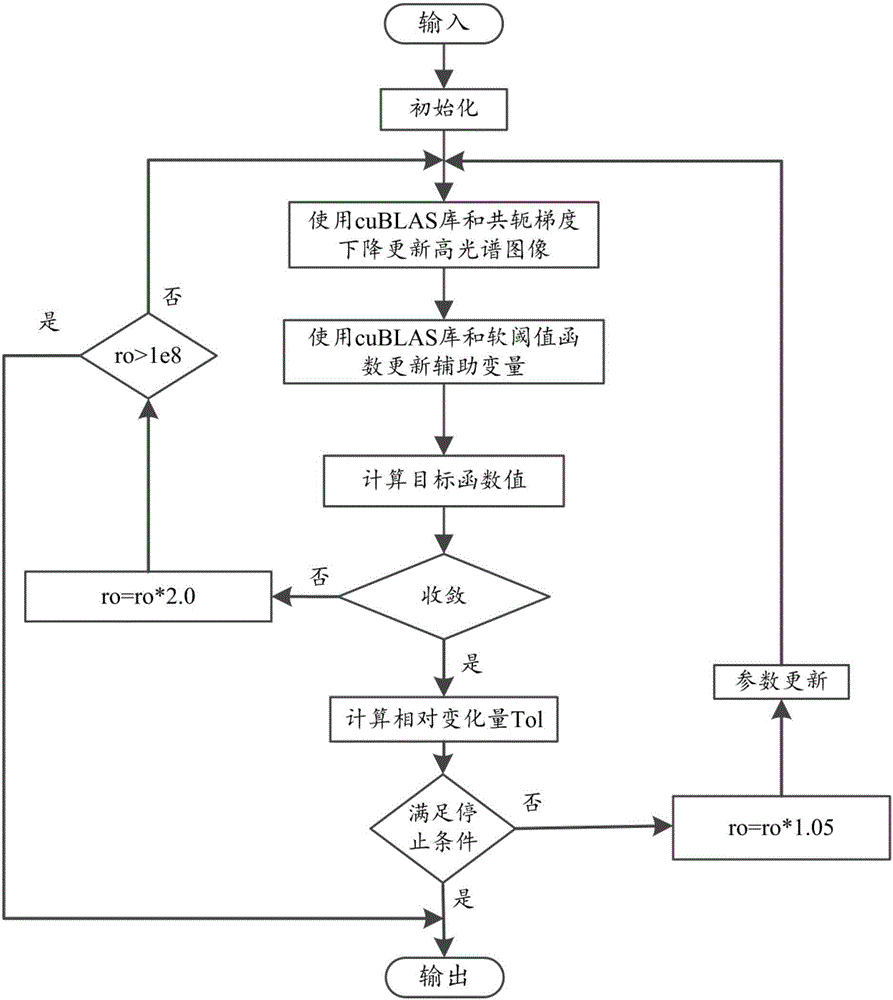

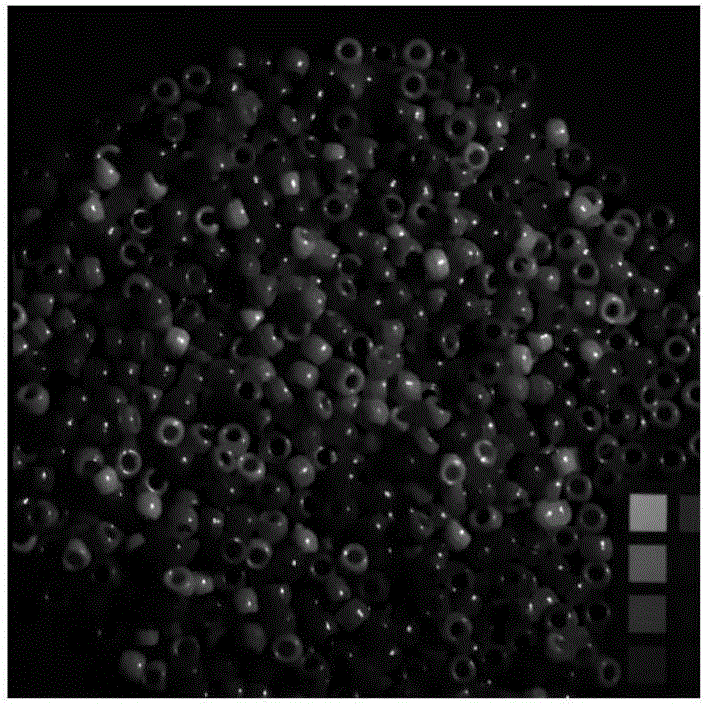

InactiveCN107525588AFast convergenceImprove efficiencySpectrum investigationReconstruction methodGeological exploration

The invention discloses a quick reconstruction method of a double-camera spectral imaging system based on a GPU, and relates to a method which can quickly acquire a high-resolution hyperspectral image, wherein the method relates to the field of computational photography. The method is applied on a double-camera spectral imaging system based on coded aperture snapshot spectral imaging and a gray-scale camera. A hyperspectral image reconstruction problem is converted to a plurality of sub optimization problems, and furthermore a GPU is utilized for finishing solving of each sub problem. A cuBLAS database and a conjugate gradient reduction method are utilized for updating the hyperspectral image. A soft-threshold function is utilized for updating an auxiliary variable. Iteration is performed for finishing reconstruction of the hyperspectral image. The method of the invention can realize high-quality hyperspectral image reconstruction of the double-camera spectral imaging system and furthermore has advantages of ensuring high spatial resolution and high spectral fidelity of a reconstruction result, greatly improving reconstruction efficiency of the hyperspectral image, and expanding application range of the hyperspectral image. The quick reconstruction method can be used in a plurality of fields of manned space flight, geological exploration, vegetation studying, etc.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Geometric correction and disparity extraction device of binocular camera

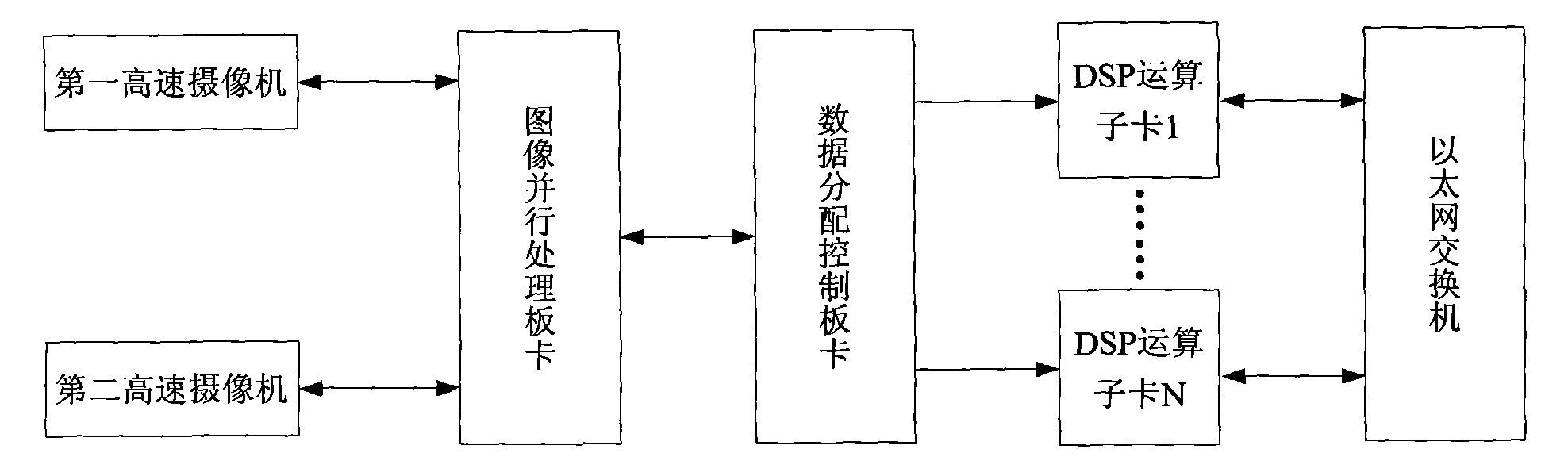

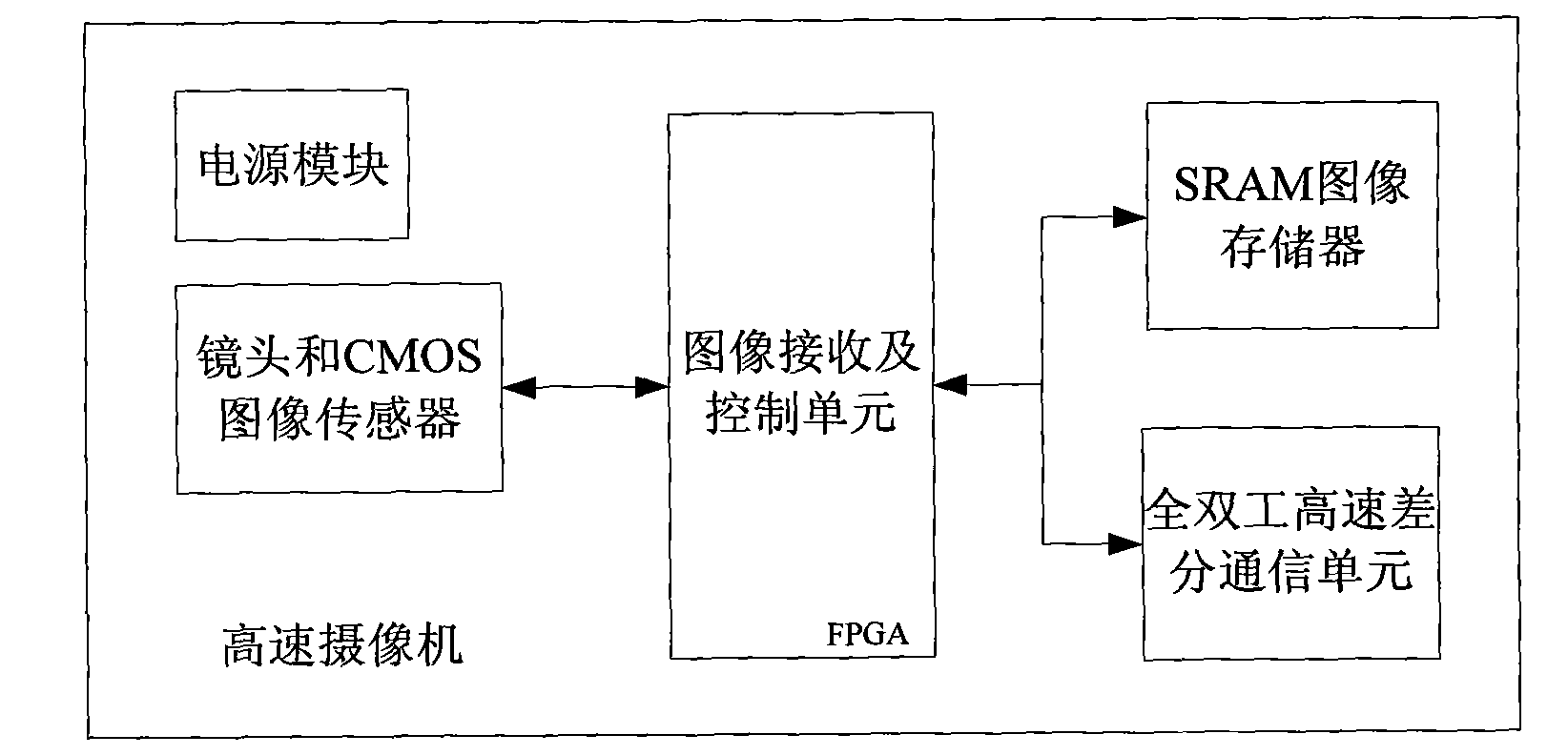

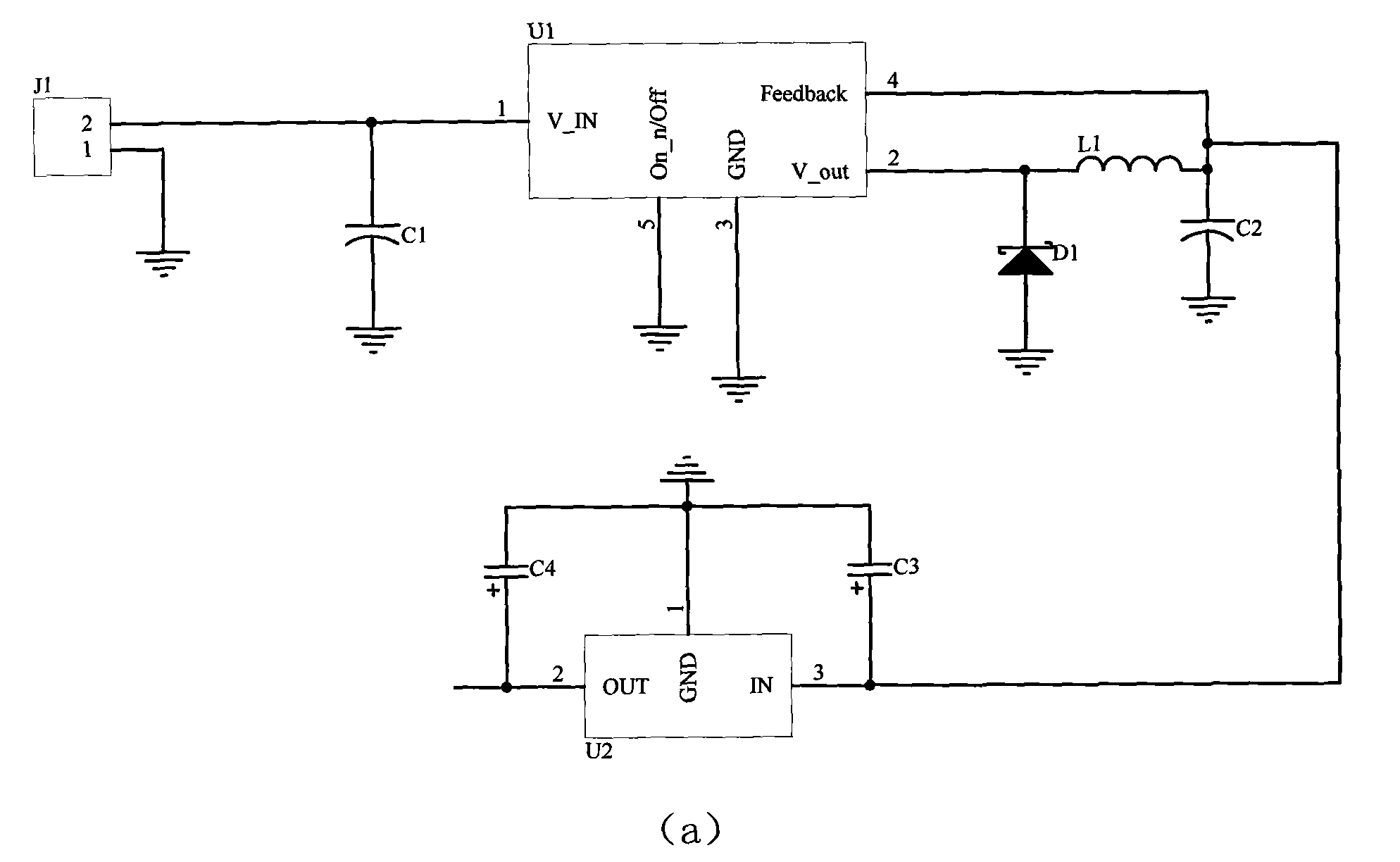

InactiveCN101916429AGive full play to one's own advantagesFast operationTelevision system detailsColor television detailsDigital signal processingDistribution control

The invention discloses a geometric correction and disparity extraction device of a binocular camera, which comprises two high-speed cameras, an image parallel processing board, a data distribution control board, a plurality of DSP (Digital Signal Processing) operation daughter cards and an Ethernet switch. Images acquired by the high-speed cameras are transmitted to the image parallel processing board for real-time geometric correction, the results are distributed to the data distribution control board and one group of DSP operation daughter cards for real-time processing, and the processing results are summarized by the Ethernet switch and transmitted to receiving equipment. Different disparity extraction methods and the advanced application of binocular stereoscopic vision are realized by updating software on the DSP operation daughter cards. The invention has the advantages of high processing speed, strong real-time performance, small size, low power consumption, strong extendibility and strong flexibility; the cameras have adjustable base distance and convenient onsite debugging; and the processing process of the DSP operation daughter cards can be changed through the Ethernet or a USB flash drive.

Owner:ZHEJIANG UNIV

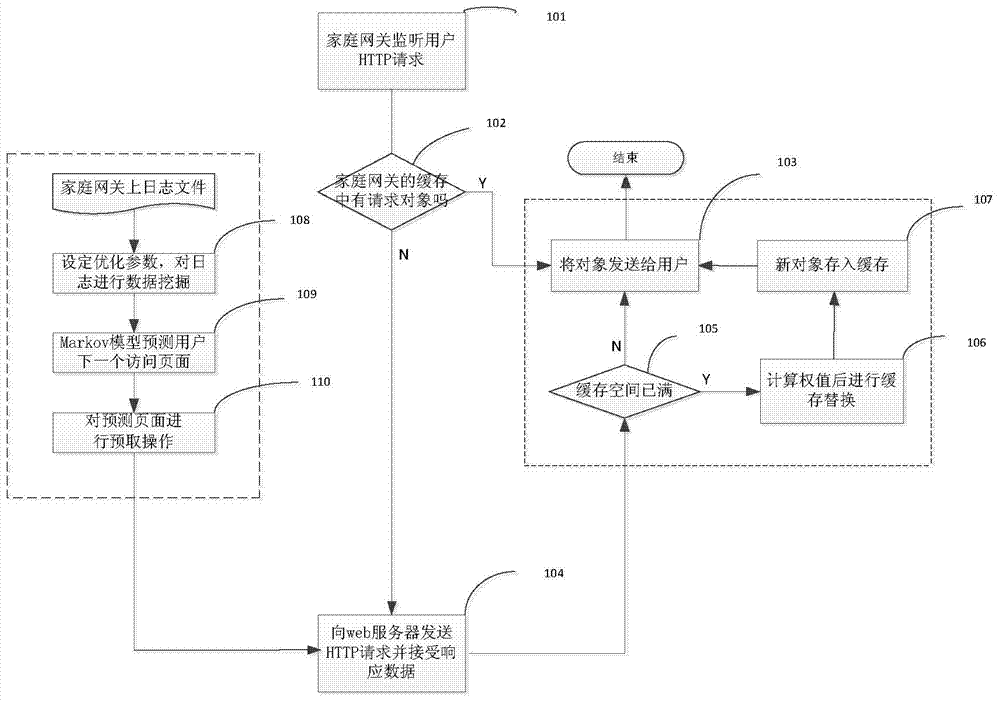

Webpage browsing accelerating method based on home gateway

The invention provides a webpage browsing accelerating method based on a home gateway. The webpage browsing accelerating method includes the steps that the home gateway is used for monitoring an HTTP request from a user and determining whether a response message corresponding to the request exists in a cache or not through searching, if the response message corresponding to the request does not exist in the cache, the home gateway forwards the HTTP request to a WEB server and receives a response from the WEB server, a response copy is copied into the cache of the home gateway, if the space of the cache is enough, the response copy is directly stored in the cache, if the space of the cache is not enough, weights are calculated, the smaller weights are replaced by the response copy in the cache space, data mining is conducted on logs at regular intervals through an optimized PPM prediction model to obtain a prediction model tree, a next access webpage of the user is predicted on the basis of the prediction model tree through a Markov model, a pre-fetch operation is conducted, and pre-fetch content is updated into the cache. The webpage browsing accelerating method is based on the home gateway, achieves webpage browsing acceleration by the adoption of the cache and the pre-fetch technology, and is low in cost and more obvious in accelerating effect.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

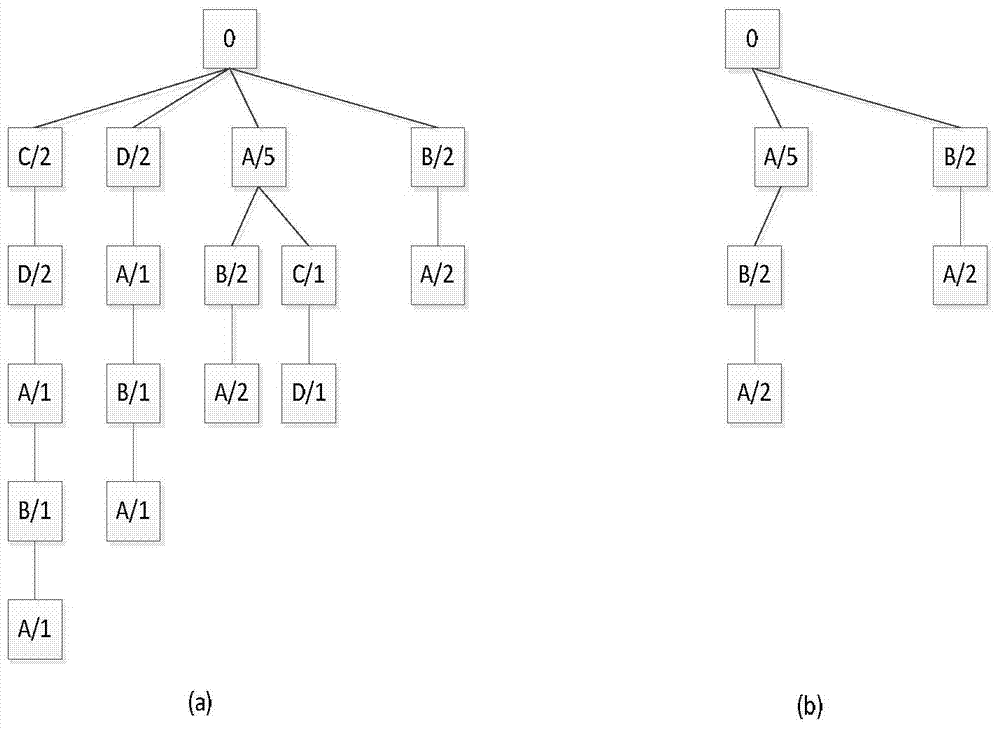

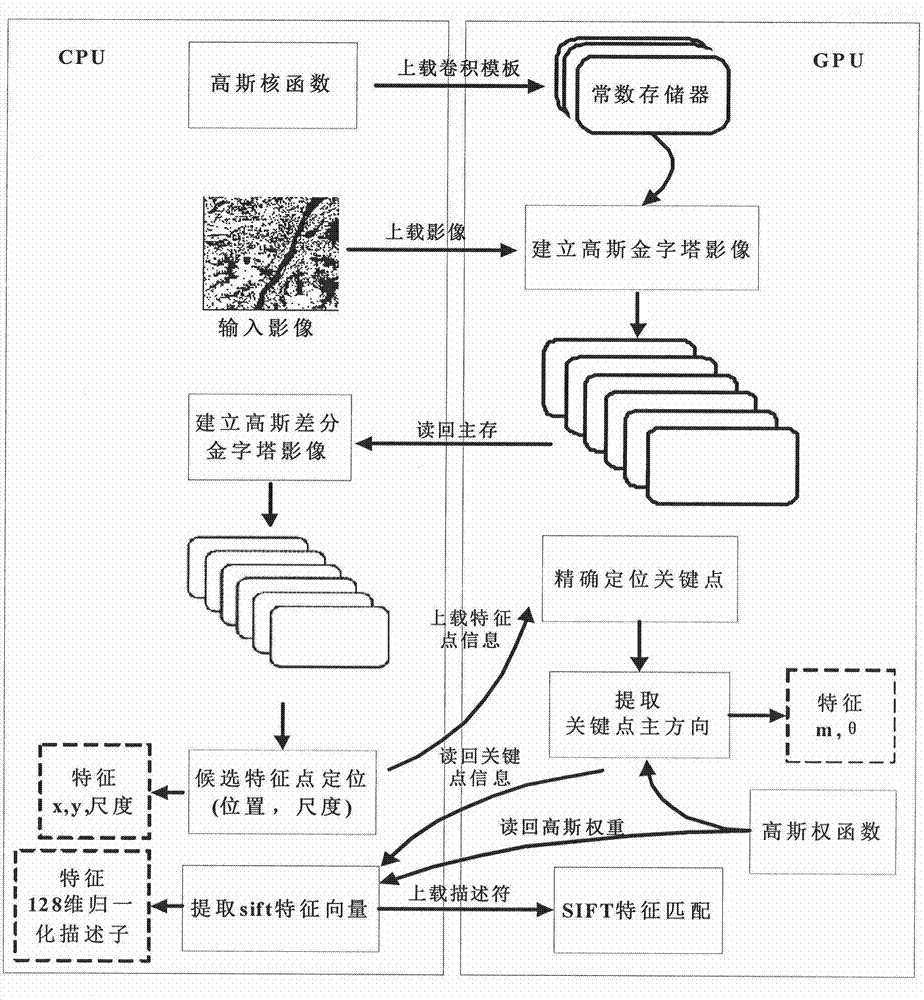

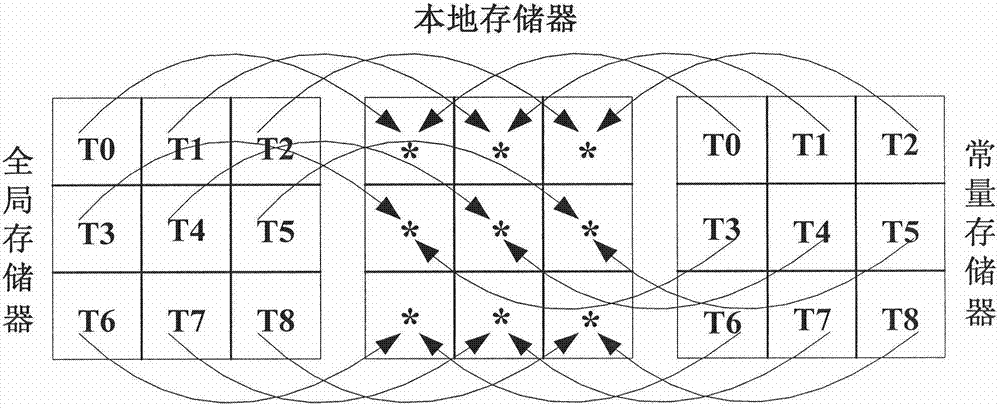

SIFT feature matching method based on OpenCL parallel acceleration

InactiveCN104732221AIrrelevantThe acceleration effect is obviousCharacter and pattern recognitionPattern recognitionParallel algorithm

The invention relates to an SIFT feature matching method based on OpenCL parallel acceleration. The SIFT feature matching method includes the steps of SIFT feature matching parallel calculation, chessboard type convolution operation based on OpenCL and task distribution and mapping of working nodes. Plenty of calculation is partitioned to be conducted separately between a CPU and a GPU, the calculation advantages of the CPU and the GPU are played, the strong ability of CPU plus GPU heterogeneous calculation is fully reflected, real-time performance is high, and a Sift feature matching parallel algorithm with transportability achieves platform independence.

Owner:ZHENGZHOU NORMAL UNIV

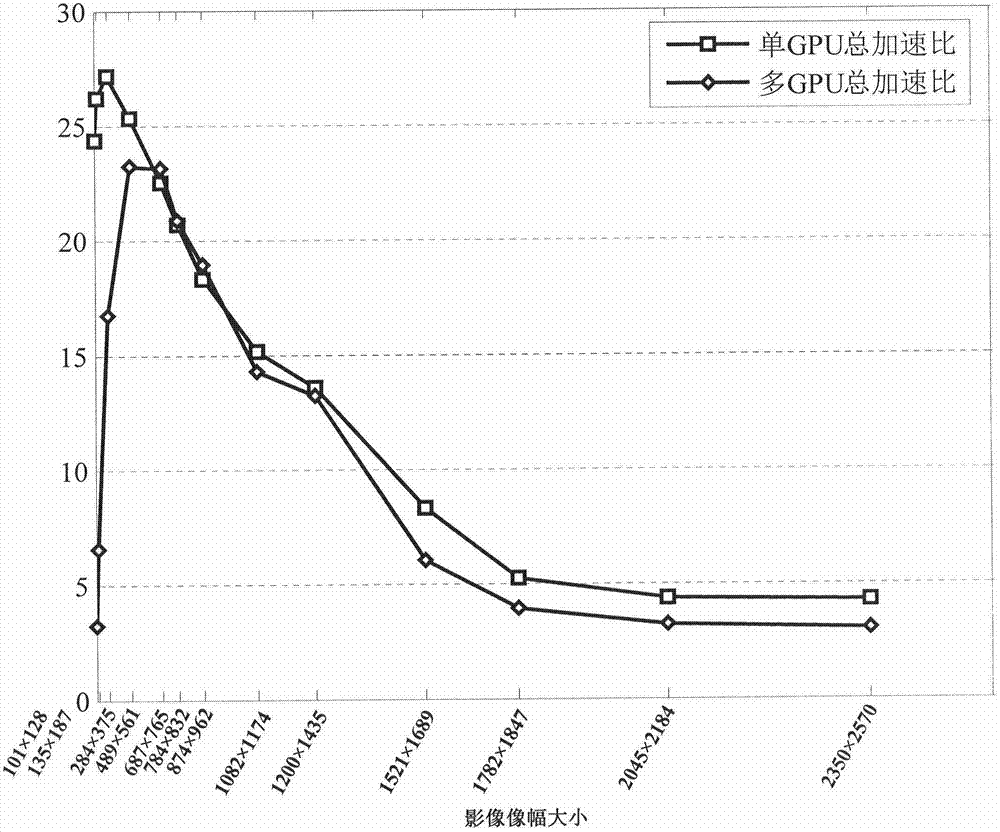

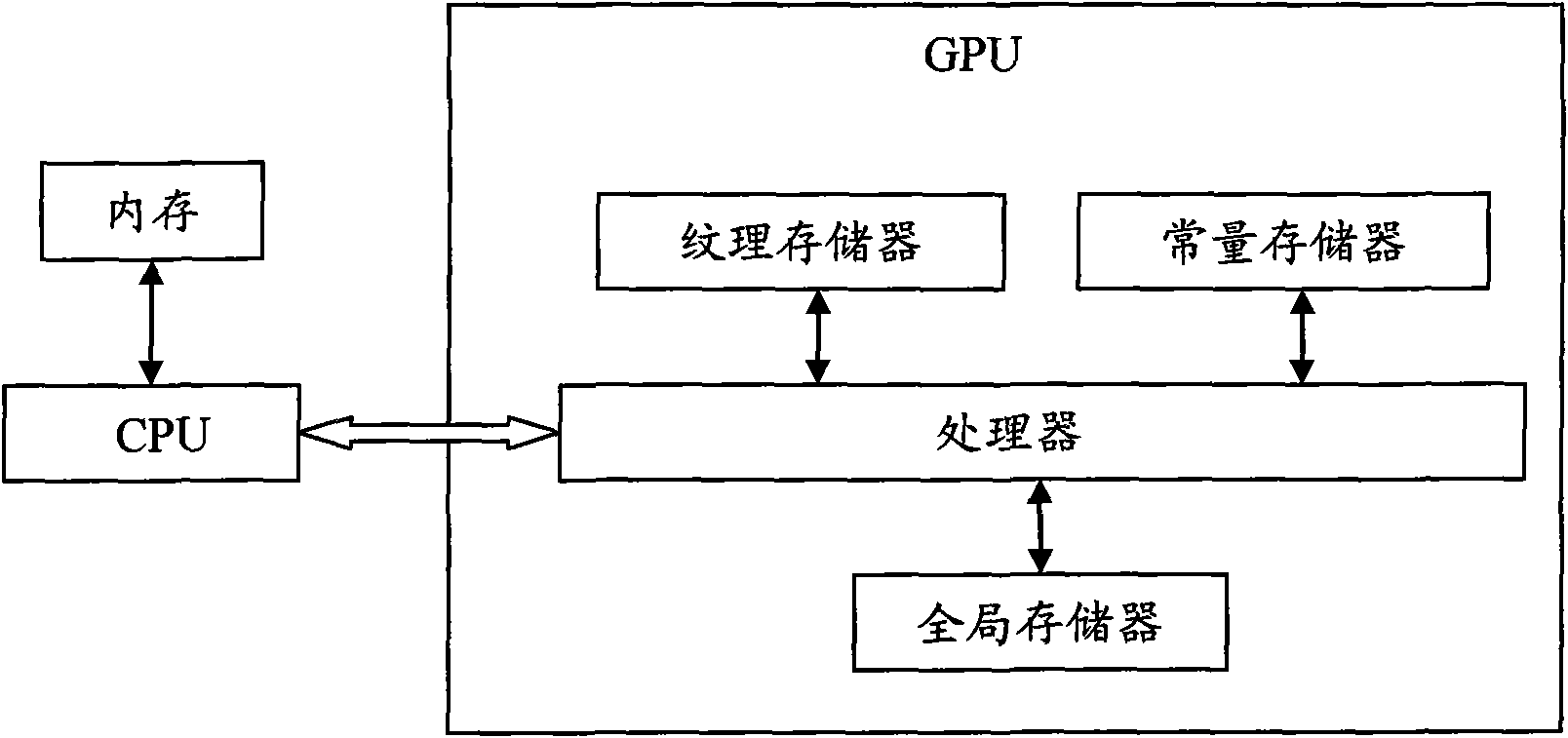

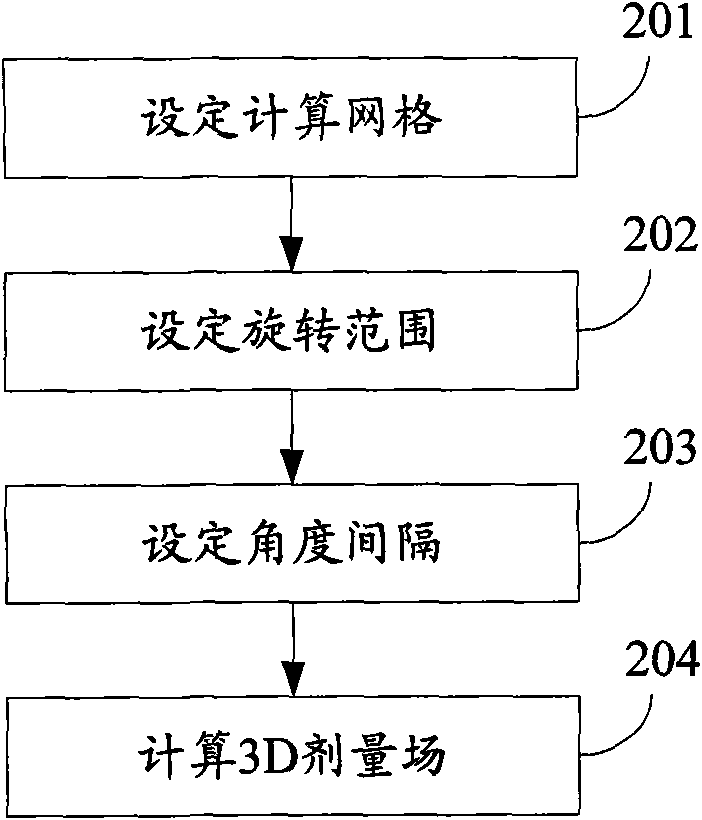

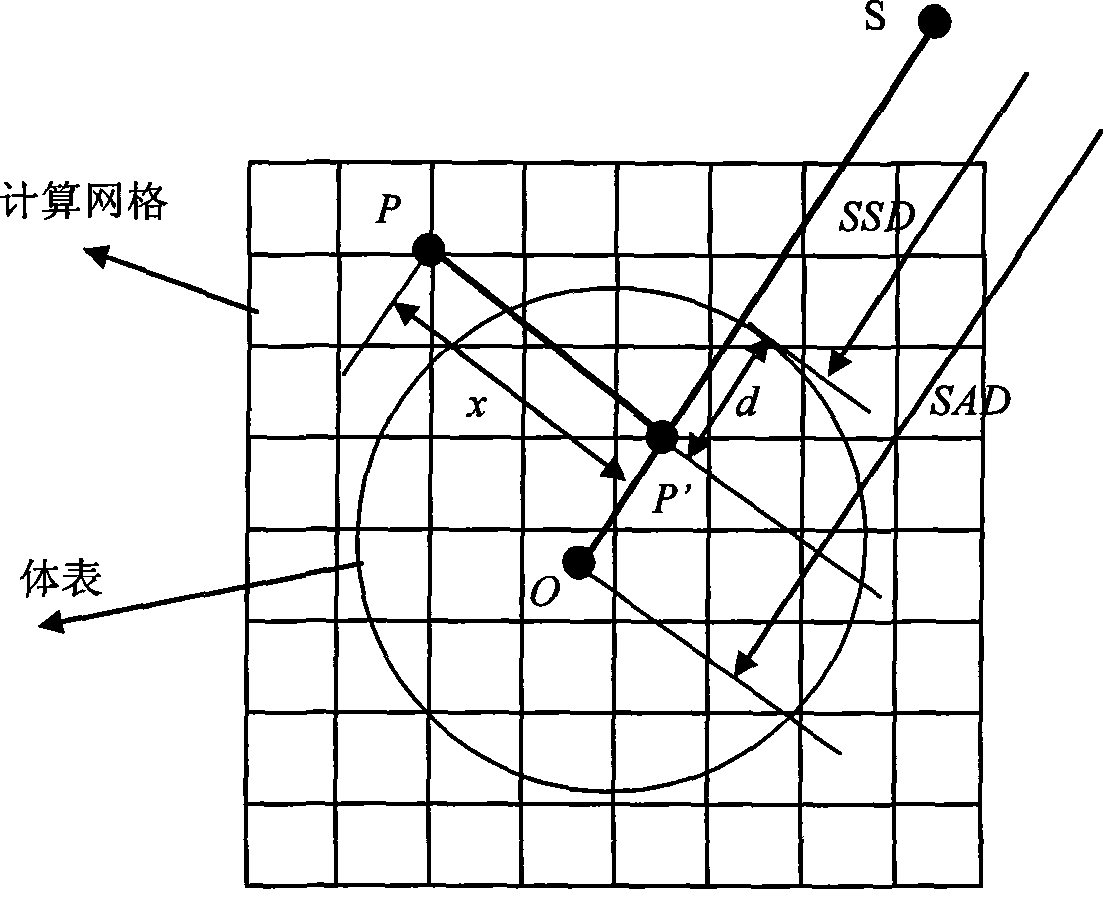

Dosage calculation optimization method and system based on CUDA

ActiveCN101664583ATake full advantage of parallel computingHigh Computational SpeedupSpecial data processing applicationsX-ray/gamma-ray/particle-irradiation therapyOptimization systemCUDA

The invention discloses a dosage calculation optimization method based on CUDA, which comprises the following steps: a central processing unit transmits the part of data of dosage calculation, which can be subjected to parallel computing, to a display processing unit; the display processing unit conducts the parallel computing to the received data according to pre-defined algorithm; and the display processing unit returns the calculation result. The invention also discloses a dosage calculation optimization system based on CUDA. The invention utilizes GPU hardware to provide higher calculationspeedup ratio, and transmits the part which can be subjected to the parallel computing to the GPU for calculation, thus bringing the advantages of the parallel computing of the GPU into full play, and effectively improving the calculation speed.

Owner:SHEN ZHEN HYPER TECH SHENZHEN

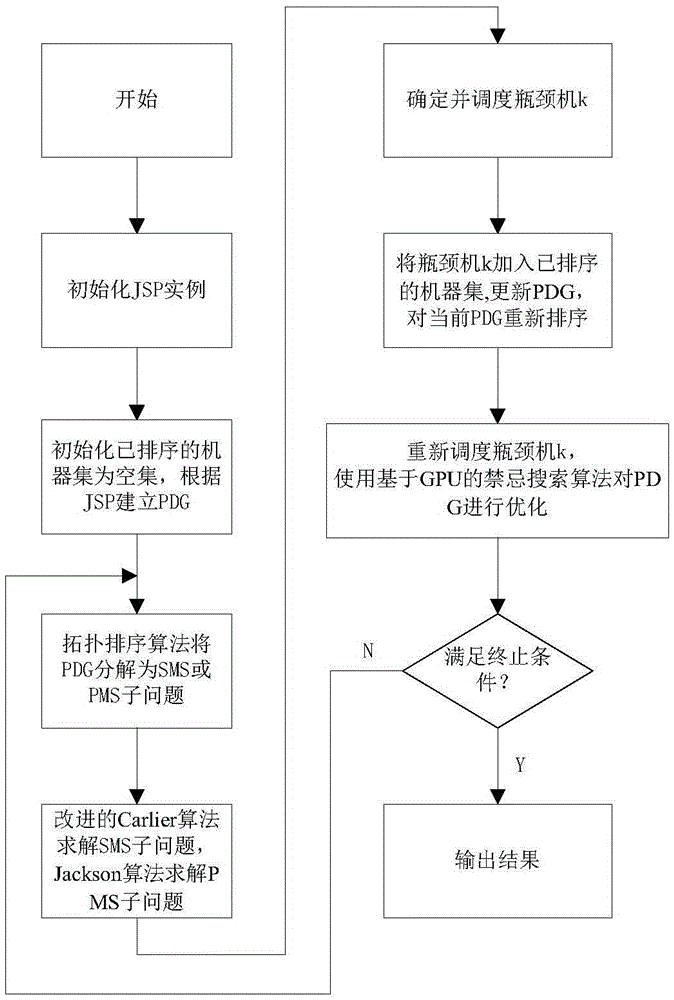

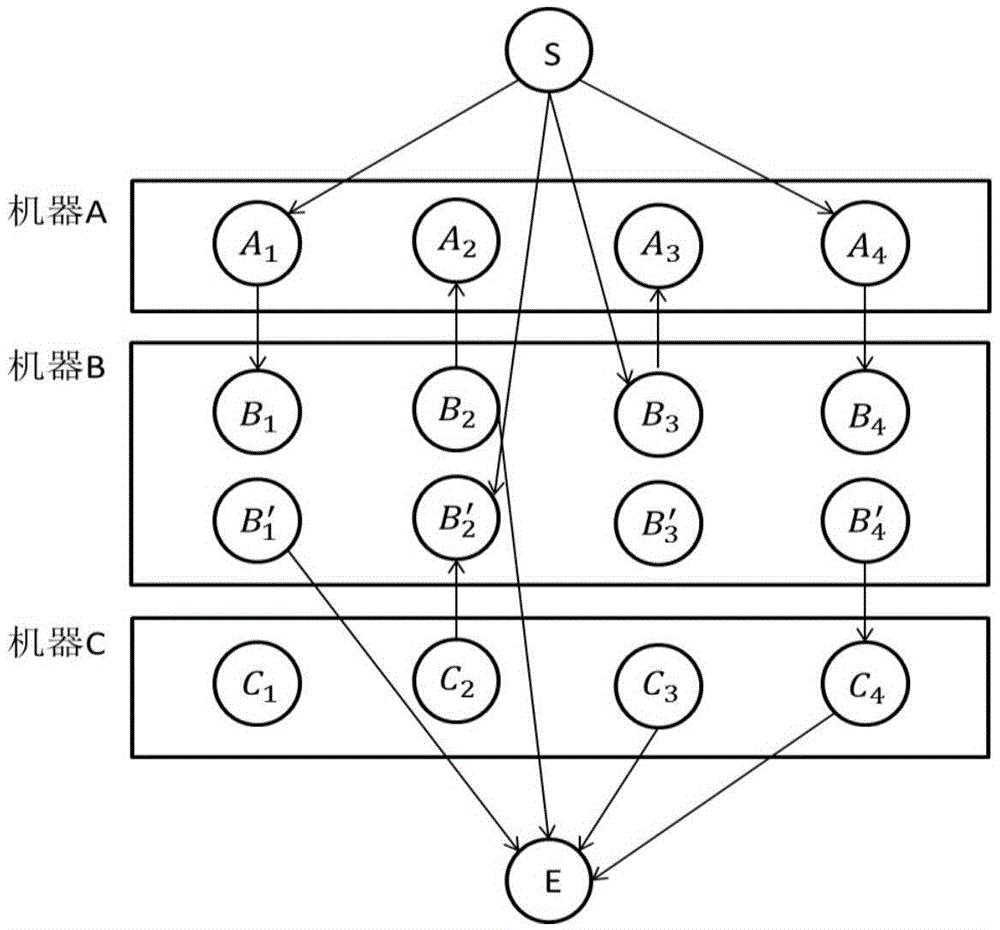

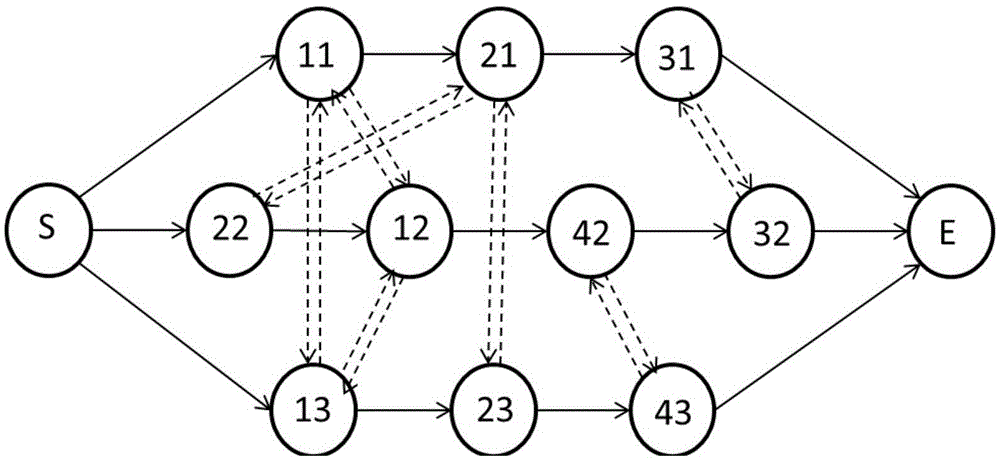

Hybrid heuristic shifting bottleneck procedure for solving parallel-machine job-shop scheduling

The invention provides a hybrid heuristic shifting bottleneck procedure for solving parallel-machine job-shop scheduling. According to the procedure, a hybrid shifting bottleneck procedure is provided by combining a shifting bottleneck procedure and a heuristic tabu search method, and a GPU is further utilized to achieve a parallel tabu search algorithm. The hybrid shifting bottleneck procedure comprises the following solving processes of (1) decomposing a PDG of a parallel-machine job shop into a series of single-machine scheduling (SMS) sub-problems and parallel-machine scheduling (PMS) sub-problems; (2) solving each SMS sub-problem and PMS sub-problem; (3) determining and scheduling bottleneck machines; and (4) carrying out reordering and optimization on the current PDG during each iteration and rescheduling the scheduled bottleneck machines. According to the hybrid procedure, an unstable search result is avoided, an optimal solution can be found out and the calculation time of finding the optimal solution is shortened.

Owner:SICHUAN YONGLIAN INFORMATION TECH CO LTD

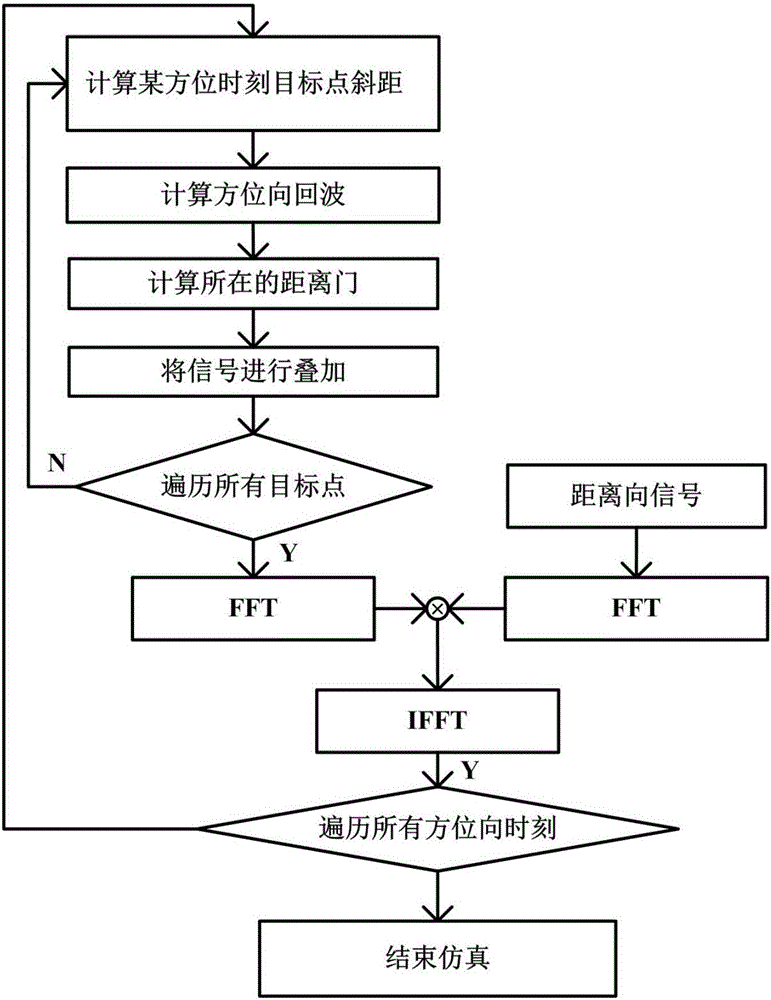

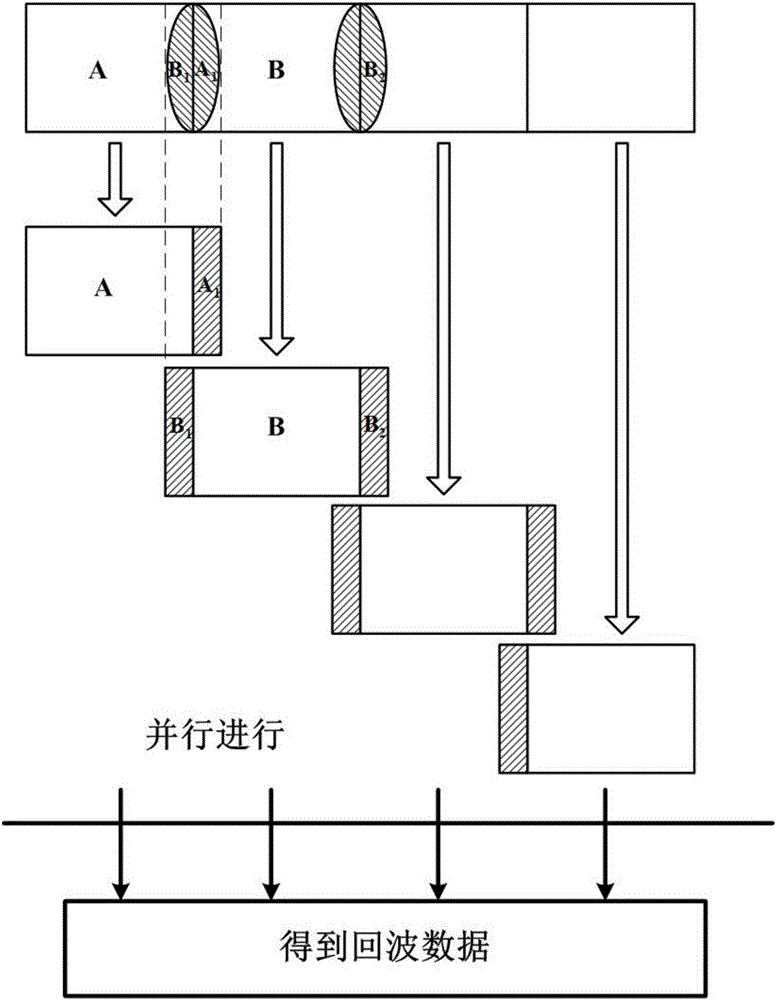

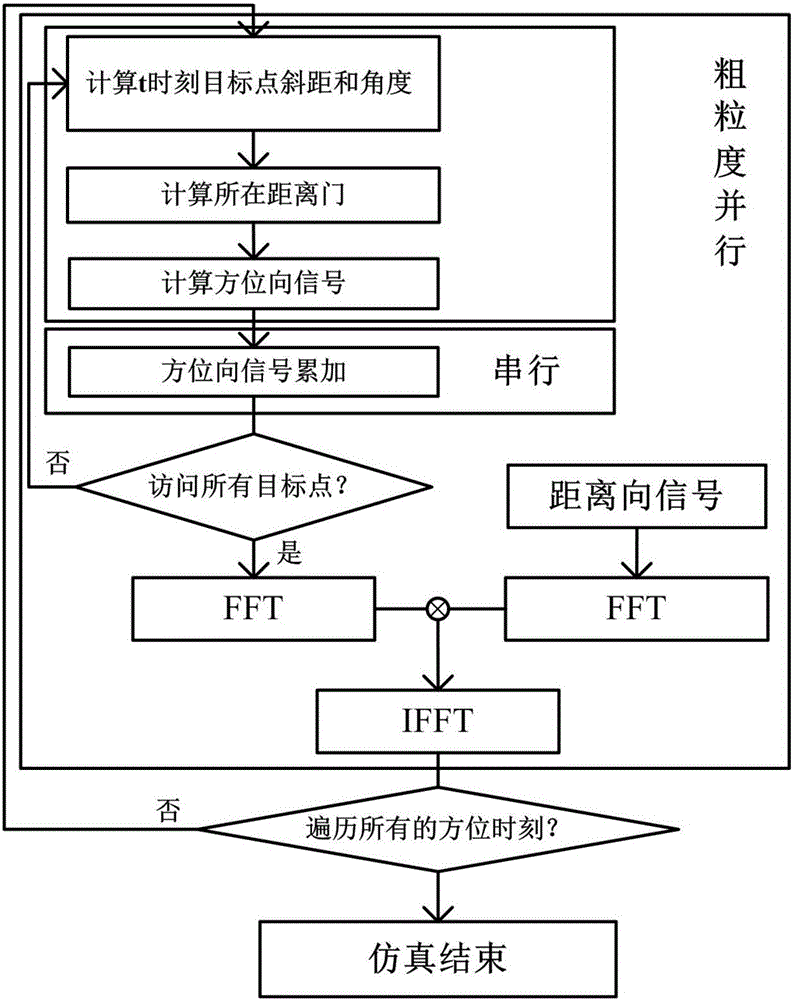

Synthetic aperture radar echo parallel simulation method based on depth cooperation

ActiveCN105911532AOptimize co-processing modeCollaborative processing mode is obviousRadio wave reradiation/reflectionSynthetic aperture radarRadar

The invention discloses a synthetic aperture radar echo parallel simulation method based on depth cooperation, belonging to the technical field of synthetic aperture radar application. Under the traditional CPU+GPU heterogeneous computing mode, generally CPU refers to operation with high processing logicality, while GPU refers to computing which is used for processing relatively dense data and is suitable for parallel operations. The invention takes an example by a related satellite-borne SAR echo simulation parallel simulation algorithm on the basis of fully researching related articles of SAR rapid echo simulation at home and abroad, and provides a satellite-borne SAR rapid echo simulation algorithm based on SIMD heterogeneous parallel processing, the SAR echo simulation process is accelerated in parallel by virtue of depth cooperation of multi-core vector expanded CPU / many-core GPU, optimization of redundant computation and parallel depth optimization aiming at irregular problem computing in the SAR echo process are performed on the basis. The experimental result proves that compared with the traditional serial computing method, the optimized CPU / GPU heterogeneous cooperation mode has the advantage that the computational efficiency can be improved by 2-3 order of magnitudes.

Owner:BEIJING UNIV OF CHEM TECH

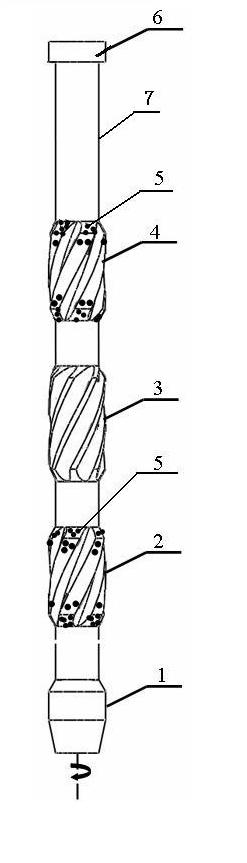

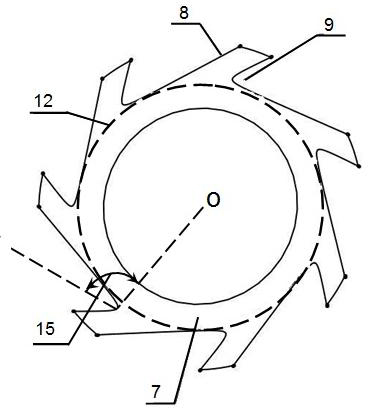

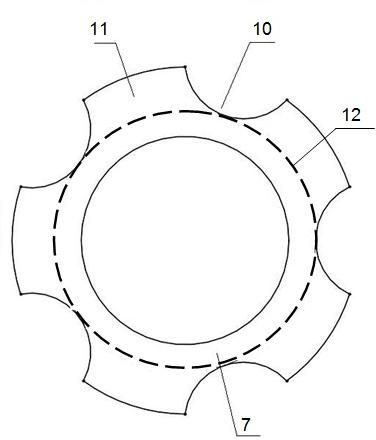

Rock debris cleaning device for drilling tool

The invention relates to a rock debris cleaning device for a drilling tool. The rock debris cleaning device for the drilling tool consists of a body, a rotating speed increaser and reaming protectors, wherein the body is a round steel pipe; an upper reaming protector, the rotating speed increaser and a lower reaming protector are arranged on an outer wall of the body; the rotating speed increaser is positioned between the upper reaming protector and the lower reaming protector; the rotating speed increaser consists of spiral blades and a debris discharging groove; the spiral blades are uniformly distributed by equal central angles; the upper reaming protector and the lower reaming protector consist of spiral protection blades which are uniformly distributed by equal central angles; a curved debris discharging groove is formed among the spiral protection blades; and a spiral angle of the rotating speed increaser, a spiral angle of the upper reaming protector and a spiral angle of the lower reaming protector are equal to one another. The rotating speed increaser can be protected by the reaming protectors, the wear of uneven walls of the well on the rotating speed increaser is reduced, even if the drilling tool is bent or buckled, the collision between the rotating speed increaser and the walls of the well also can be reduced, and the service life of the tool is prolonged.

Owner:NORTHEAST GASOLINEEUM UNIV

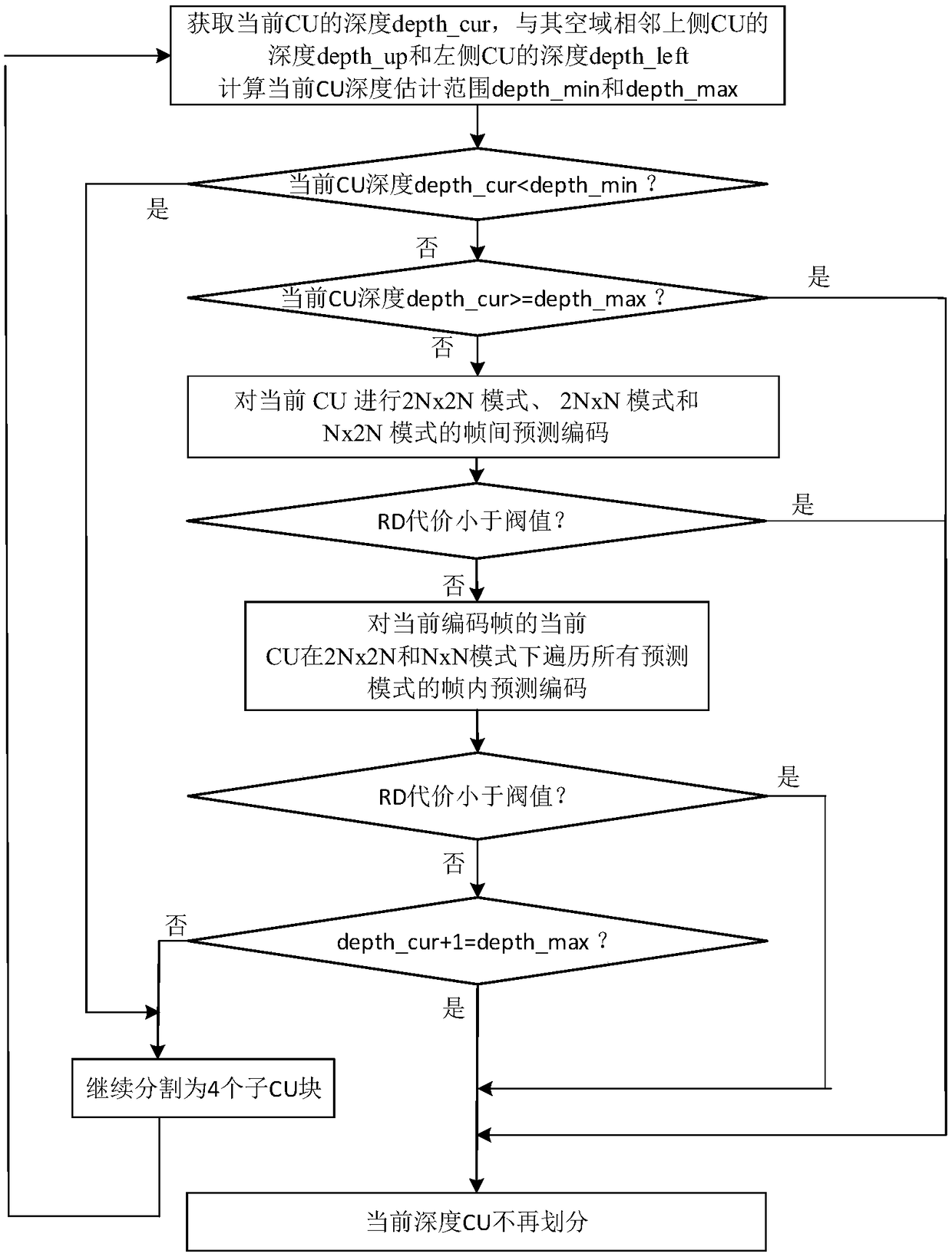

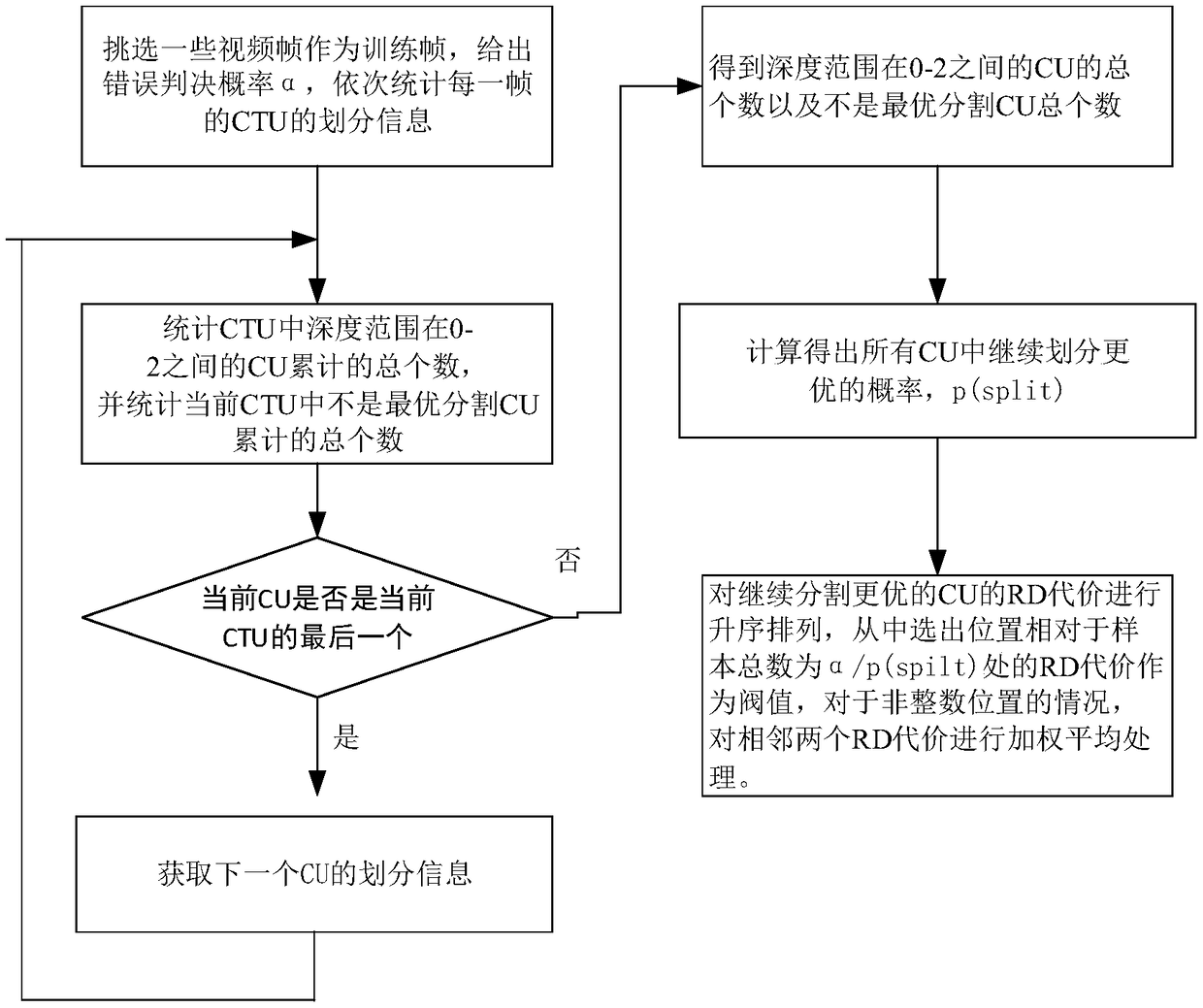

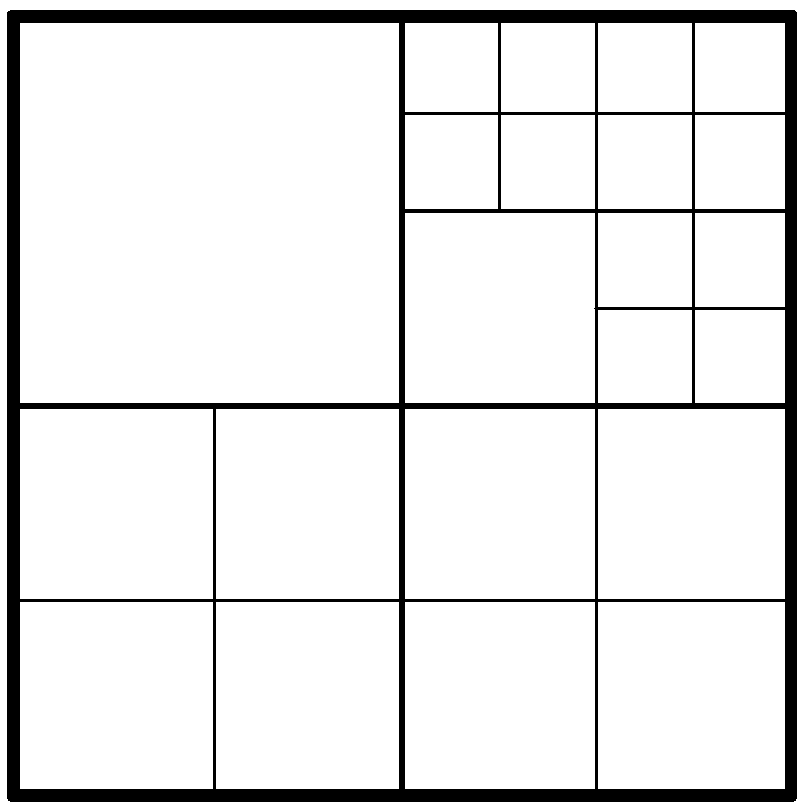

Coding unit (CU) division method applied to high efficiency video coding (HEVC)

InactiveCN108712647AReduce computational complexityImprove encoding speedDigital video signal modificationComputation complexityComputer architecture

The invention discloses a coding unit (CU) division method applied to high efficiency video coding (HEVC), and relates to a HEVC technology. The invention aims at solving the problem that the existingHEVC coding technology is high in computing complexity and slow in coding speed. The method comprises the steps of 1, if the depth of the current CU is less than a minimum depth, turning to the step5; if the depth of the current CU is more than or equal to the maximum depth, ending; and otherwise turning to the step 2; 2, performing interframe prediction coding of 2N*2N, 2N*N and N*2N modes on the current CU, computing rate-distortion cost, if the rate-distortion cost is less than a threshold, ending, and otherwise, turning to the step 3; 3, performing interframe prediction coding of 2N*2N and N*N modes , computing the rate-distortion cost, if the rate-distortion cost is less than a threshold, ending, and otherwise, turning to the step 4; 4, judging whether the current CU reaches the maximum depth, if yes, ending, and otherwise, turning to the step 5; and 5, continuously dividing the current CU into four N*N sub-CU with the same size, and turning to the step 1. The method provided bythe invention is applied to the field of HEVC.

Owner:HARBIN INST OF TECH

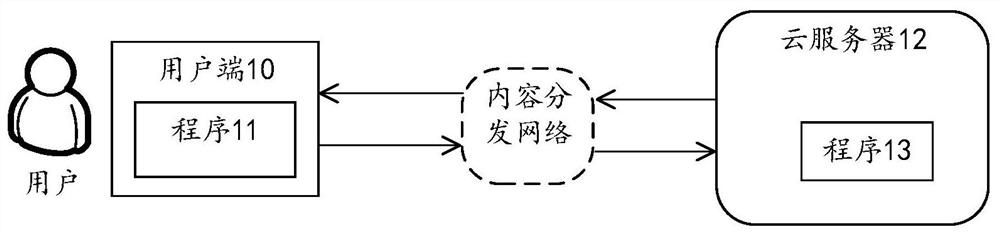

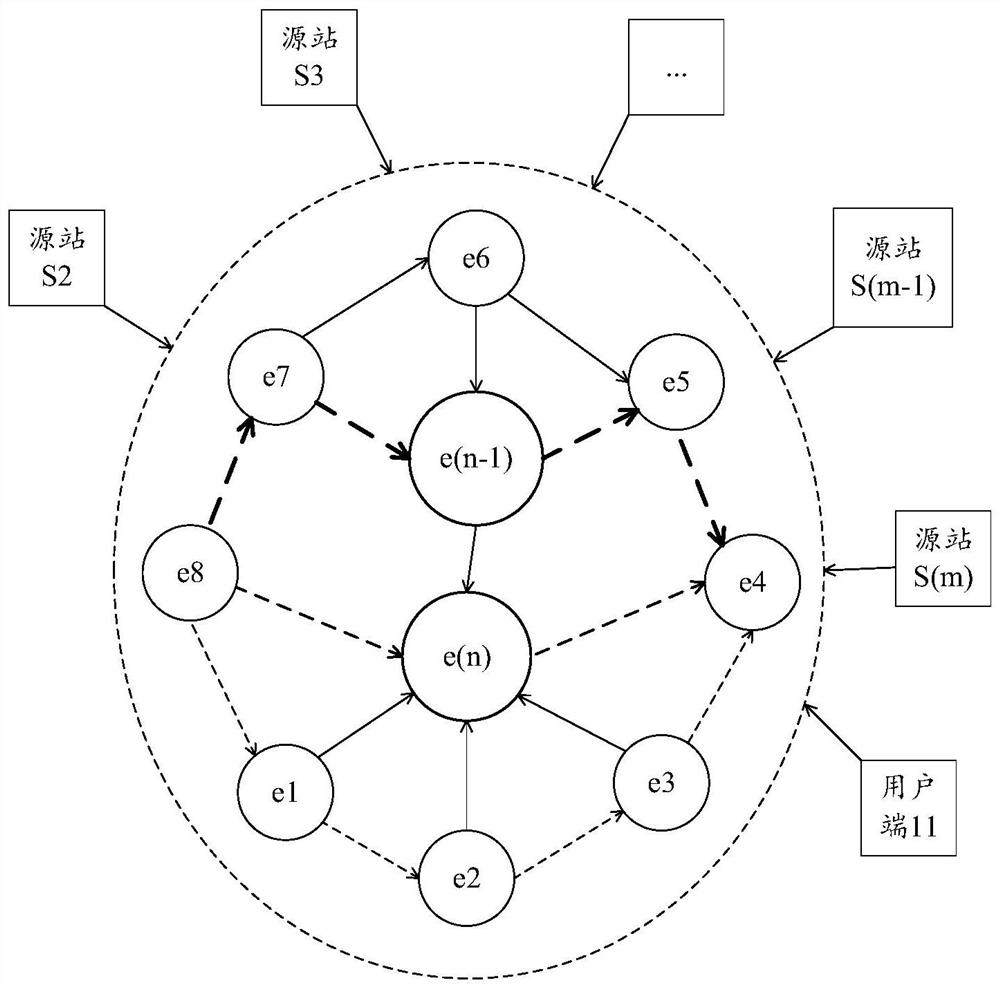

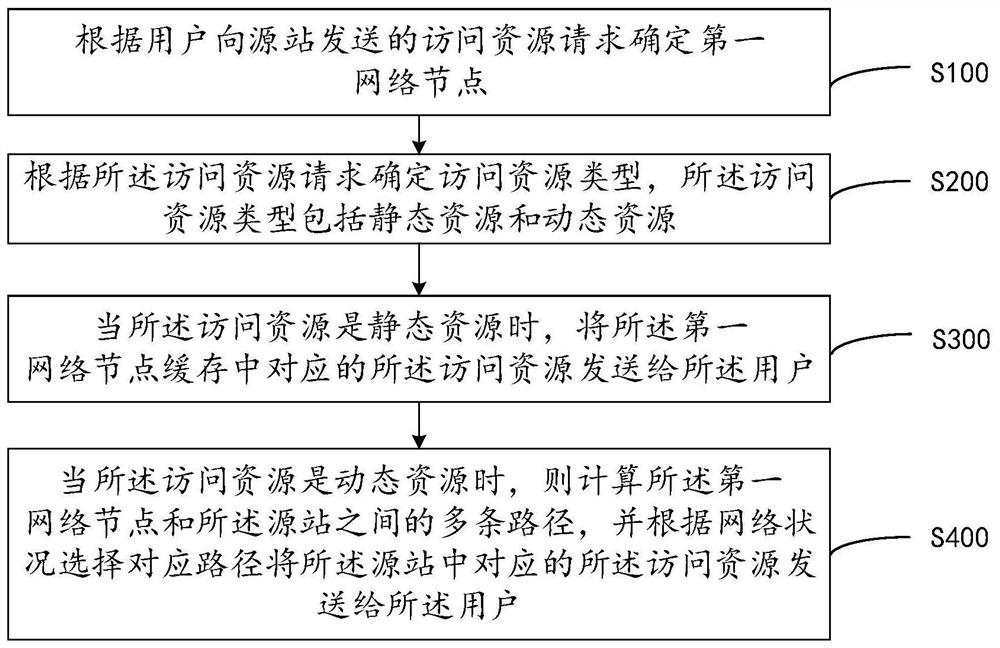

Data transmission method and device, computer equipment and storage medium

PendingCN112256495AThe acceleration effect is obviousQuick switchData switching networksRedundant hardware error correctionPathPingStation

The invention discloses a data transmission method and device, computer equipment and a storage medium, and the method comprises the steps: determining a first network node according to an access resource request sent to a source station by a user, determining the type of an access resource according to the access resource request, and when the access resource is static, sending the correspondingaccess resource in the first network node cache to the user; and when the access resource is a dynamic resource, calculating a plurality of paths between the first network node and the source station,and selecting a corresponding path according to the network condition to send the corresponding access resource in the source station to the user, thereby ensuring the optimal acceleration effect andstable acceleration effect. The method and device can be applied to smart government affairs, smart city management, smart communities, smart security and protection, smart logistics, smart medical treatment, smart education, smart environmental protection and smart traffic scenes, so that the construction of smart cities is promoted.

Owner:PING AN TECH (SHENZHEN) CO LTD

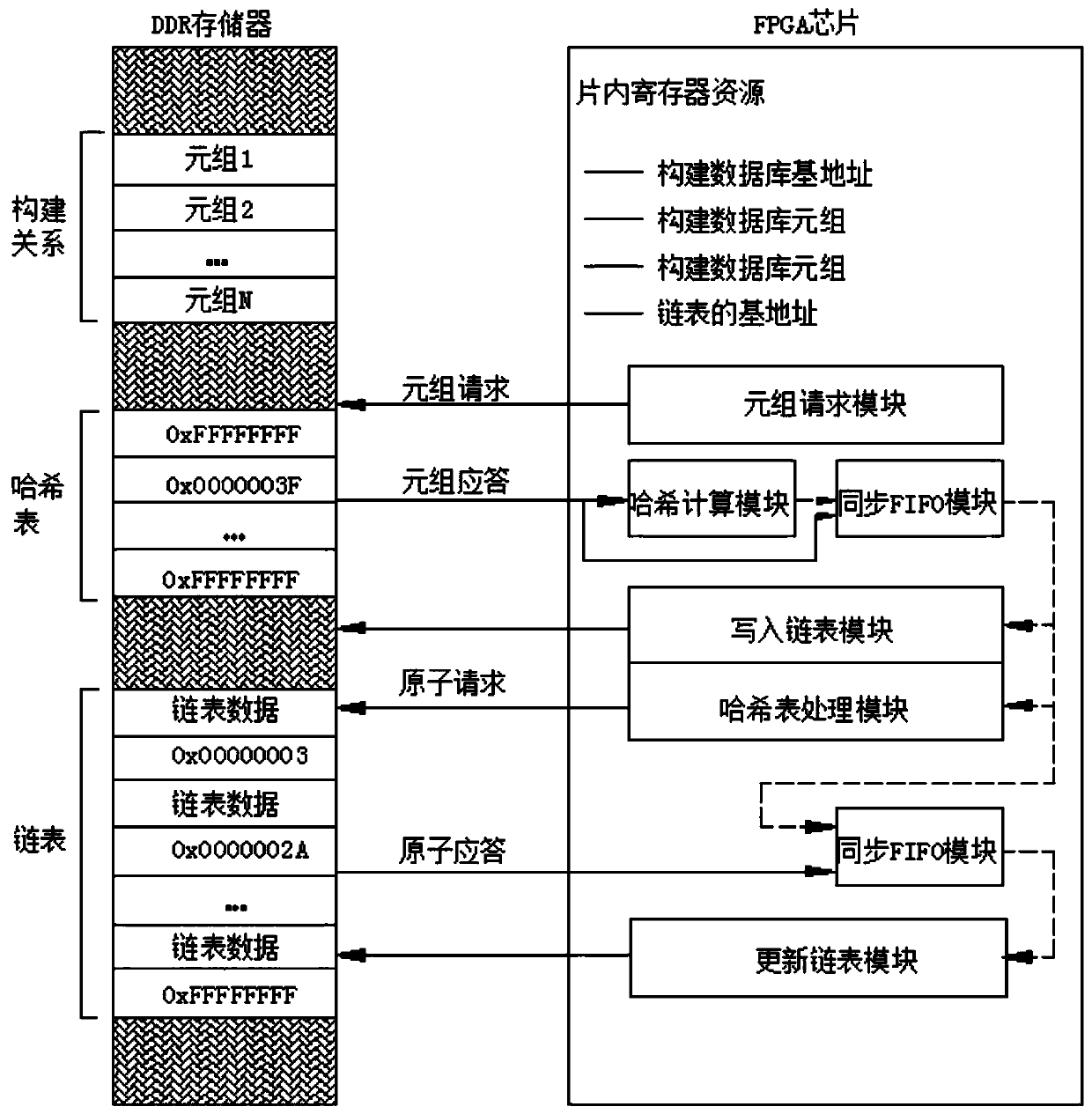

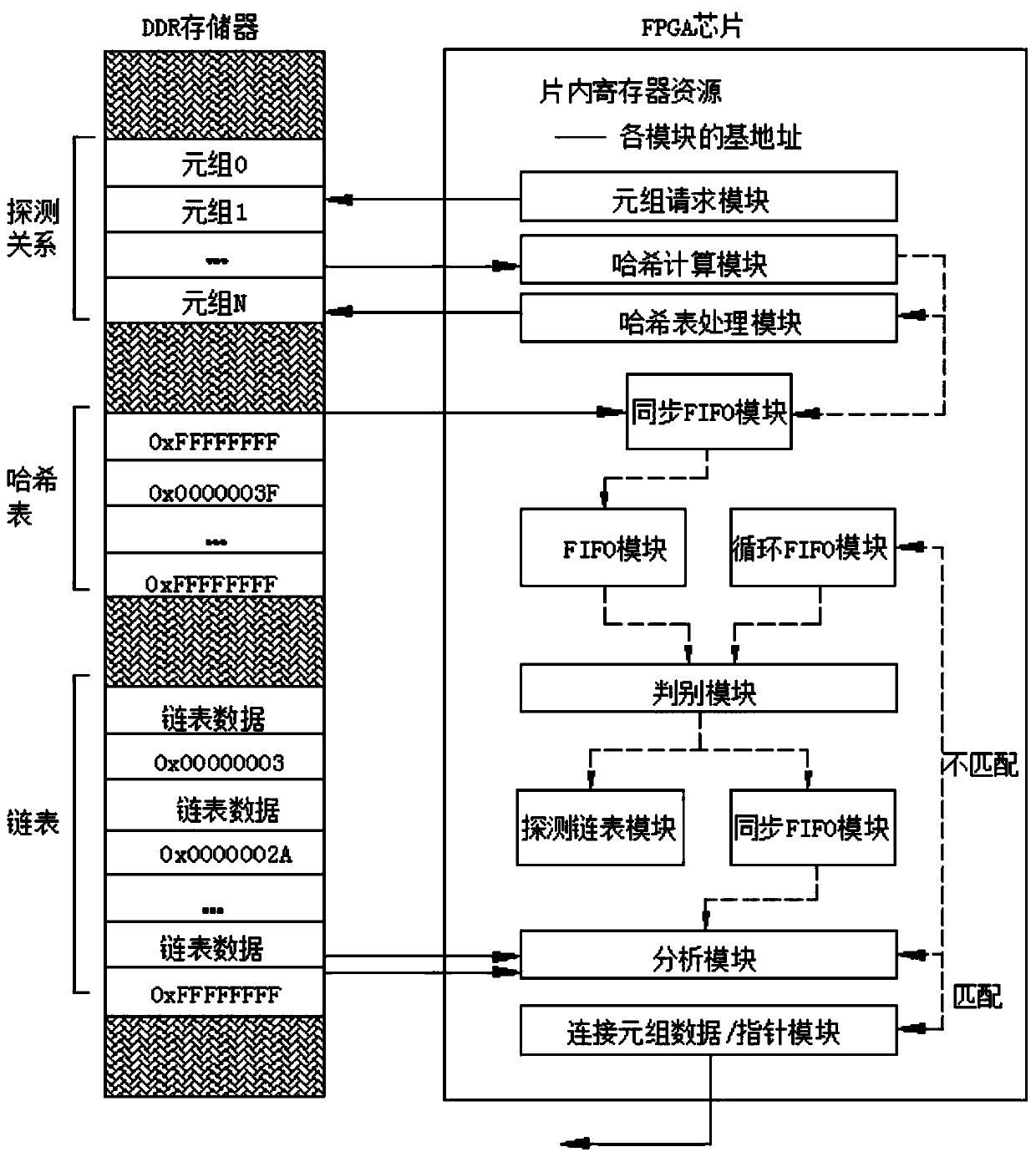

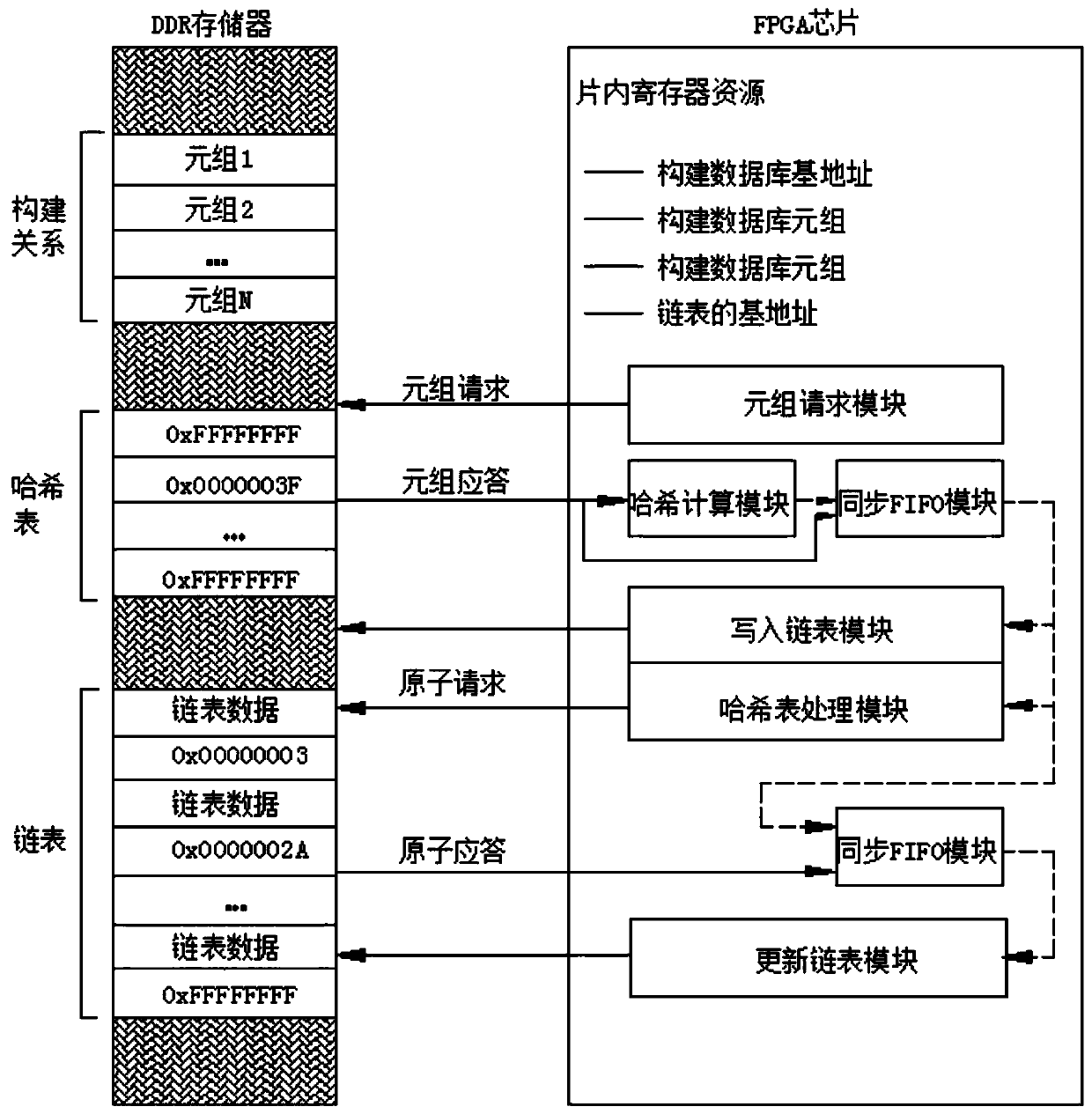

Hash join operator acceleration method and system based on FPGA-DDR

ActiveCN109977116AImprove operational efficiencyMake up for bandwidth issuesEnergy efficient computingSpecial data processing applicationsIn-memory databaseHash join

The invention discloses a Hash join operator acceleration method and system based on an FPGA-DDR, and belongs to the field of acceleration of a memory database. The technical problem to be solved is how to realize acceleration operation in a construction stage and a detection stage of a Hash connection algorithm. The method comprises: storing a tuple, a hash table and a linked list through a DDR memory, hash calculation is conducted through an FPGA chip, the hash table and the linked list are updated, and the FPGA chip is controlled to conduct interactive communication facing the DDR memory; under the cooperation of the DDR memory and the FPGA chip, parallel multi-thread operation is executed in the construction stage and the detection stage of the hash connection to realize the construction and matching of the hash table. The system comprises a DDR memory and an FPGA chip, the DDR memory is used for storing a tuple, a hash table and a linked list, and the FPGA chip is used for storinga base address, executing hash calculation, updating the hash table and the linked list and controlling the DDR memory to perform interactive communication.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD

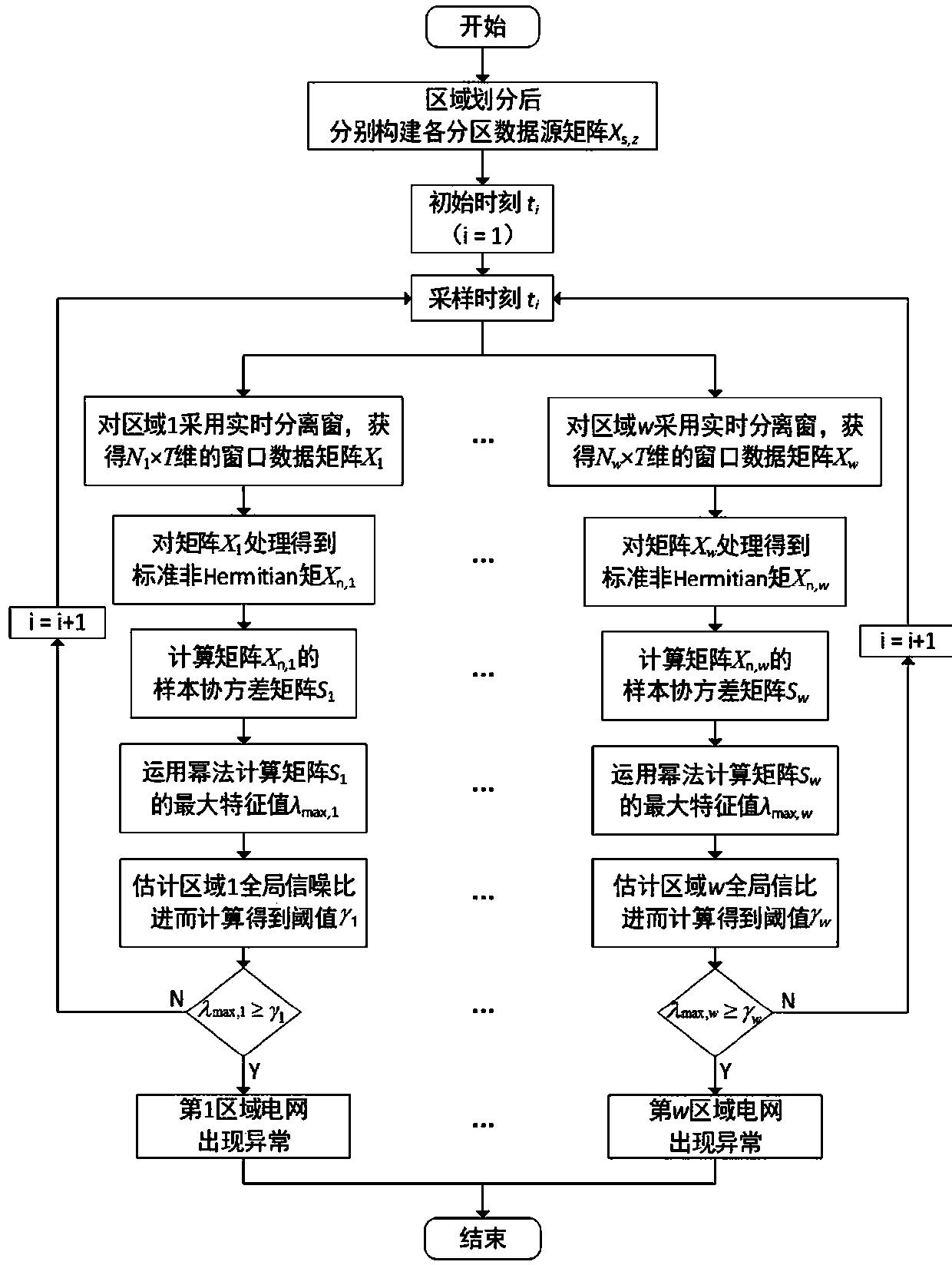

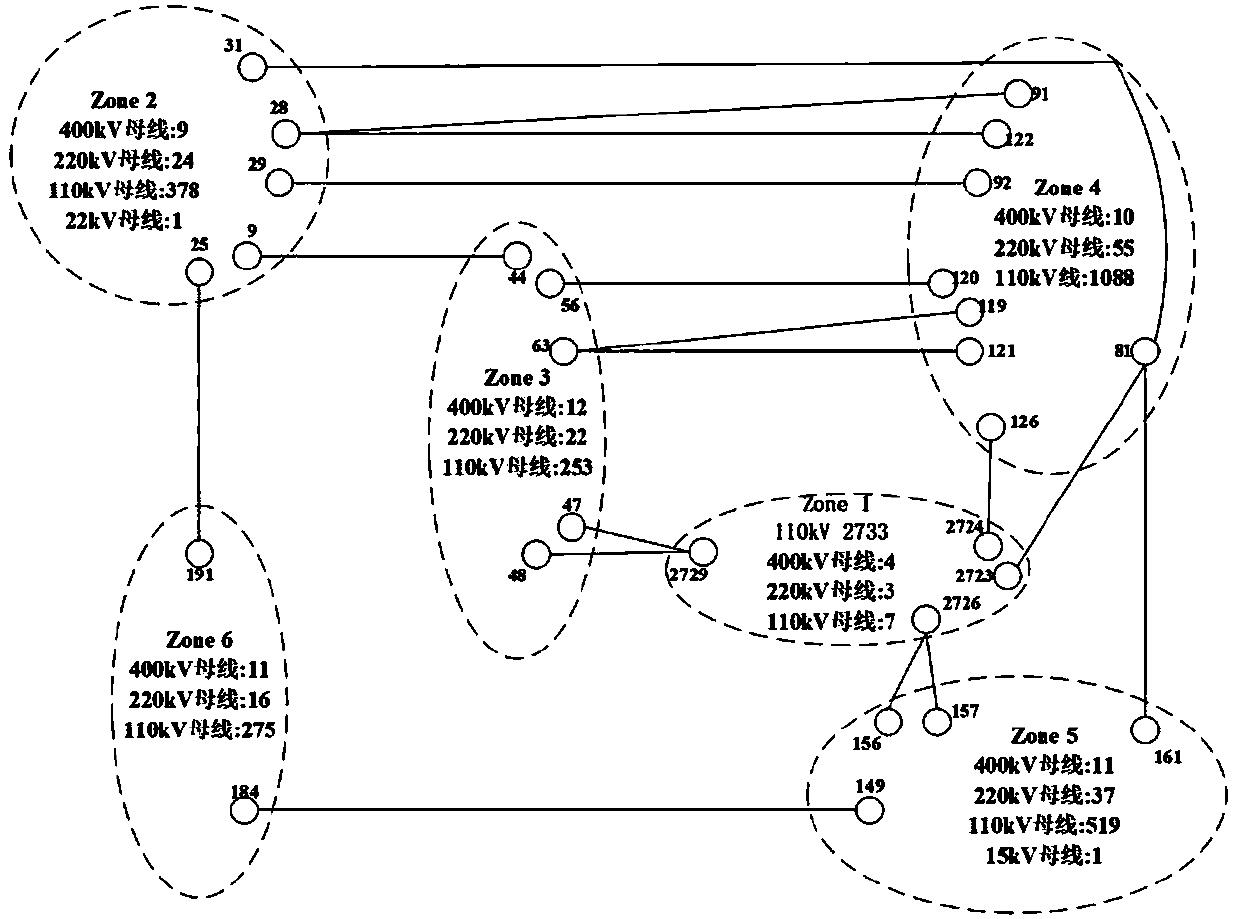

Large-scale power grid abnormal load identification method based on a power method and a parallel computing technology

ActiveCN109657613AImprove computing efficiencyThe acceleration effect is obviousData processing applicationsCharacter and pattern recognitionHermitian matrixPower grid

The invention discloses a large-scale power grid abnormal load identification method based on a power method and a parallel computing technology. The large-scale power grid abnormal load identification method comprises the following steps that step 1, data source matrixes Xs and z of all partitions are synchronously constructed; Step 2, the time window width T of each partition is determined and asampling starting moment t < 1 > is set; Step 3, a sliding window matrix X < z > of each partition is synchronously obtained ; 4, the sliding window matrixes X < z > of all the partitions are subjected to standardization processing synchronously, and non-Hermitian matrixes X < n > and X < z > of all the partition standards are obtained; 5, a sample covariance matrix S < z > of each partition is synchronously obtained ; 6, the maximum characteristic values max (th) and z (th) of the sample covariance matrix of each partition are quickly estimated by using a power method; 7, each partition estimates the signal-to-noise ratio z at the current moment, so that the dynamic threshold z of the maximum characteristic value of the sample covariance matrix of the corresponding partition is obtained;And 8, power grid state abnormity out-of-limit judgment is carried out. The method has the characteristics that the calculation efficiency can be remarkably improved, and the applicability to large-scale power grid application is enhanced.

Owner:GUIZHOU UNIV

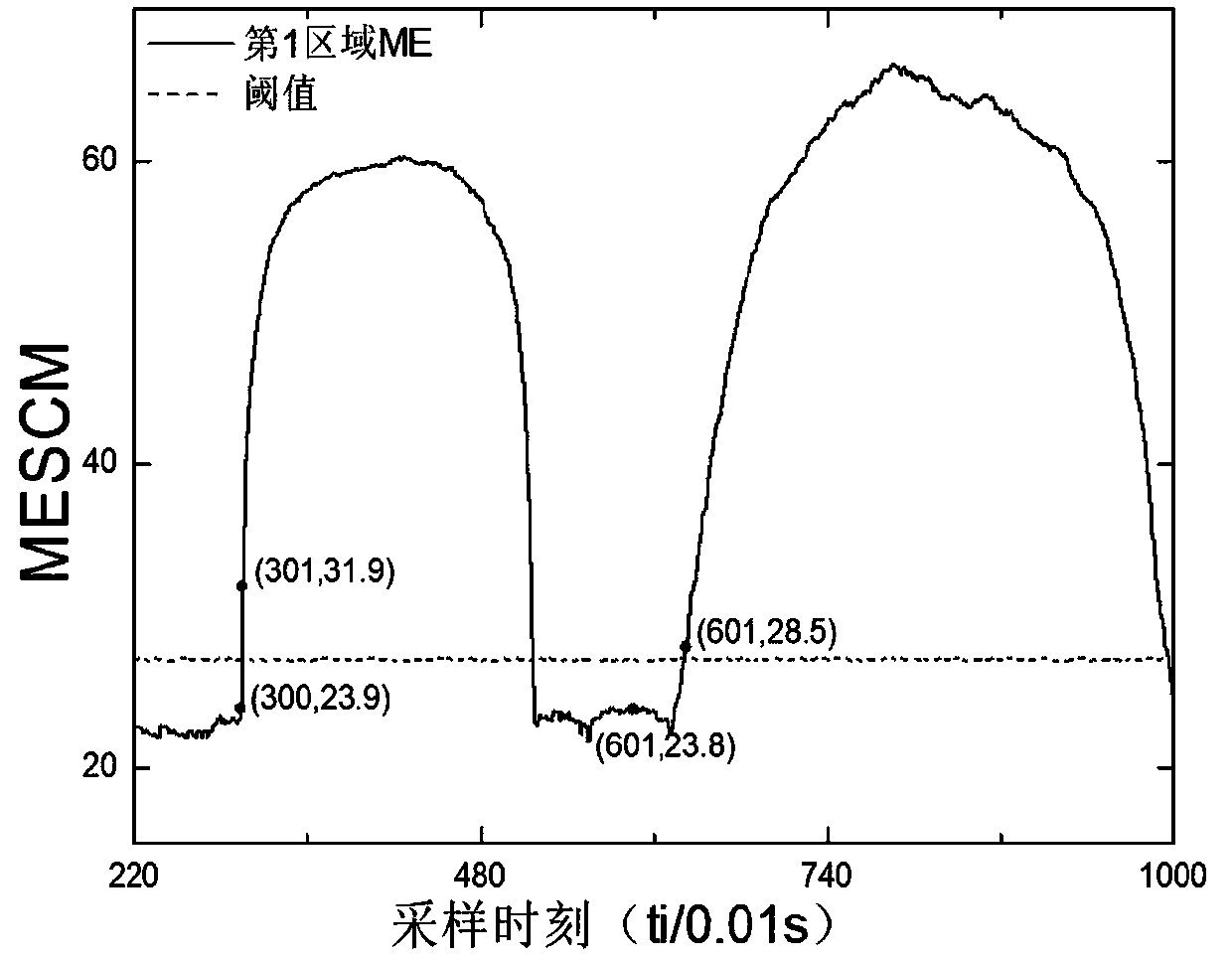

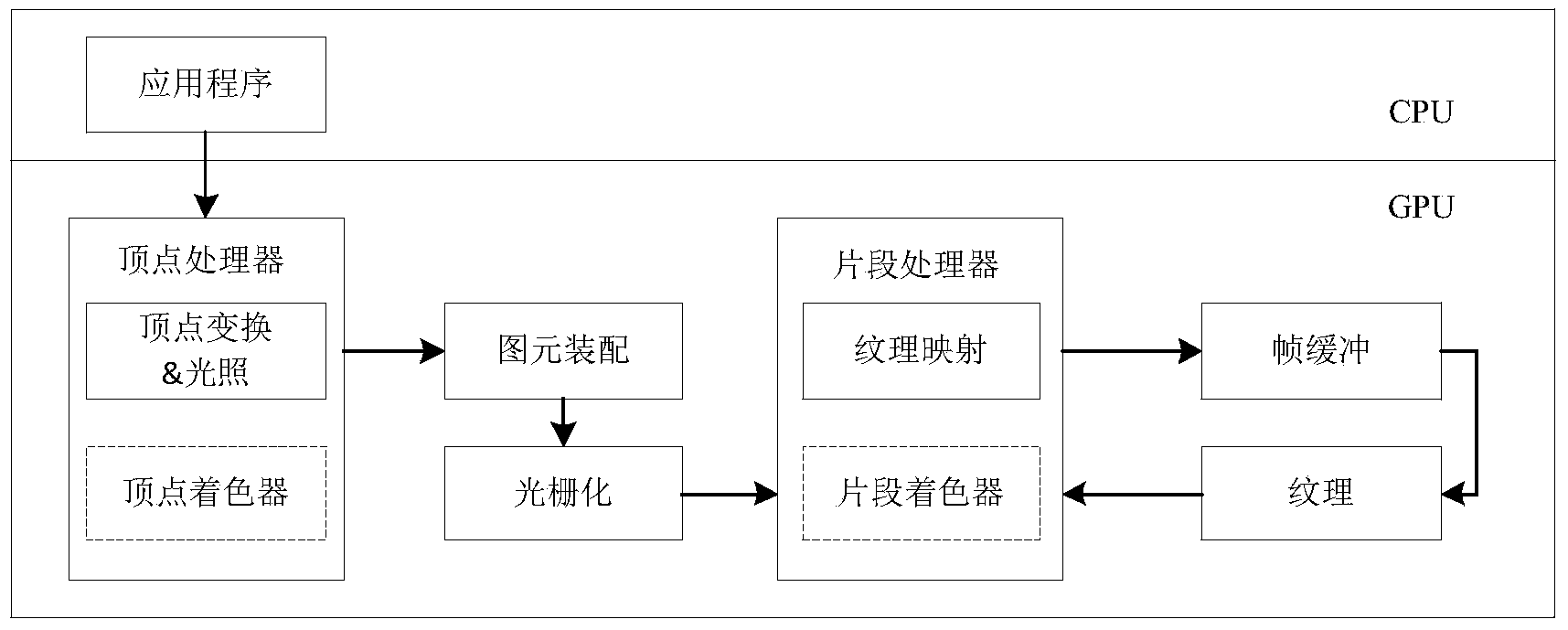

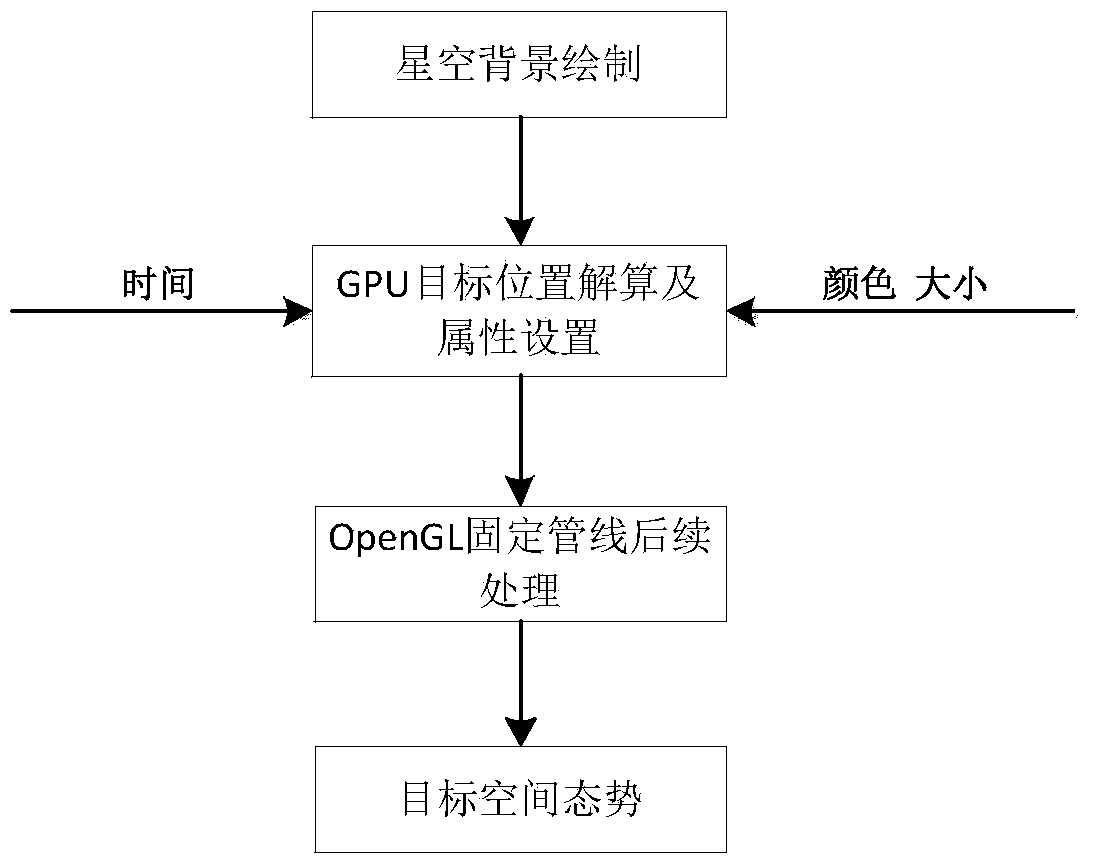

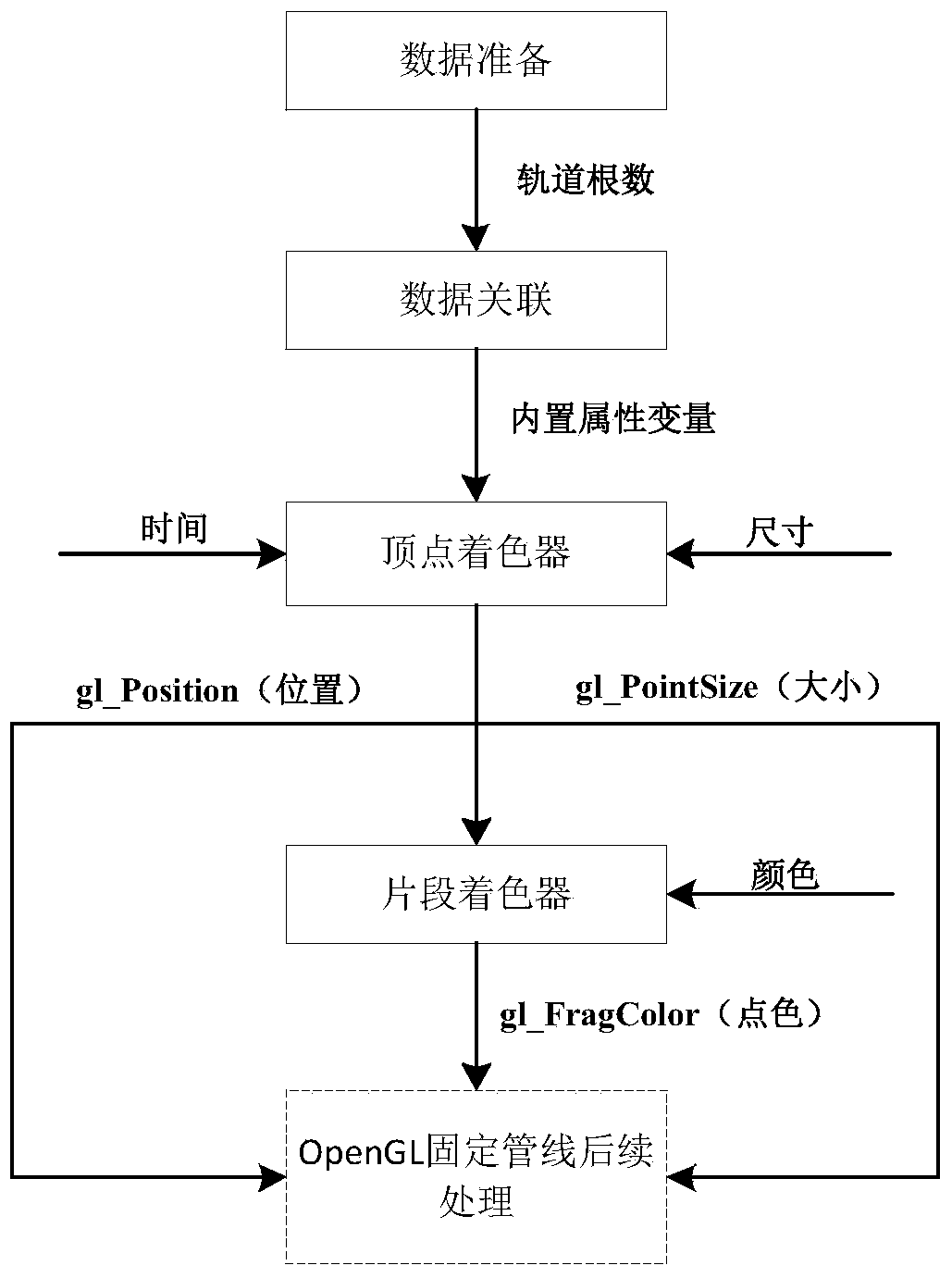

A space target real time simulation method

ActiveCN103679780AThe acceleration effect is obviousImprove real-time performanceAnimationReal-time simulationSky

The invention relates to a space target real time simulation method, and belongs to the technical field of spaceflight simulation. According to the method, firstly, a visualized star sky background is constructed; then through the combination with orbital elements of space targets, and via a programmable processor, high speed resolving and drawing of positions, sizes and colors are completed; and finally, through the combination with viewpoint positions and user clipping information, generation of a space situation in a target direction is completed. According to the invention, characteristics of parallel processing and high precision floating point computing of a GPU is fully utilized; the acceleration effect is obvious; the real-time performance is good; and a reliable means is provided for real time simulation of the targets in space situation expression.

Owner:THE PLA INFORMATION ENG UNIV

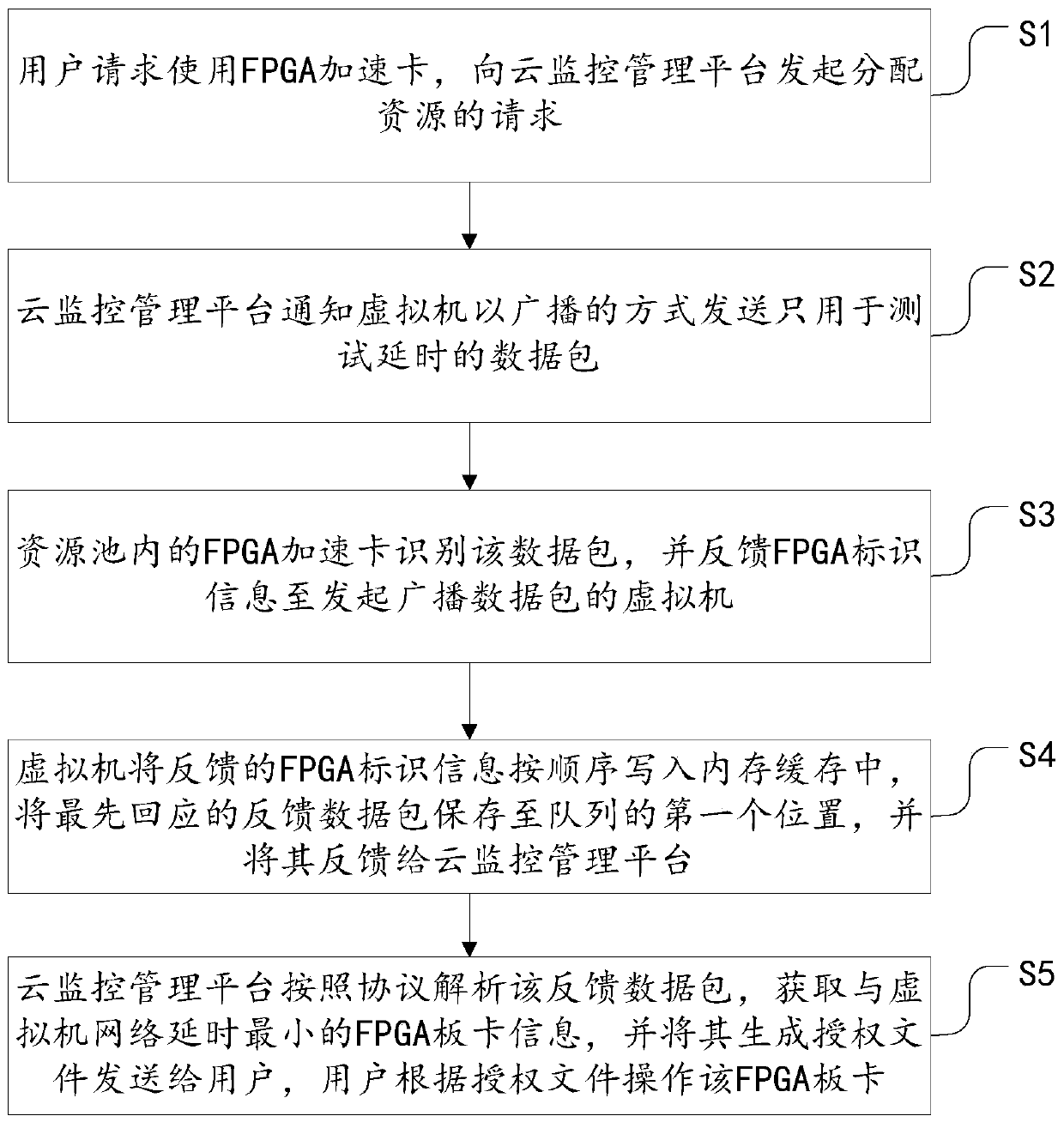

FPGA cloud platform acceleration resource allocation method and system

ActiveCN110618871AImprove experienceProtect effective rights and interestsResource allocationResource poolDistribution method

The invention provides an FPGA cloud platform acceleration resource allocation method and system. According to the invention, accelerator card resources are allocated and coordinated according to thetime delay between a user host and a FPGA accelerator card deployed in each network segment; when the user applies for using the FPGA, the FPGA acceleration card with the minimum delay with the host in the FPGA resource pool is allocated to the user, thereby realizing allocation of acceleration resources of the FPGA cloud platform; a cloud monitoring management platform can obtain the transmissiondelay with a virtual machine network according to different geographic positions of the FPGA board cards in the FPGA resource pool, , and can allocate the board card with the minimum delay to each user for use; in addition, unauthorized users can be effectively prevented from randomly accessing the acceleration resources in the resource pool, and the effective rights and interests of a resource pool owner are protected. According to the method and the device, the FPGA acceleration card which is not authorized to be used by the user is effectively protected, the network delay of the board cardallocated to the user can be ensured to be minimum, the optimal acceleration effect is achieved, and the user experience is improved.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

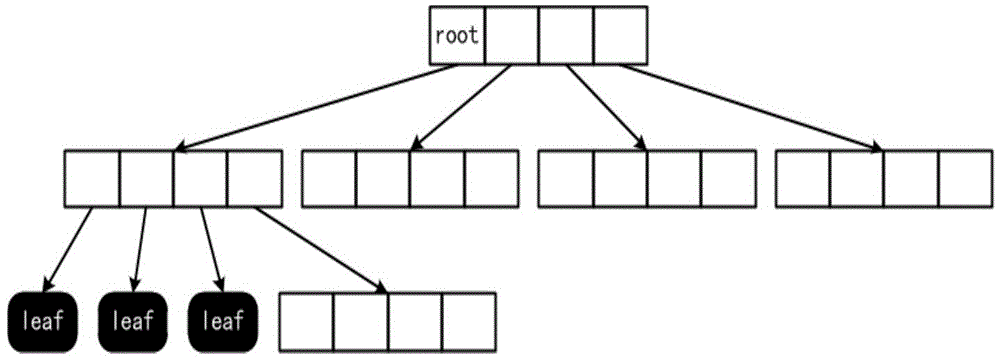

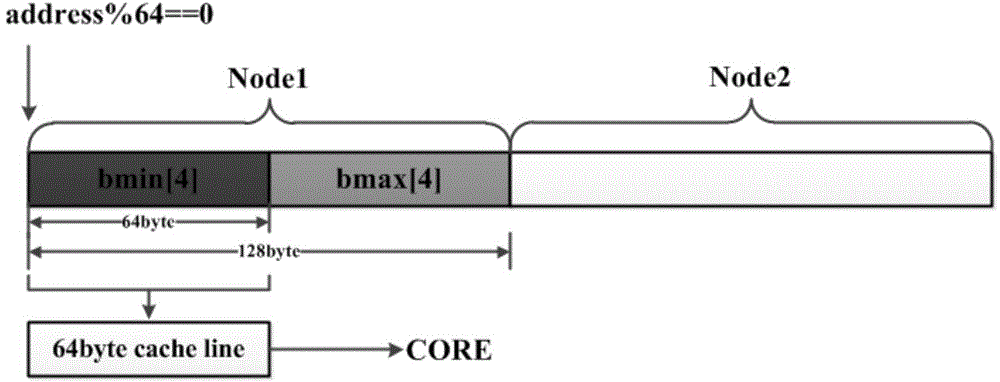

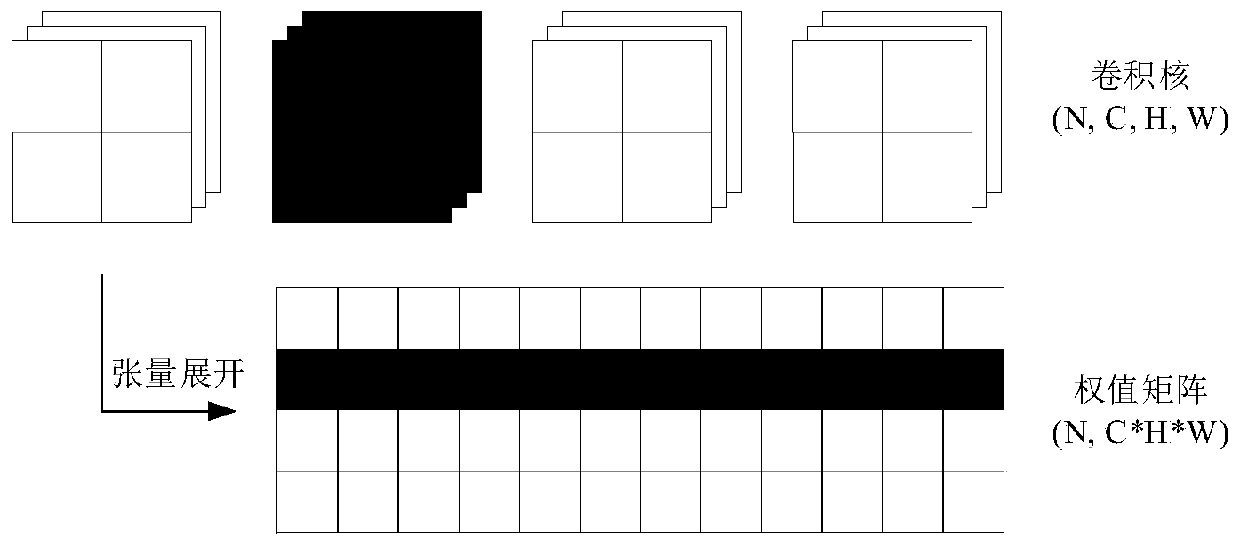

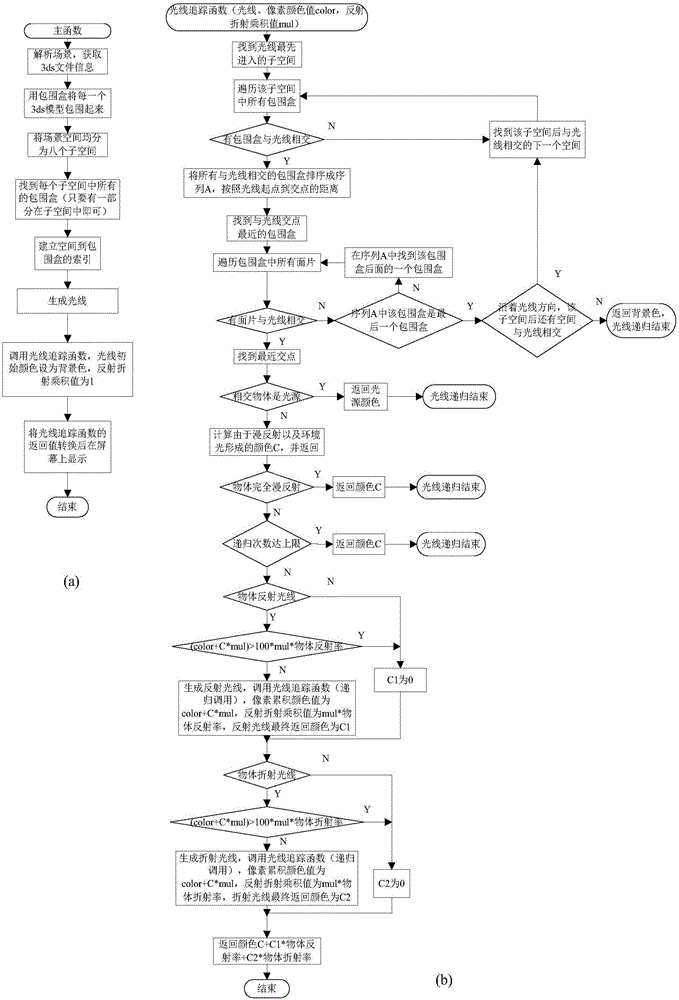

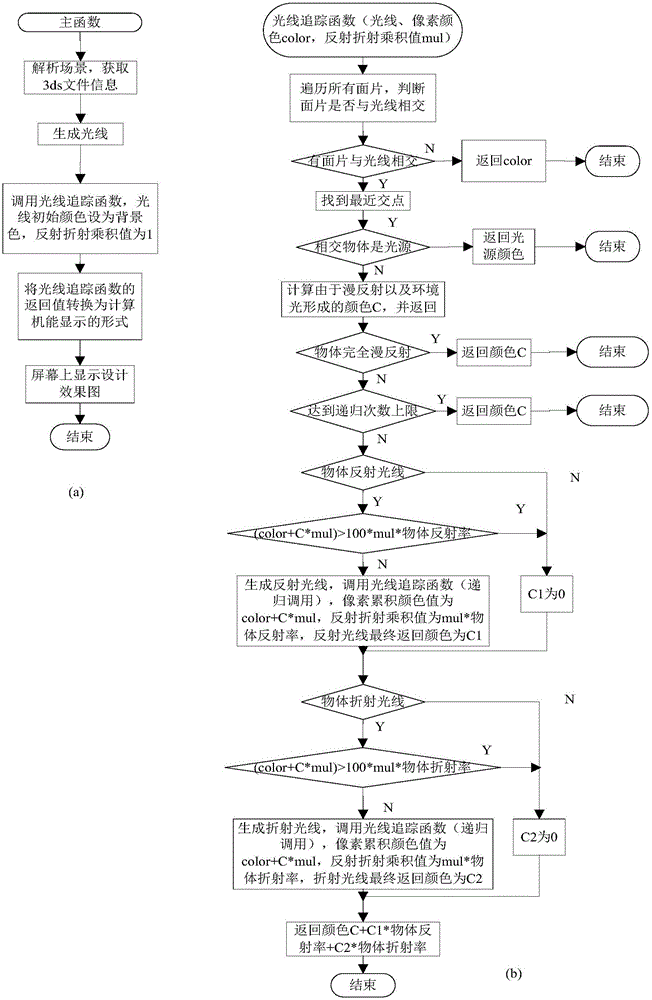

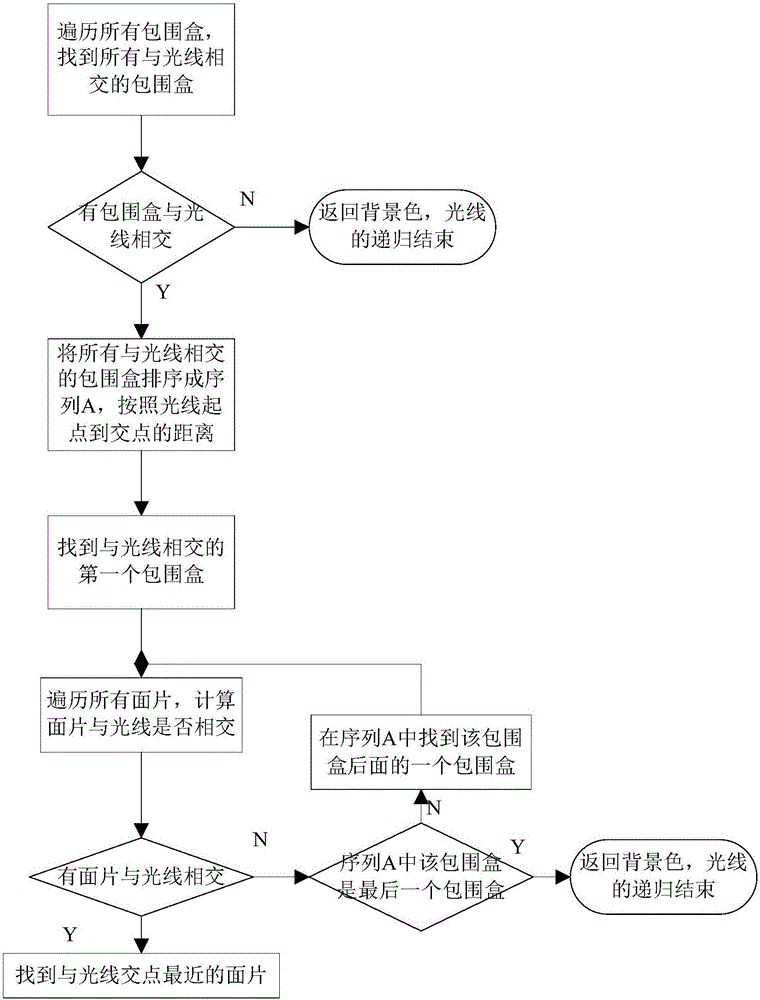

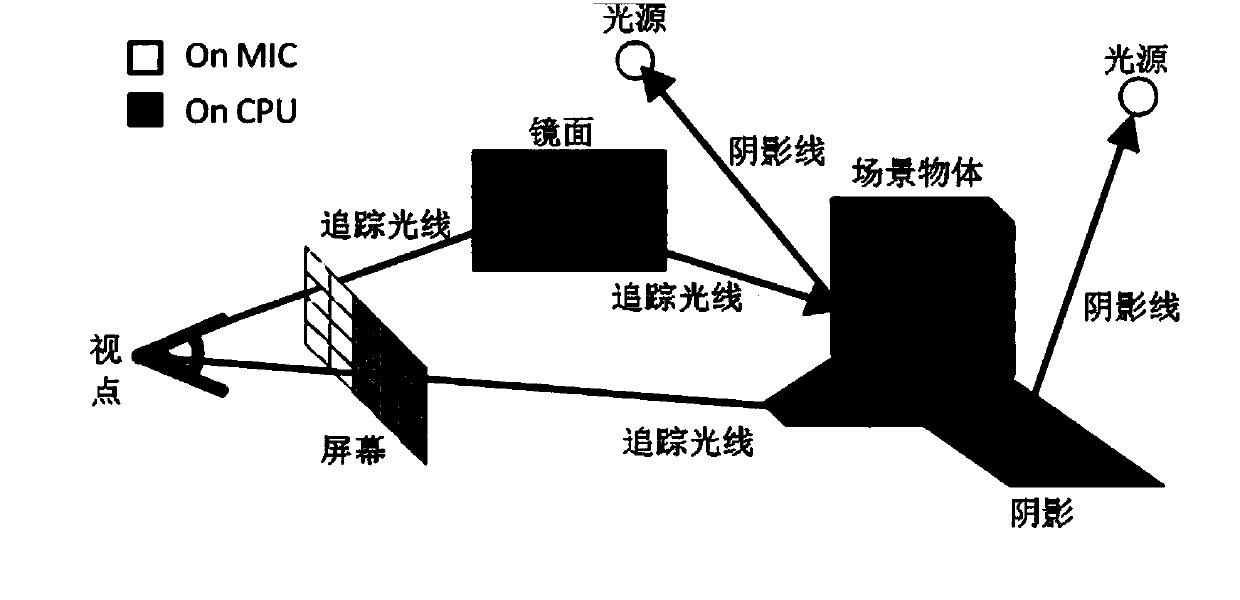

Light tracing parallel optimization method based on Intel many-core framework

ActiveCN104700447AAdapt to accessReduce the number of applicationsDigital computer detailsElectric digital data processingLight beamEngineering

The invention discloses a light tracing parallel optimization method based on an Intel many-core framework. The light tracing parallel optimization method based on the Intel many-core framework comprises the steps of 1, a spatial index BVH space acceleration structure for scene data is established; 2, primary light is generated, wherein a screen is divided into a plurality of screen subspaces according to the pixel and sampling is conducted, so that the primary light is generated; 3, light is traced, wherein the BVH space acceleration structure and scene geometric data are uploaded, communication between the Intel many-core framework and a CPU is conducted through asynchronous transmission, a plurality of sub-threads are started by a main thread, each sub-thread traces the primary light generated by each screen subspace according to the light beam, so that the point of intersection between each light ray and the scene is obtained; 4, the points of intersection are colored, wherein the points of intersection obtained during light tracking are colored, the step 2 is executed if secondary light is generated during coloring, the color of the primary light is obtained finally through coloring, and the light rays overlap on the screen, so that a final image is synthesized.

Owner:SHANDONG UNIV

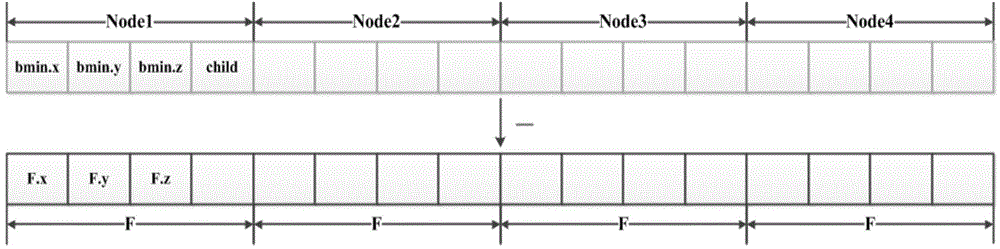

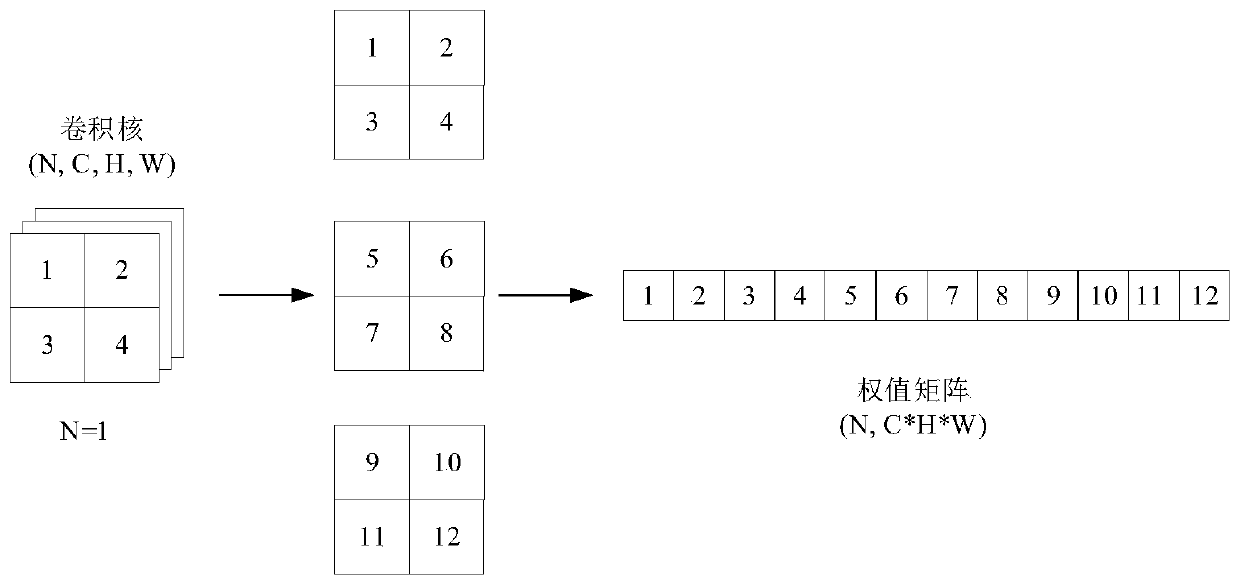

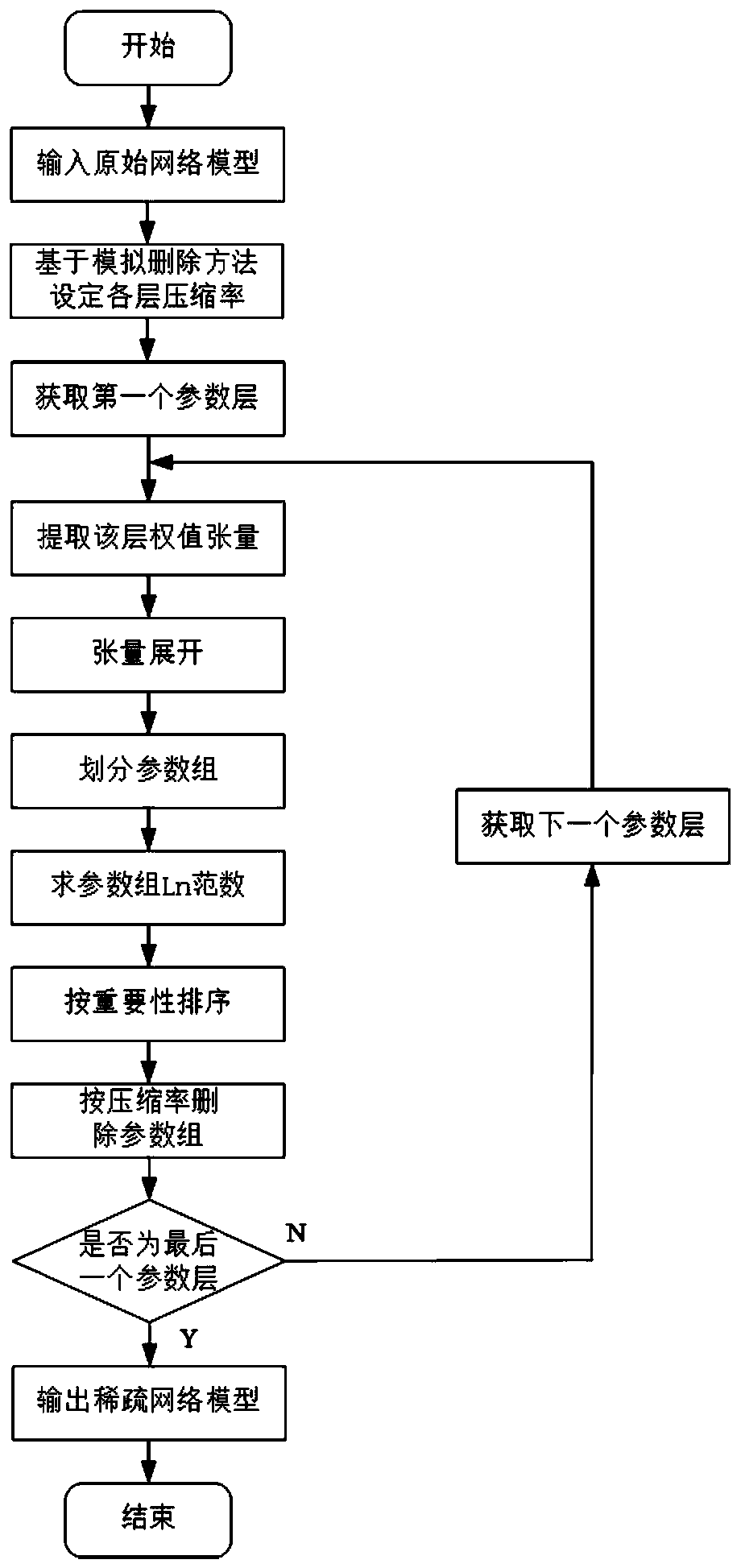

Neural network column sparse method based on weight saliency

InactiveCN110020724AAccurately achieve compression accelerationEfficient calculation of sparsity rateNeural architecturesPhysical realisationSparse methodsAlgorithm

The invention discloses a neural network column sparse method based on weight saliency. When the neural network model carries out feedforward operation, the four-dimensional weight tensor can be expanded into a two-dimensional matrix in a tensor expansion mode, and therefore convolution operation is converted into matrix multiplication. Therefore, on the basis of a tensor expansion operation mode,the invention discloses a method for carrying out column sparsity on a weight matrix, namely deleting columns of the weight matrix in a neural network parameter layer to obtain a sparse model, and the dimension of the operation matrix is reduced at the moment, thereby reducing the model scale of the neural network and accelerating the operation of the neural network. Network re-training is performed on the remaining weight parameters to callback the accuracy, and re-training is stopped when the accuracy of the model is not increased any more to obtain a final model. According to the method, the deep learning model can be deployed on mobile and embedded equipment, a certain actual acceleration effect is obtained, and the application of an intelligent algorithm on a mobile terminal is promoted.

Owner:ZHEJIANG UNIV

Acceleration method of ray tracing algorithm in home decoration design software

ActiveCN105117533AAvoid intersection calculationsEasy to implementSpecial data processing applications3D-image renderingDesign softwareLower grade

The invention discloses an acceleration method of a ray tracing algorithm in home decoration design software. The optimization of the ray tracing algorithm and the hardware acceleration of a GPU (Graphics Processing Unit) are combined, the optimized ray tracing algorithm is realized through CUDA (Compute Unified Device Architecture) programming, the ray tracking algorithm based on CUDA acceleration is realized on the high-grade GPU which supports recursion and the low-grade GPU which does not support the recursion, and the software and hardware combination of the optimization of the algorithm and hardware acceleration of the GPU is used for accelerating the rendering of the ray tracking algorithm. The acceleration method fully performs the advantages of a bounding box algorithm and a space subdivision algorithm, solves the blindness problem of ray and bounding box traversal, is simple, is obvious in acceleration effect, is simple in implementation, avoids a phenomenon that a great quantity of data is transmitted between a CPU (Central Processing Unit) and the GPU, fully utilizes the own memory of the GPU, and provides a superexcellent implementation scheme for the algorithms including the ray tracking algorithm and the like which operate on the CUDA and need recursion.

Owner:常州赞云软件科技有限公司

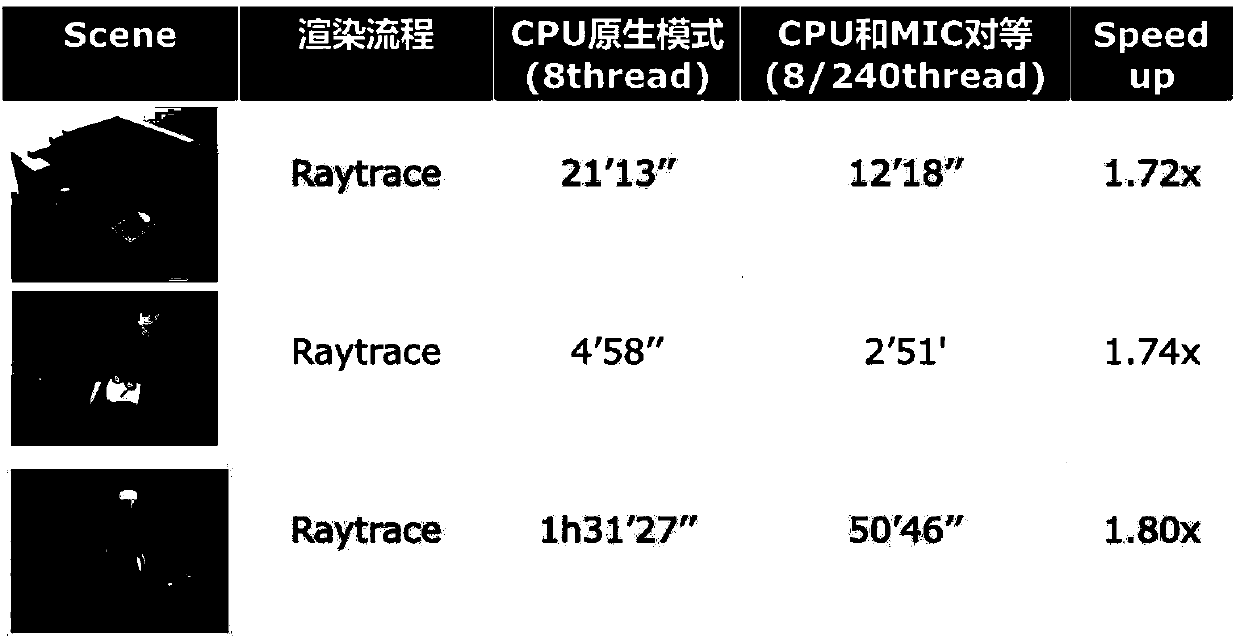

Light ray tracing acceleration method based on Intel multiple core framework peer mode

The invention discloses a light ray tracing acceleration method based on an Intel multiple core framework peer mode. The light ray tracing acceleration method based on the Intel multiple core framework peer mode includes steps: estimating a proportional relation between CPU (central processing unit) computing ability and MIC (many integrated core) computing ability; partitioning respective task loads of a CPU and MICs, and setting tasks of rendering processes of a CPU end and multiple MIC ends; using the peer mode to render assigned screen partitioning areas; starting multiple threads to process renderings of the screen partitioning areas; transmitting a rendering result to the CPU through the MICs after the rendering tasks are finished, and synthesizing a final image in the charge of the CPU. The light ray tracing acceleration method based on the Intel multiple core framework peer mode has the advantages of being large in parallel granularity, high in robustness, high in reproducibility, and independent of a concrete light ray tracing implementation detail method. Furthermore, the numbers of MIC nodes and CPU nodes are theoretically infinite large, and acceleration effects are obvious due to the fact that no computing resource is wasted on all the nodes.

Owner:SHANDONG UNIV

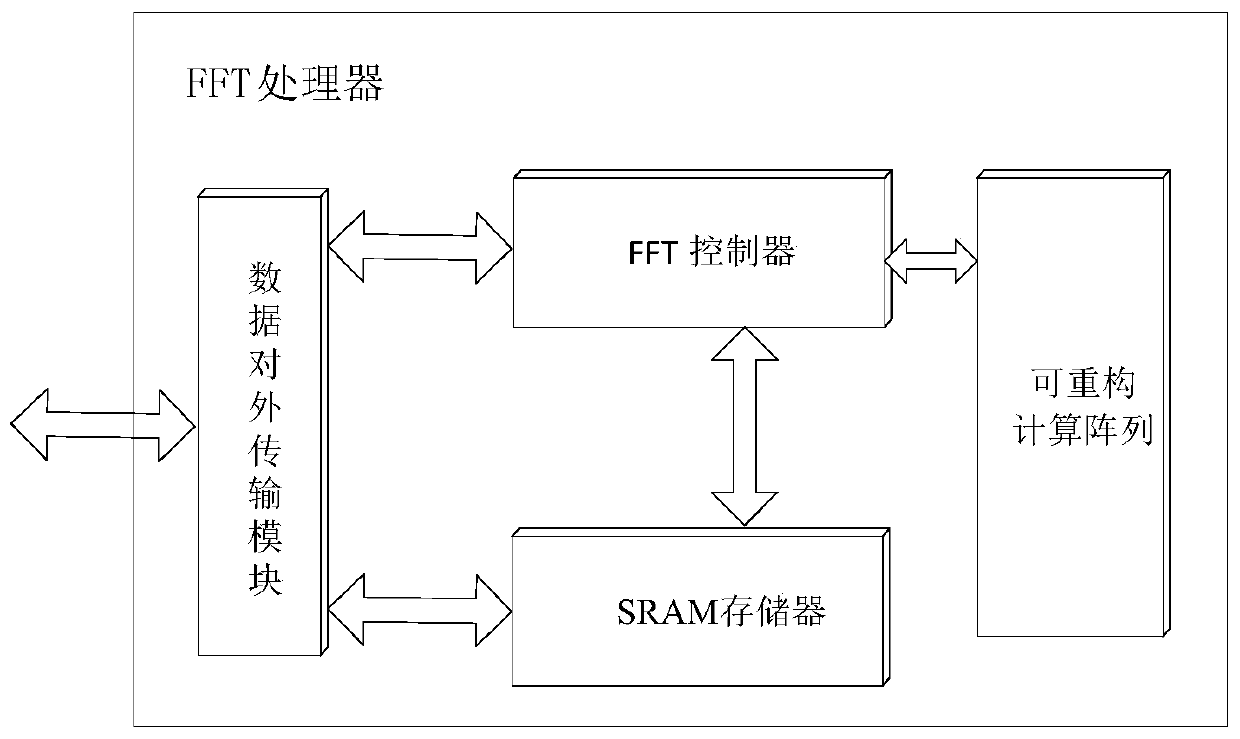

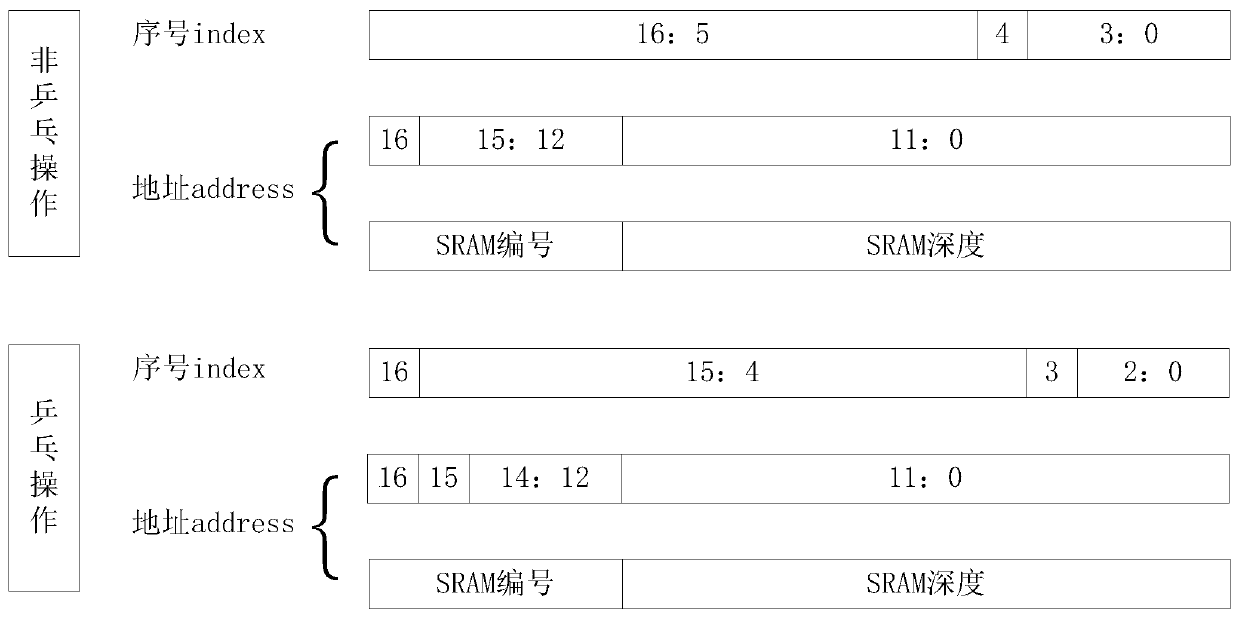

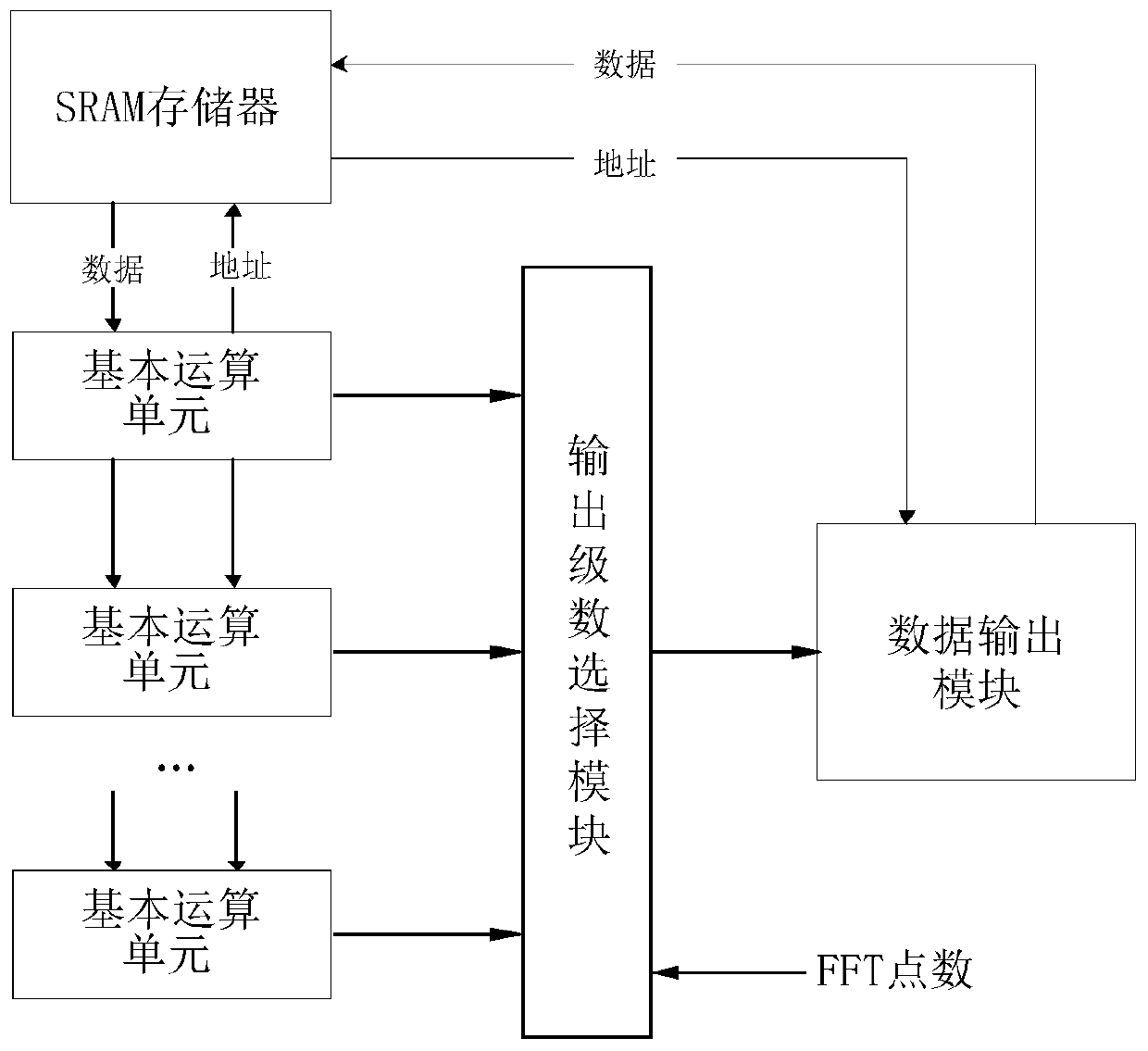

A reconfigurable FFT processor supporting multi-mode configuration

ActiveCN109977347AImprove resource utilizationImprove operation accuracyDigital data processing detailsEnergy efficient computingResource utilizationFft processor

A reconfigurable FFT processor supporting multi-mode configuration comprises an on-chip SRAM memory which communicates with an off-chip memory through a data external transmission module; a reconfigurable computing array which comprises a plurality of single-precision floating point adders based on the IEEE-754 standard, the subtracters and the floating point multipliers; an FFT controller which is used for controlling the whole flow of the FFT operation; and the data external transmission module which is used for controlling the data transmission between the processor and the off-chip memory.The beneficial effects are that the processor has the high operation precision, obvious acceleration effect and high utilization rate of hardware resources.

Owner:NANJING UNIV

Method for carrying out parallel simulation by repeatedly switching a plurality of operation modes of simulator

ActiveCN101799767AThe acceleration effect is obviousImprove parallel efficiencyMultiprogramming arrangementsSoftware simulation/interpretation/emulationPerformance indexOperation mode

The invention discloses a method for carrying out parallel simulation by repeatedly switching a plurality of operation modes of a simulator, and aims at reducing the loss of simulation precision and the simulation time. The technical scheme of the invention is as follows: a host computer software and hardware platform of an operation simulator is constructed, a server node is provided with a control software of a server-side, and a simulation node is provided with a control software of a client; the control software of the server-side carries out global configuration and initialization on thenodes participating in the parallel simulation; the server node and the simulation node are performed with communication initialization; the control software of the client operates the simulator on the simulation node; the simulation nodes parallelly simulate the same Benchmark program in the three modes, namely functional simulation, detailed pre-heating and detailed simulation; and the control software of the client monitors the changes of a local performance index file and a status file, acquires the operation information and sends the information to the server nodes, and the server node receives the information and correspondingly processes to obtain a simulation result. The invention has obvious accelerated effect, high parallel efficiency, and small precision loss.

Owner:NAT UNIV OF DEFENSE TECH

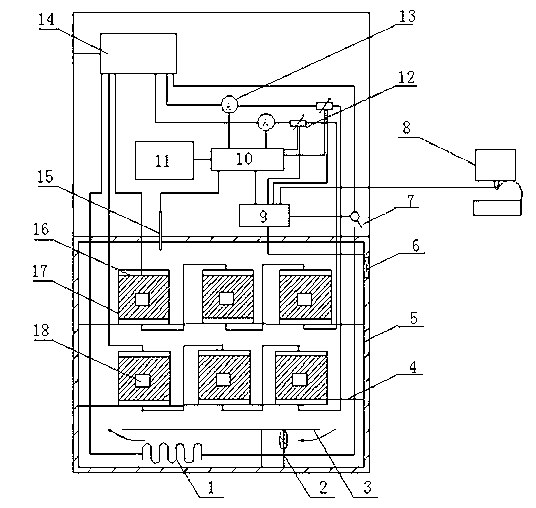

Soil corrosivity accelerated test method and device

ActiveCN103257105AThe acceleration effect is obviousWeather/light/corrosion resistanceProgramme control in sequence/logic controllersSignal onCorrosion

The invention discloses a soil corrosivity accelerated test method and device. The device comprises a rectifier (14), three soil boxes (17), a heater (1), a temperature sensor (15), an information acquisition system (10), an LED (light-emitting diode) display screen (11), a PLC (programmable logic controller) control module (9) and a computer (8), wherein the soil boxes (17) in which metal test pieces (18) and graphite sheets (16) are arranged are directly connected with the rectifier (14), ammeters (13) and resistors (12), and the three soil boxes are connected in serial in a group and then placed on a same layer of a support (4) of a lower layer test region of a test box; the heater (1), an electromagnetic switch (7) and the rectifier (14) can form a loop, and the information acquisition system (10) can receive signals of the ammeters (13), the resistors (12) and the temperature sensor (15) and can display signals on the LED display screen (11) through a digital form; and the PLC control module (9), the information acquisition system (10), the resistors (12), the electromagnetic switch (7) and the computer (8) are connected. The soil corrosivity accelerated test method and device provided by the invention can both consider soil macro and microcosmic factors when a soil corrosion accelerated test is performed, so that in the accelerated test, measures the proper corrosivity of soil, close to erosion data, can be measured, and the soil corrosivity accelerated test method and device provided by the invention has the characteristics that the device is simple in structure, is high in efficiency and favorable.

Owner:ELECTRIC POWER RES INST STATE GRID JIANGXI ELECTRIC POWER CO +2

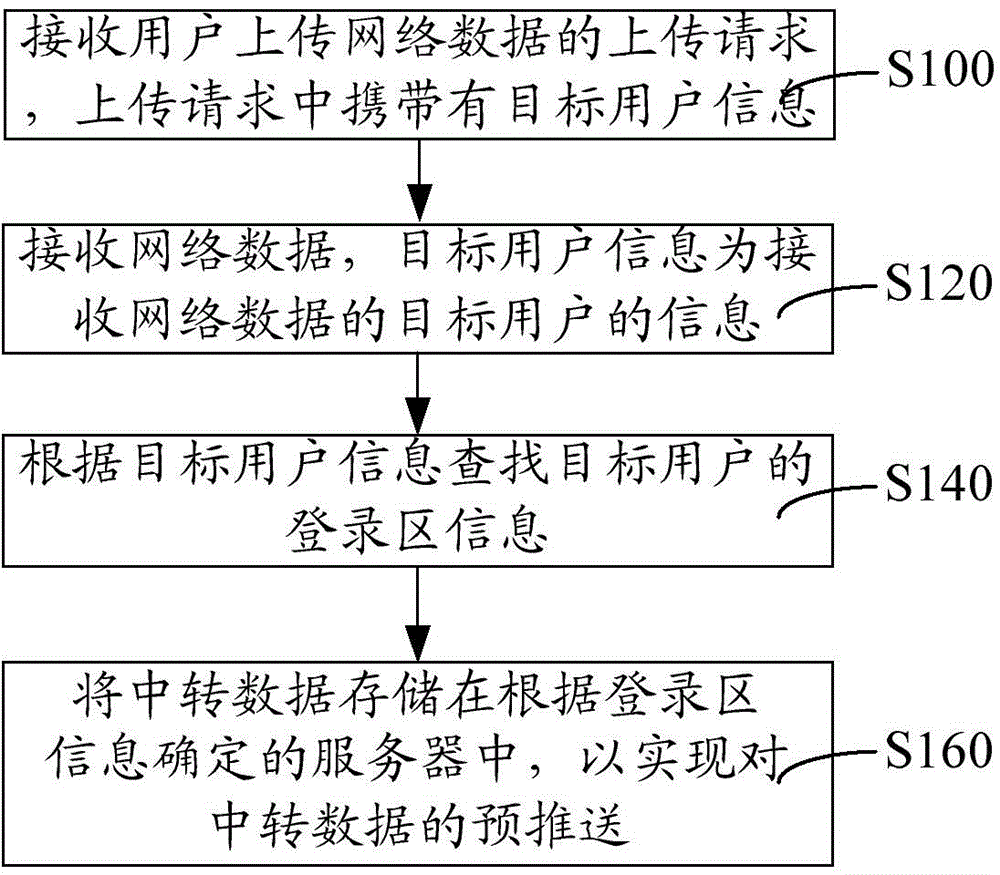

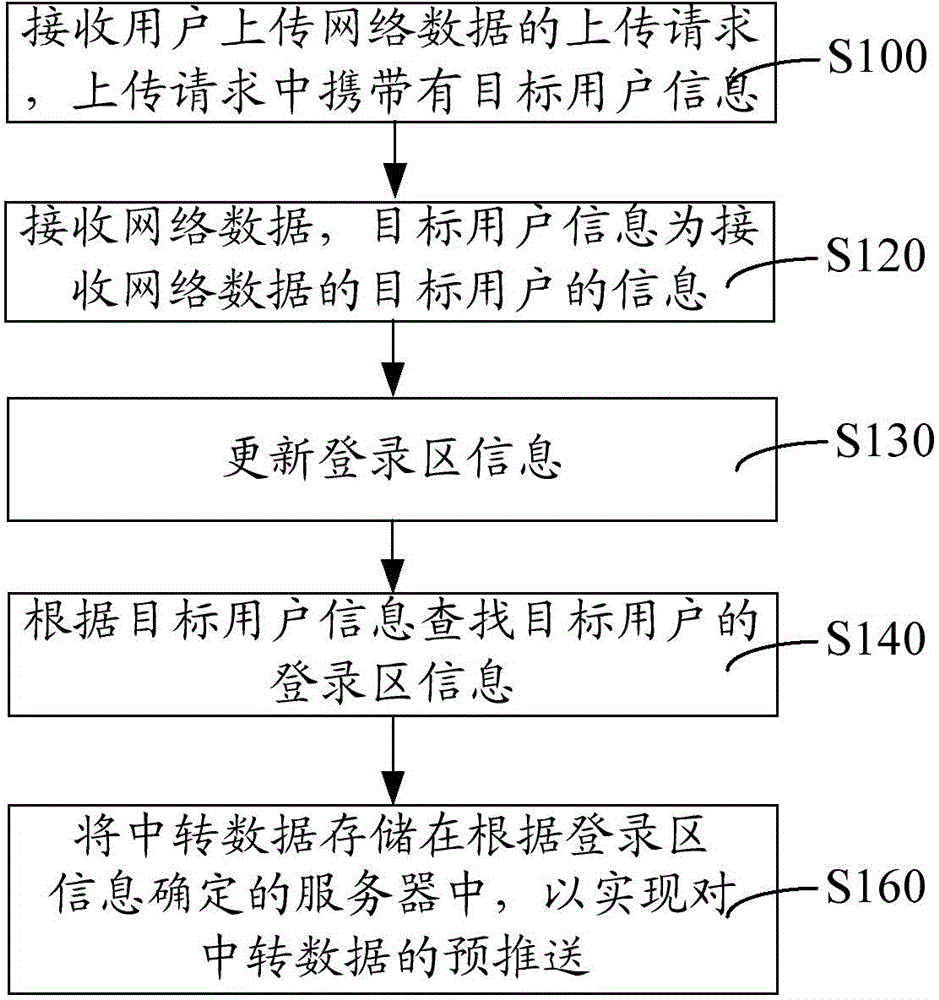

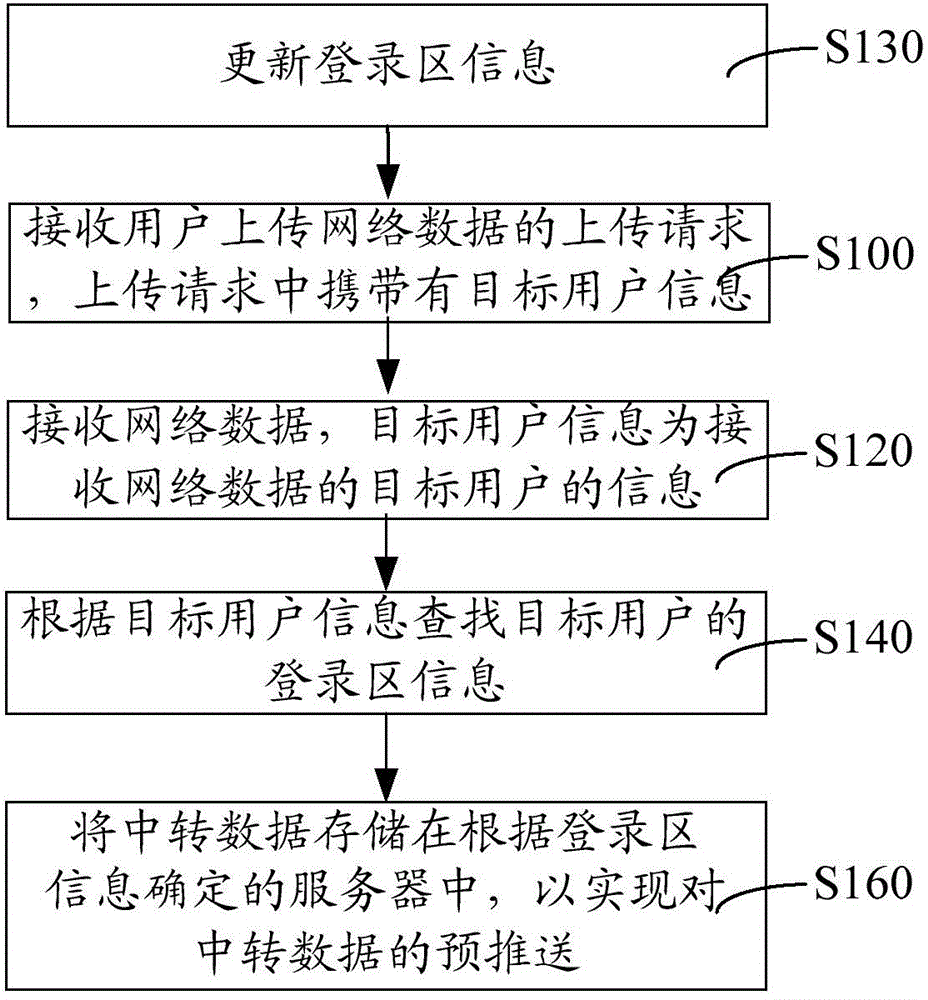

Information pushing method, device and system, as well as information access device

The invention discloses an information pushing method which comprises the following steps of receiving an uploading request of uploading network data from a user, wherein carrying target user information in an uploading request; receiving the network data; searching for the login area information of a target user according to the target user information; storing the network data in a server determined according to the login area information to pre-push the network data. According to the information pushing method, the network data, such as a picture, uploaded by the user, is pushed into the server determined according to the login area information of the target user in advance, and the target user logging in the server before highly possibly logs in the server again, so that the hit rate during downloading can be increased; when the target user makes a request of downloading the picture on the server, the network data can be directly provided by the server, so that time for acquiring the network data from another server is saved, and obvious acceleration effects are achieved. In addition, the invention further provides an information pushing device, an information access device and an information pushing system.

Owner:SHENZHEN TENCENT COMP SYST CO LTD

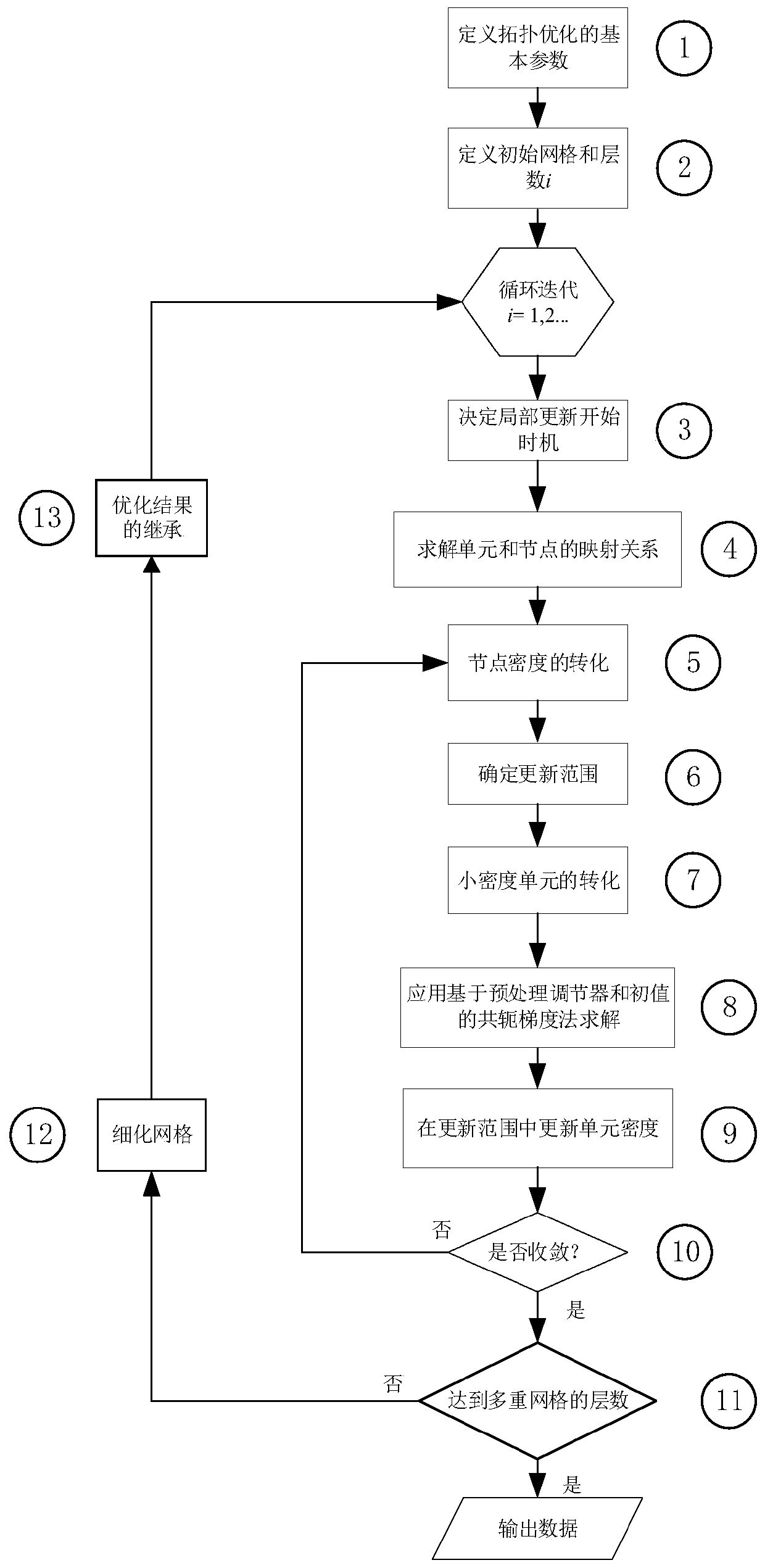

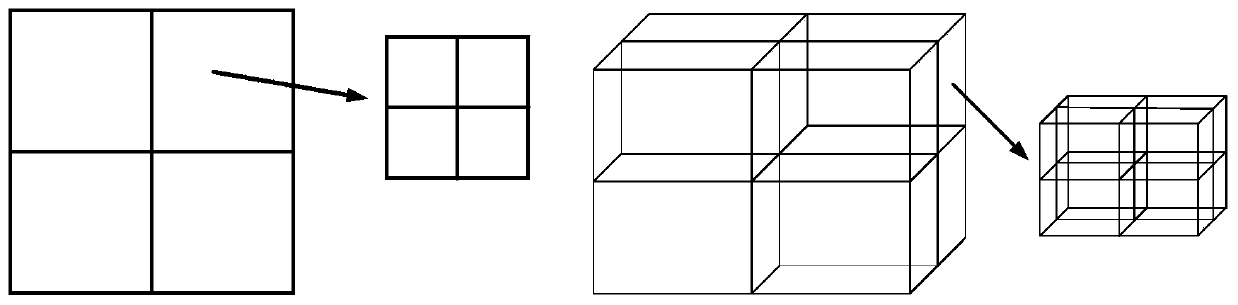

A triple acceleration topology optimization method

ActiveCN109840348AImprove acceleration performanceThe acceleration effect is obviousSpecial data processing applicationsConjugate gradient methodComputer science

The invention discloses a triple acceleration topology optimization method. According to the invention, by improving three aspects of multi-grid density mapping, the conjugate gradient method based onpre-processing and an initial value, and local updating, a design domain is divided into a plurality of layers of grids with different thicknesses through multi-grid density mapping, topological solving is conducted on a coarse grid layer firstly, an obtained optimization result is mapped to a next layer of fine grid layer to serve as an initial value, a topological optimization process on the fine grid layer skips redundant iteration, and the topological optimization process is accelerated; According to the conjugate gradient method based on preprocessing and an initial value, a preprocessing regulator and the initial value are added to iterative solution of a topological optimization equation, and the solution speed is increased; in the local updating, an update unit is selected, and the number of unit updates during iteration is reduced to achieve an acceleration effect. Based on the method, triple acceleration of topological optimization is realized, the topological optimization process is remarkably accelerated, and an optimization result with high precision and low calculation cost is obtained.

Owner:SOUTH CHINA UNIV OF TECH

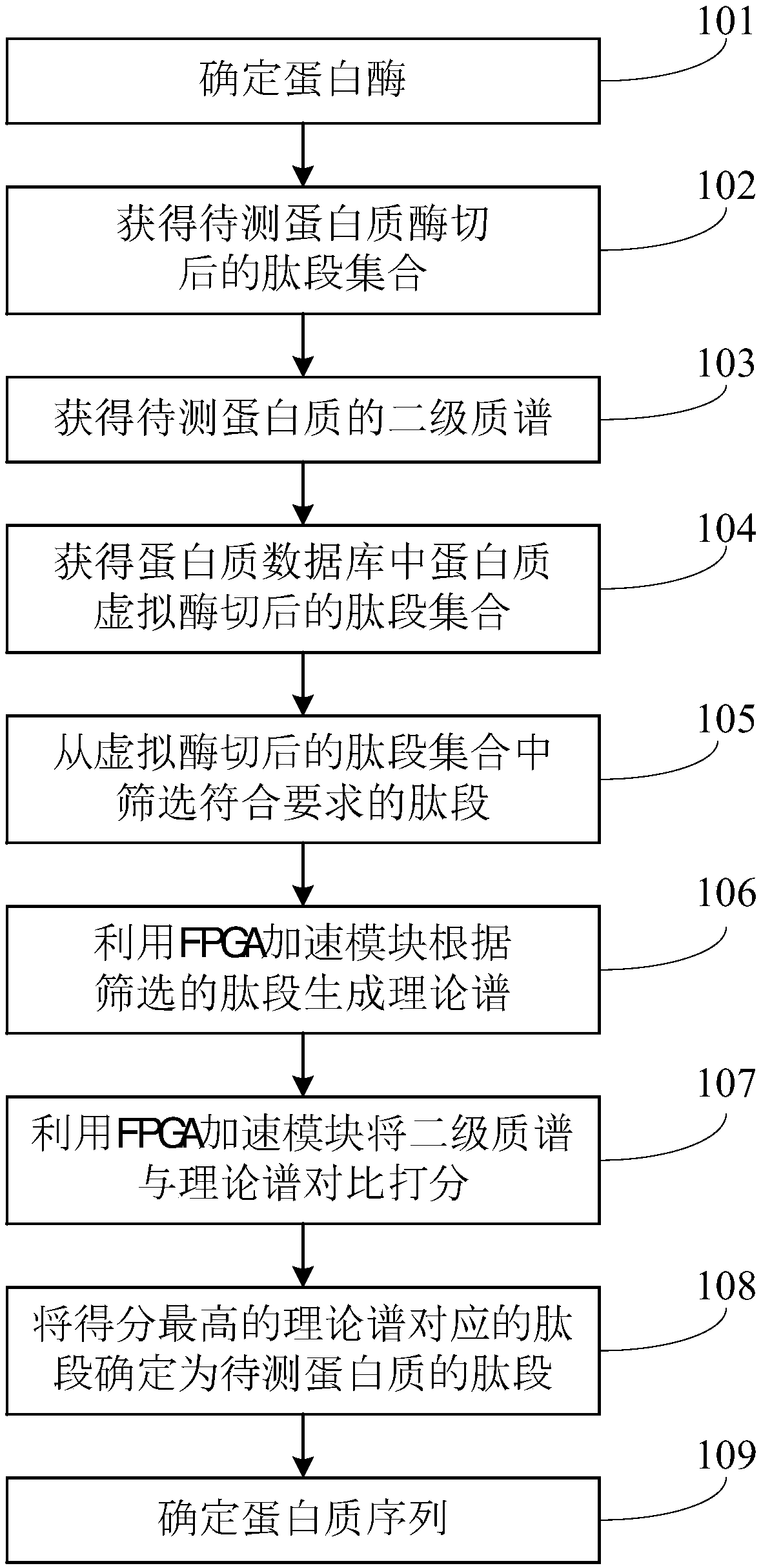

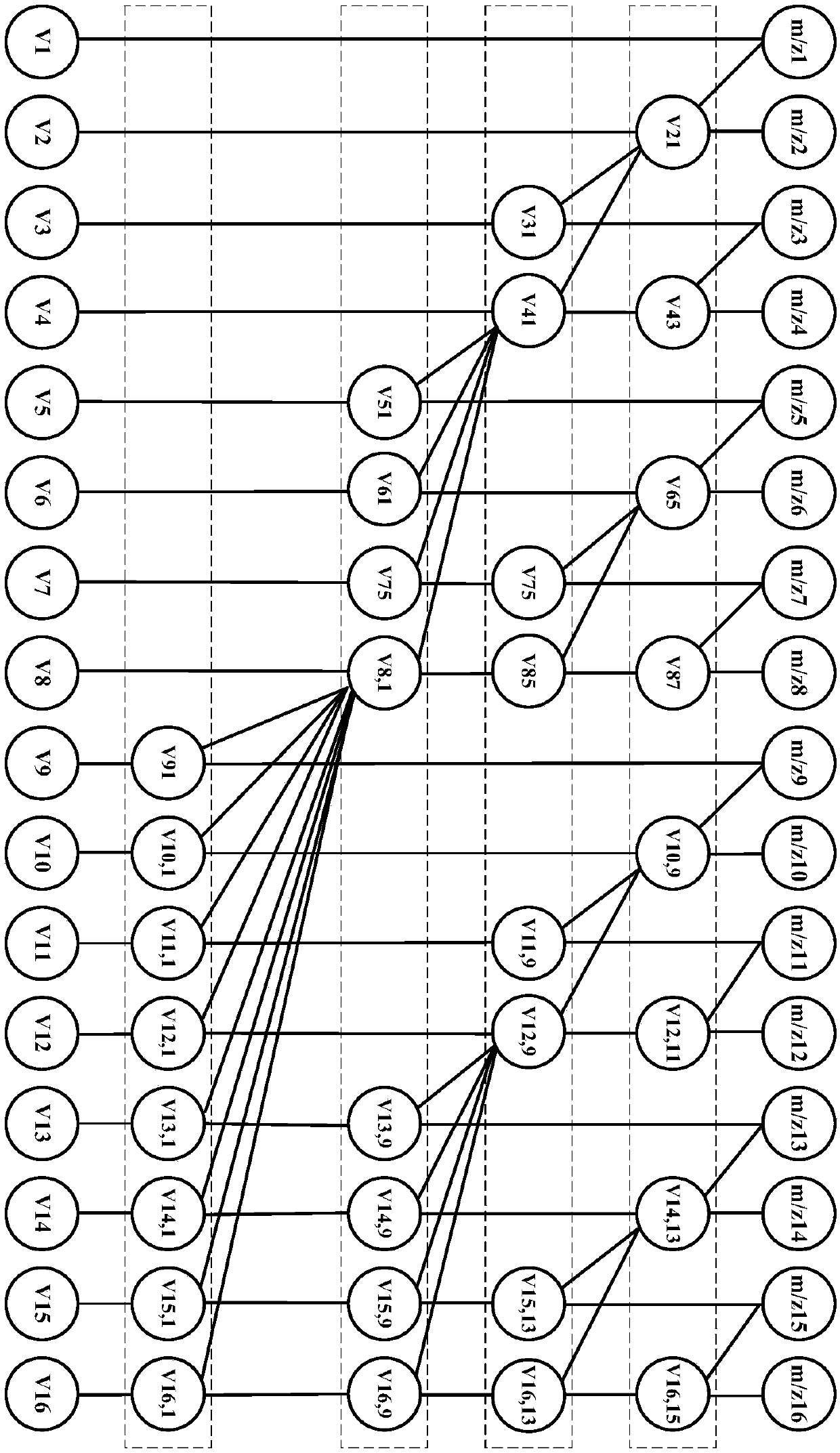

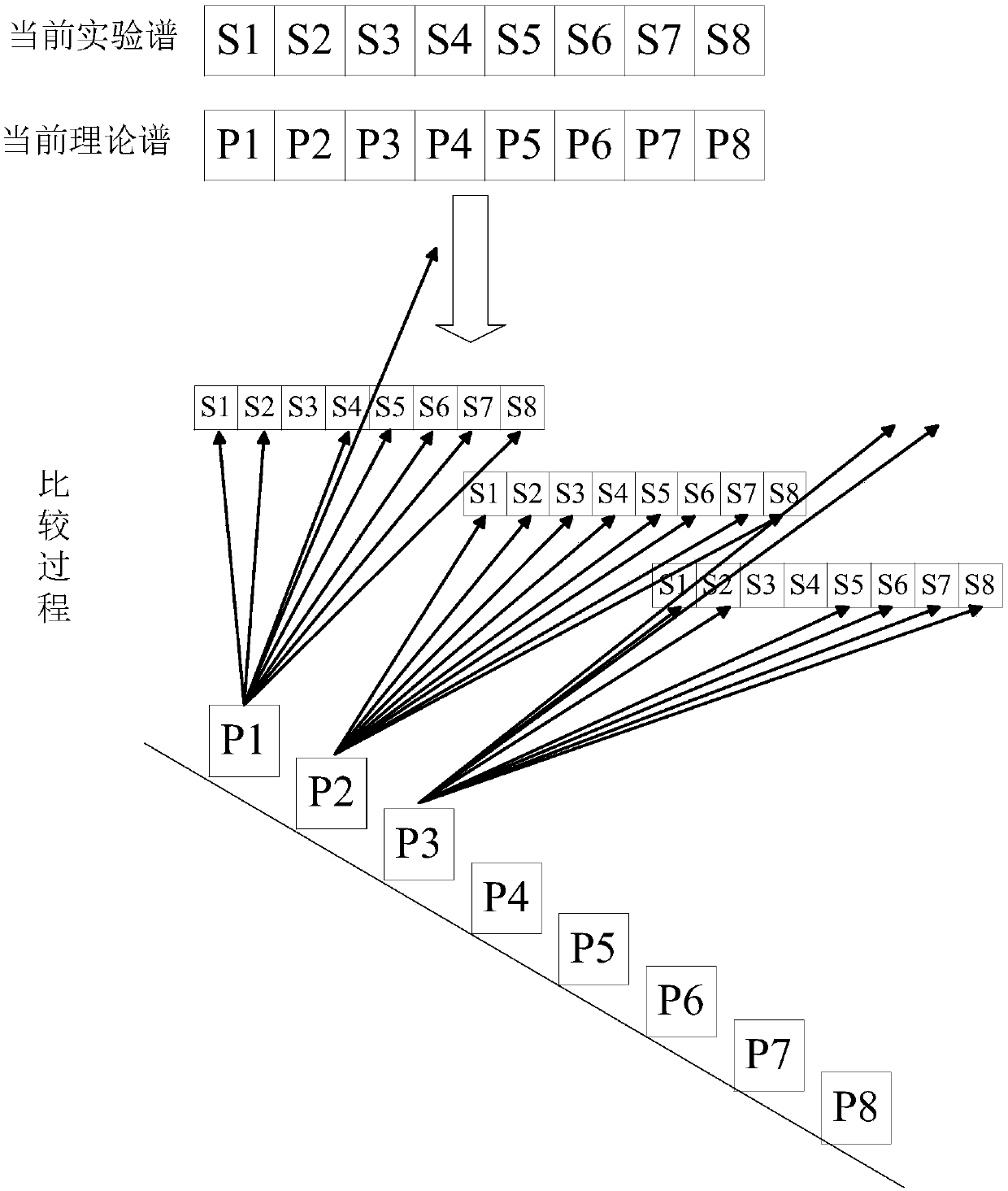

Protein identification method and system

ActiveCN107727727AThe acceleration effect is obviousComplete processMaterial analysis by electric/magnetic meansPeptide fragmentMass spectrometric

The invention belongs to the technical field of biological analysis and in particular discloses a protein identification method and a protein identification system. The protein identification method comprises the following steps: performing digestion operation on protein to be tested according to protease, and acquiring a secondary mass spectrum of the protein to be tested by using a protein tandem mass spectrum technique; performing virtual digestion operation on a protein sequence in a protein database, and extracting a first type of peptide fragments meeting requirements; generating a theoretic spectrum by using an FPGA (Field Programmable Gate Array) according to the first type of the peptide fragments; comparing the secondary mass spectrum of the protein to be tested with the theoretic spectrum by using an FPGA acceleration module, and performing similarity scoring; confirming a peptide fragment corresponding to a theoretic spectrum with a highest score as a peptide fragment of the protein; and sequentially confirming all peptide fragment sequences of the protein, thereby obtaining protein sequences. By adopting the protein identification method and the protein identificationsystem disclosed by the invention, acceleration on the FPGA is achieved, the whole scoring process is accelerated for about 25 times, a good acceleration effect is achieved, and the operation efficiency of the system is improved.

Owner:FUDAN UNIV

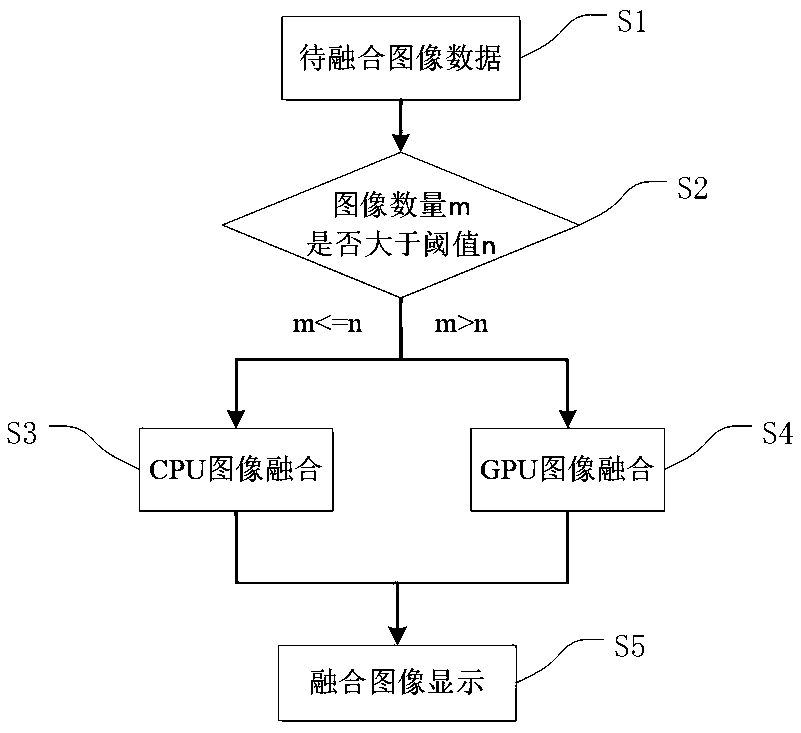

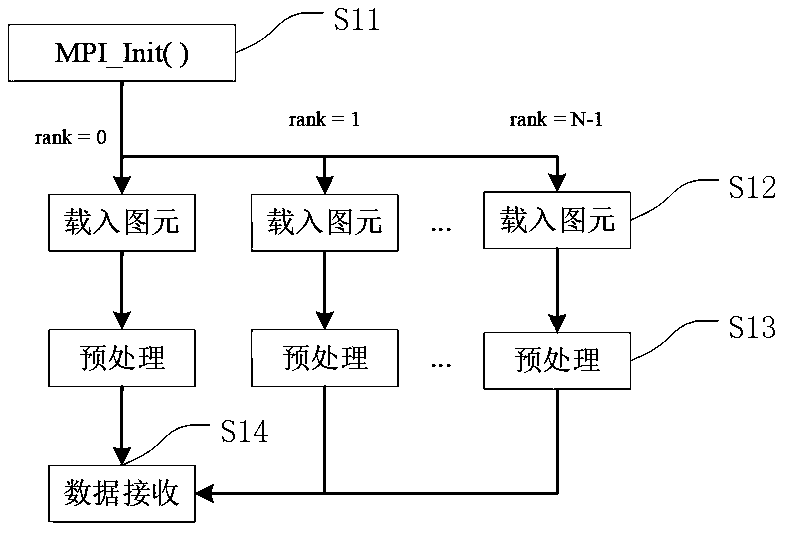

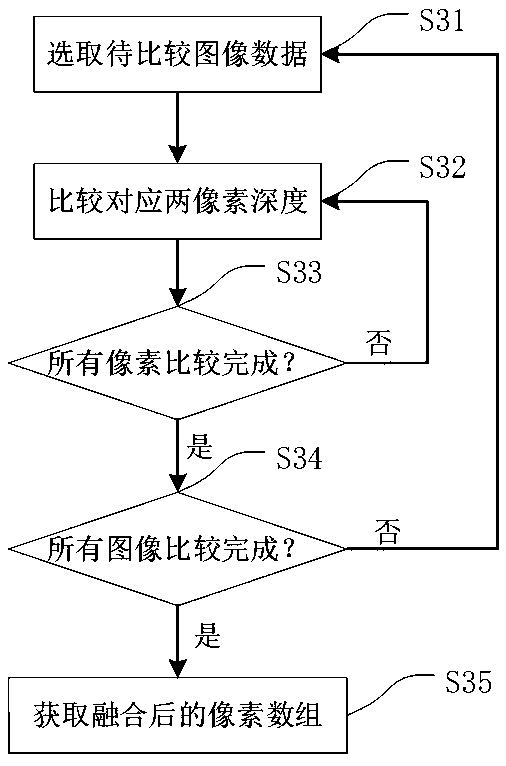

Massive urban space three-dimensional data cloud rendering image fusion method and system

ActiveCN111145331AImprove efficiencyAchieve completenessProcessor architectures/configuration3D-image renderingComputational physicsData cloud

The invention relates to the field of massive urban space three-dimensional data cloud rendering, in particular to a massive urban space three-dimensional data cloud rendering image fusion method anda massive urban space three-dimensional data cloud rendering image fusion system. The method is characterized by comprising the following steps of: S1, acquiring image data to be fused; S2, judging the number of images; S3, carrying out CPU image fusion; S4, carrying out GPU image fusion; and S5, completing the image fusion. According to the invention, the fusion efficiency of multiple images canbe greatly improved, and the rendering performance of a three-dimensional large-scale scene is further improved.

Owner:深圳市数字城市工程研究中心 +1

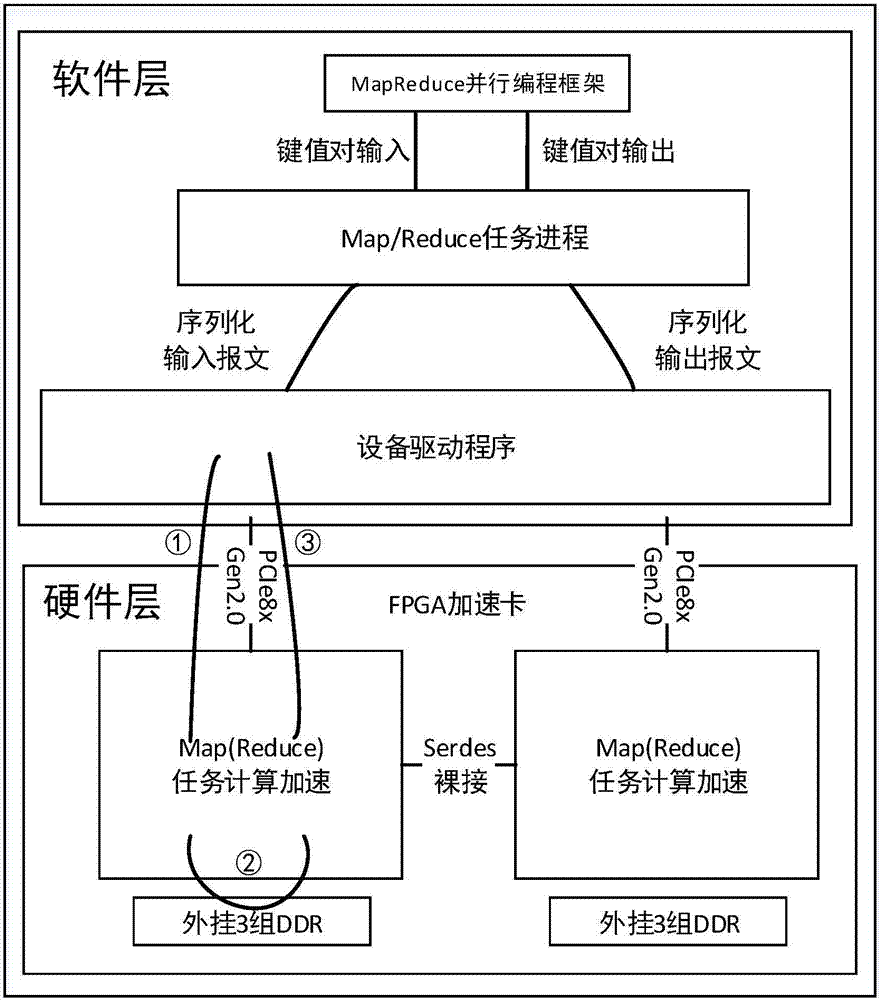

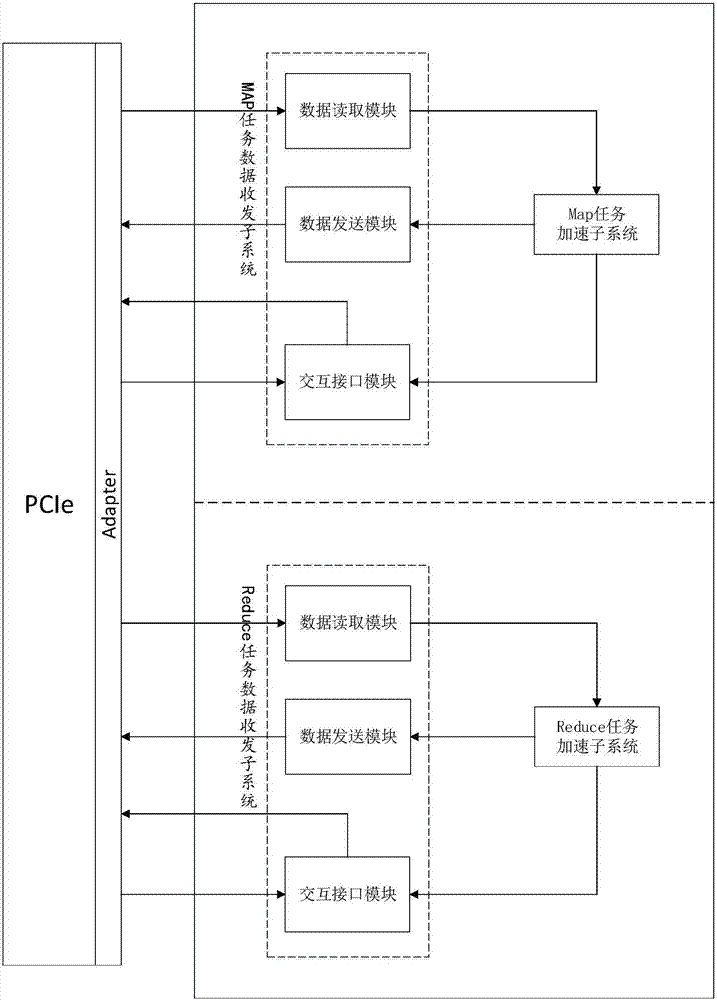

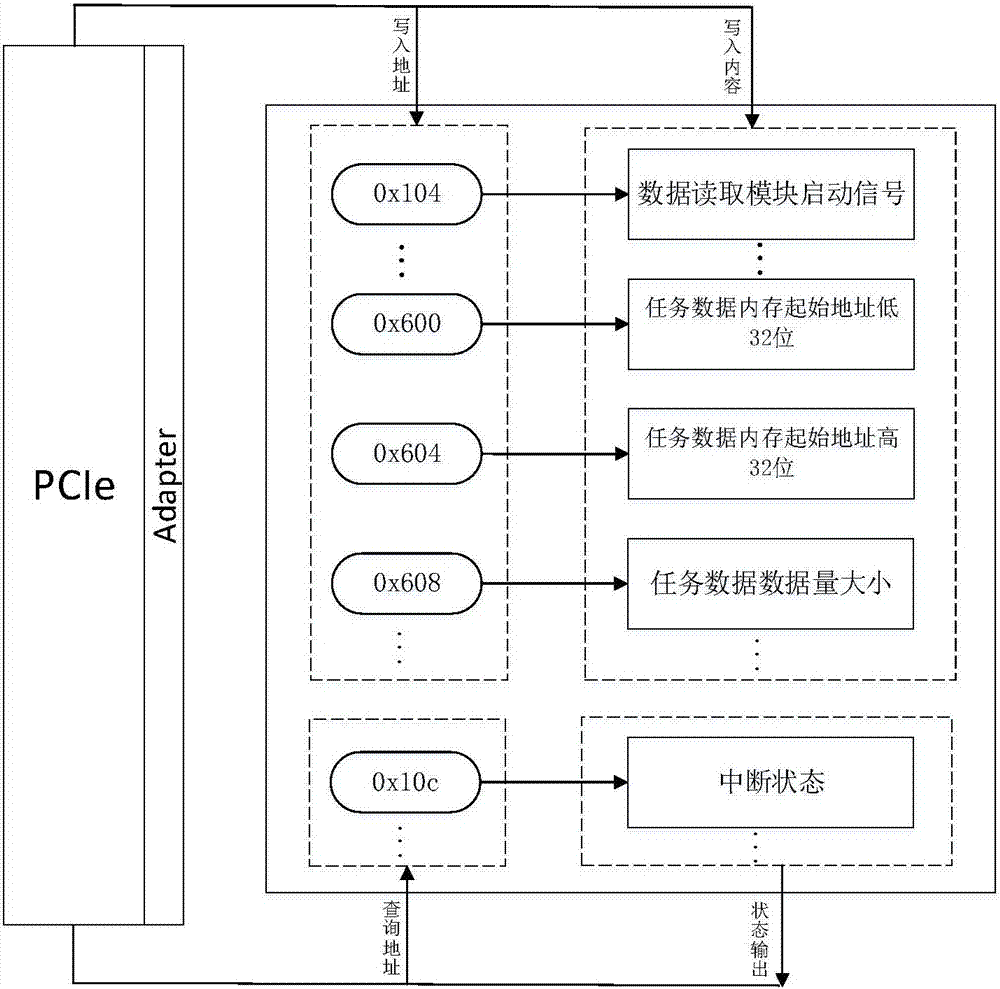

MapReduce-based K-means clustering algorithm FPGA acceleration system

InactiveCN107368375AReduce computational complexityReduce computing time overheadInterprogram communicationCharacter and pattern recognitionComputation processAssembly line

The invention provides a MapReduce-based K-means clustering algorithm FPGA acceleration system. The acceleration system mainly comprises a Map task data receiving and transmitting subsystem, a Map task acceleration subsystem, a Reduce task data receiving and transmitting subsystem and a Reduce task acceleration subsystem, wherein the Map task data receiving and transmitting subsystem transmits corresponding data from a PCIe terminal to the Map task acceleration subsystem and transmits a final calculation result of the Map task acceleration subsystem back to the PCIe terminal; and the Reduce task data receiving and transmitting subsystem transmits corresponding data from the PCIe terminal to the Reduce task acceleration subsystem and transmits a final calculation result of the Reduce task acceleration subsystem back to the PCIe terminal. According to the acceleration system, a time consumption calculation process needing to be performed is separated out of an upper layer, a special hardware system is adopted to perform corresponding calculation, and assembly line design and a concurrent processing method are adopted for all modules in the system, so that operation processing speed is greatly increased.

Owner:HUAZHONG UNIV OF SCI & TECH

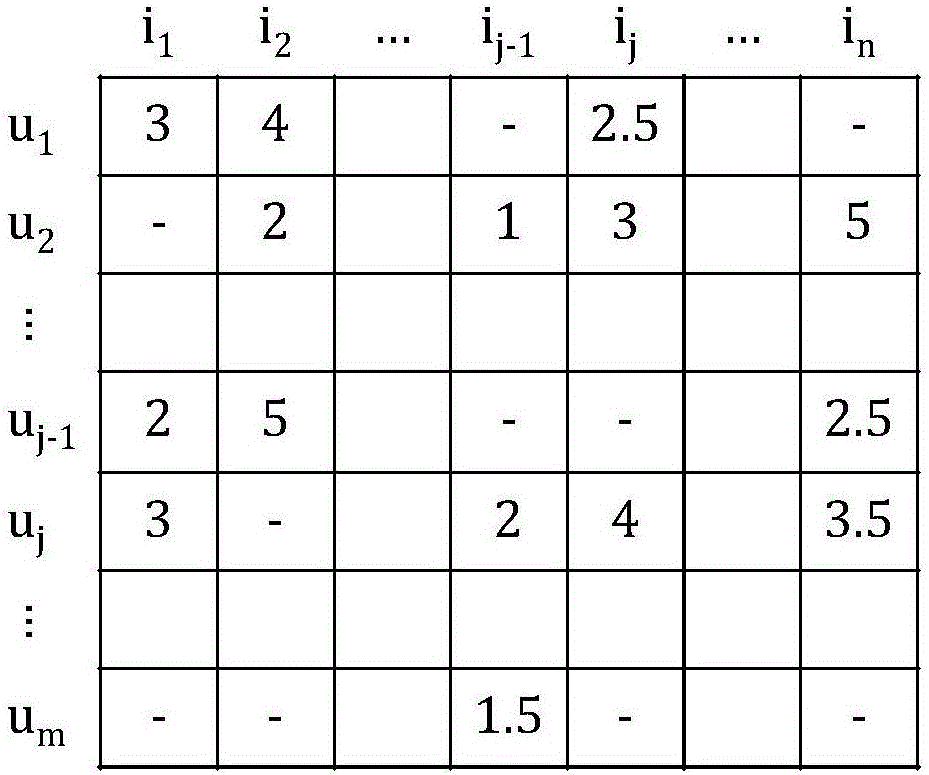

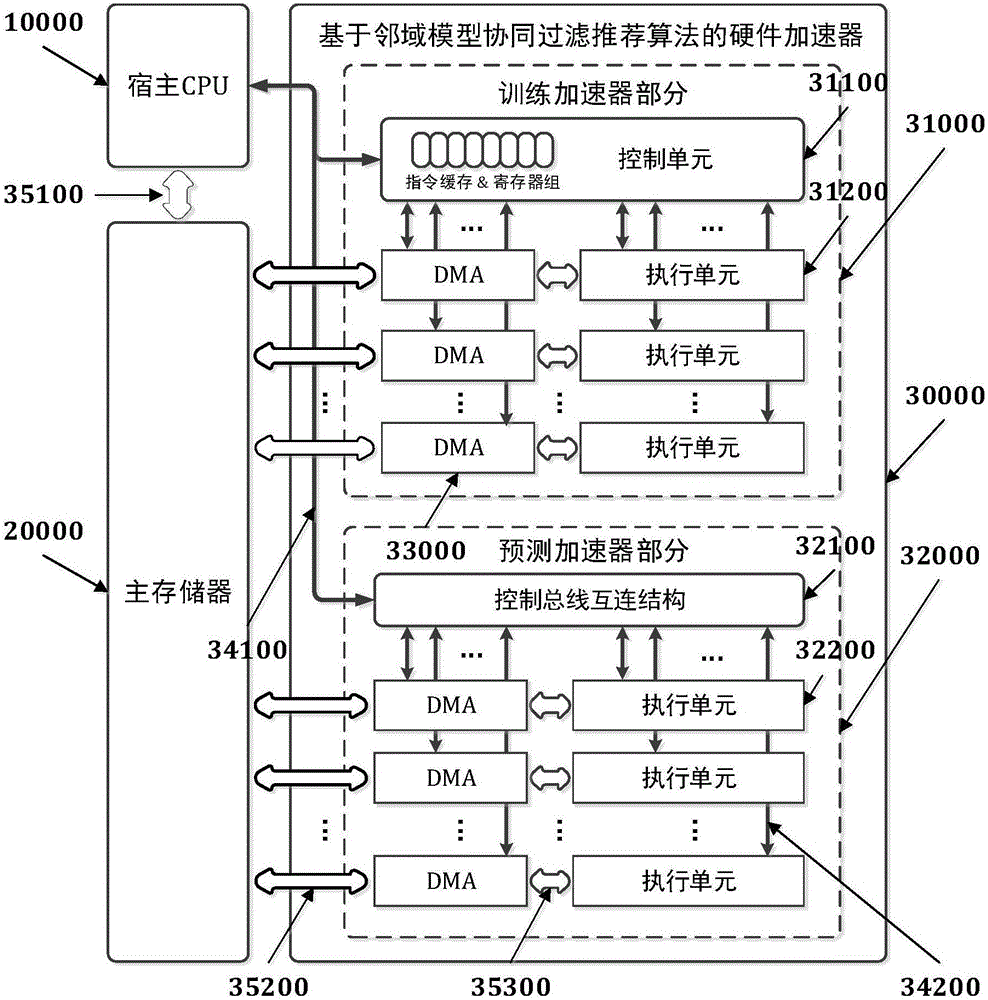

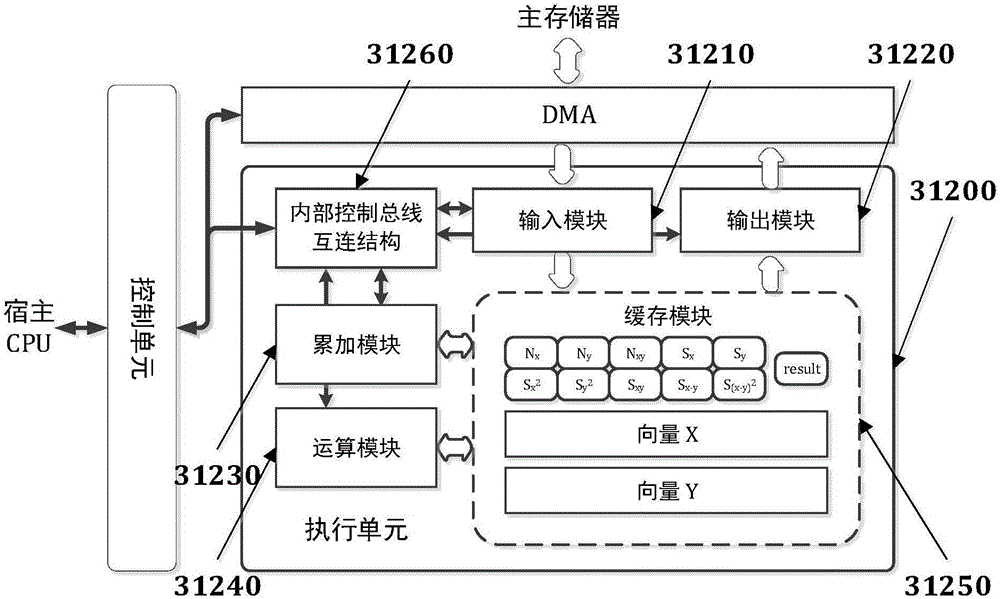

Hardware accelerator and method of collaborative filtering recommendation algorithm based on neighborhood model

InactiveCN106407137AThe acceleration effect is obviousReduce the required powerEnergy efficient computingElectric digital data processingCorrelation coefficientCosine similarity

The invention discloses a hardware accelerator of a collaborative filtering recommendation algorithm based on a neighborhood model. The hardware accelerator comprises a training accelerator structure and a forecasting accelerator structure, wherein the training accelerator structure is used for accelerating a training stage of the collaborative filtering recommendation algorithm of the neighborhood model; the forecasting accelerator structure is used for accelerating a forecasting stage of the collaborative filtering recommendation algorithm of the neighborhood model; the training accelerator part can accelerate calculation of a Jaccard similarity coefficient, a Euclidean distance, two cosine similarities, a Pearson's correlation coefficient and an average difference degree which are involved in the training stage of the acceleration algorithm; and the forecasting accelerator part can calculate cumulative summing, weighting cumulative averaging and summing cumulative averaging which are involved in the forecasting stage of the acceleration algorithm. The hardware accelerator is good in acceleration effect and relatively low in power and energy consumption expense.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC