Circuit reliability analysis method

An analysis method and reliability technology, applied in CAD circuit design, electrical digital data processing, instruments, etc., can solve the problems of difficult to support statistical static timing analysis, difficult to support fluctuation and aging analysis, high complexity, and achieve statistical Static timing analysis, accelerated application, accurate simulation results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Below in conjunction with accompanying drawing, further describe the present invention through embodiment, but do not limit the scope of the present invention in any way.

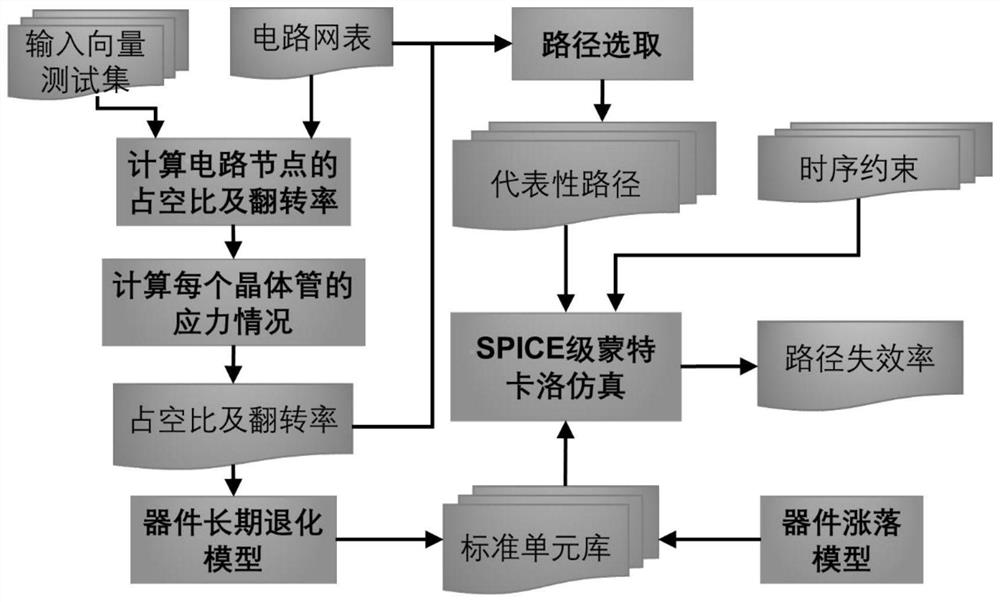

[0025] The invention provides a path-based circuit reliability analysis method, which does not need to establish a degradation-aware standard cell library, and can also support statistical static timing analysis. figure 1 Shown is the flow process of the inventive method, and concrete implementation comprises the steps:

[0026] Step 1. Select a representative path:

[0027] In order to realize path-based analysis, the present invention proposes a new representative path selection method. Although the degradation speed of different paths is different, it is impossible for a path with too small initial delay to become a critical path. First, perform static timing analysis, and then filter out short paths whose initial delay is less than 90% of the initial critical path delay (the longest path delay ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More