Method for aging trench gate VDMOS device and aging equipment

A device aging and aging equipment technology, applied in the direction of single semiconductor device testing, instruments, measuring devices, etc., can solve the problems of rapid inspection of separated gate trench VDMOS devices, injection, lack of automatic monitoring and control, etc., to achieve fast and effective. The effect of aging assessment screening

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

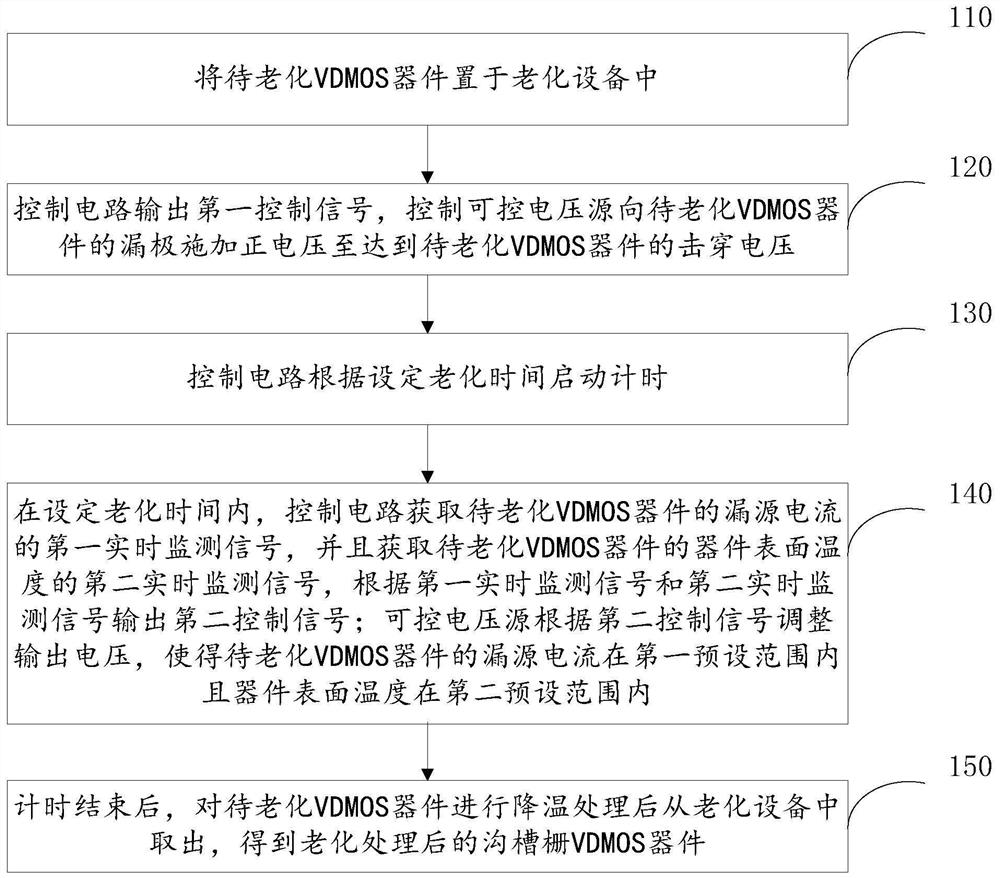

[0021] An embodiment of the present invention provides a method for aging a trench gate VDMOS device, the process of which is as follows figure 1 As shown, it mainly includes the following steps:

[0022] Step 110, placing the VDMOS device to be aged in an aging device;

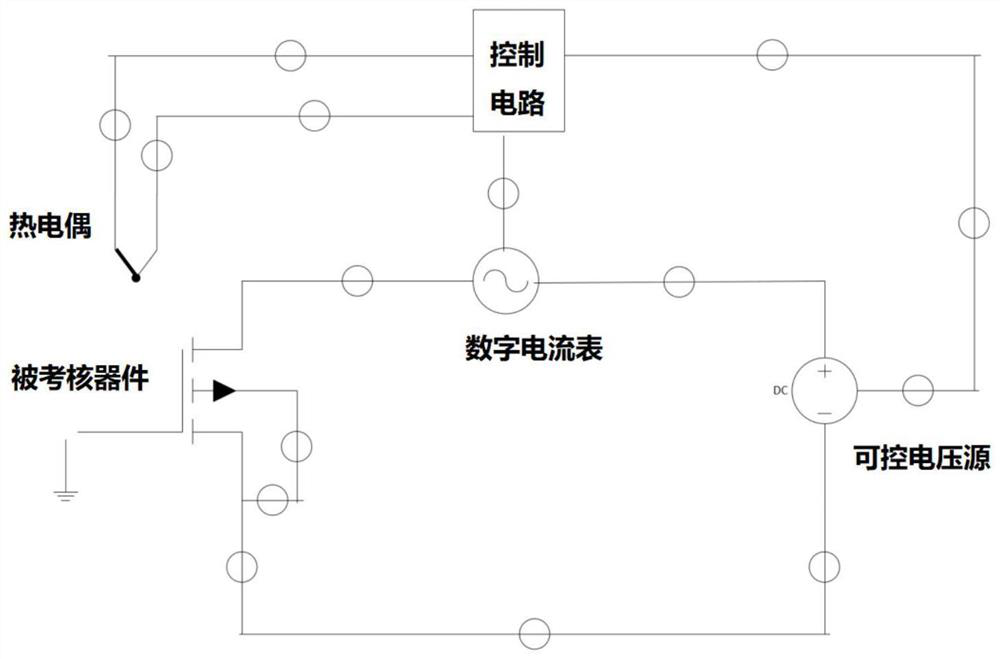

[0023] For ease of understanding, combine figure 2 As shown in the schematic diagram, the setting of the burn-in equipment and the VDMOS device to be aged in the burn-in equipment is firstly described.

[0024] Such as figure 2 As shown, the burn-in equipment includes: control circuit, thermocouple, digital ammeter and controllable voltage source.

[0025] The drain of the VDMOS device to be aged (the tested device shown in the figure) is connected to the positive pole of the controllable voltage source, the gate is connected to the negative pol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More