Multi-head chip mounter mounting efficiency optimization method and system based on bat algorithm

A bat algorithm and efficiency optimization technology, applied in computing, computing models, instruments, etc., can solve problems such as difficult energy focus, shifting work focus, slow convergence speed, etc., to improve computing efficiency, improve accuracy, and optimize capabilities high effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] In the following, the technical solution of the present invention will be described in detail through specific embodiments, and many specific details are set forth in the following description so as to fully understand the present invention. However, the present invention can be implemented in many other ways different from those described here, and those skilled in the art can make similar improvements without departing from the connotation of the present invention, so the present invention is not limited by the specific implementation disclosed below.

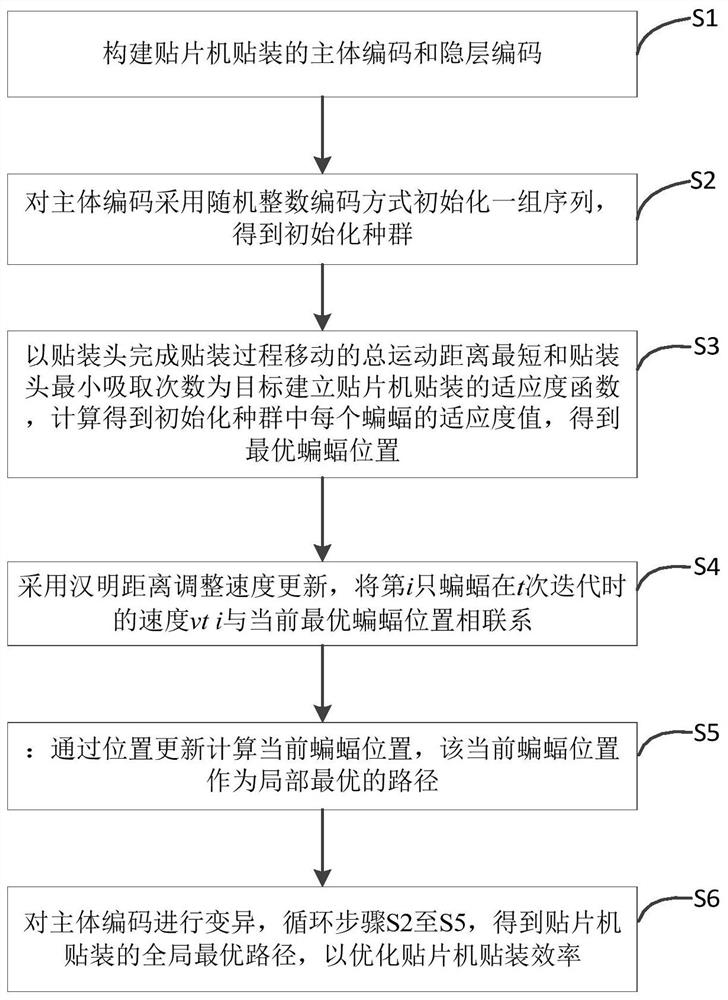

[0065] like Figures 1 to 9 As shown, a multi-head placement machine placement efficiency optimization method based on bat algorithm, including steps S1 to S6:

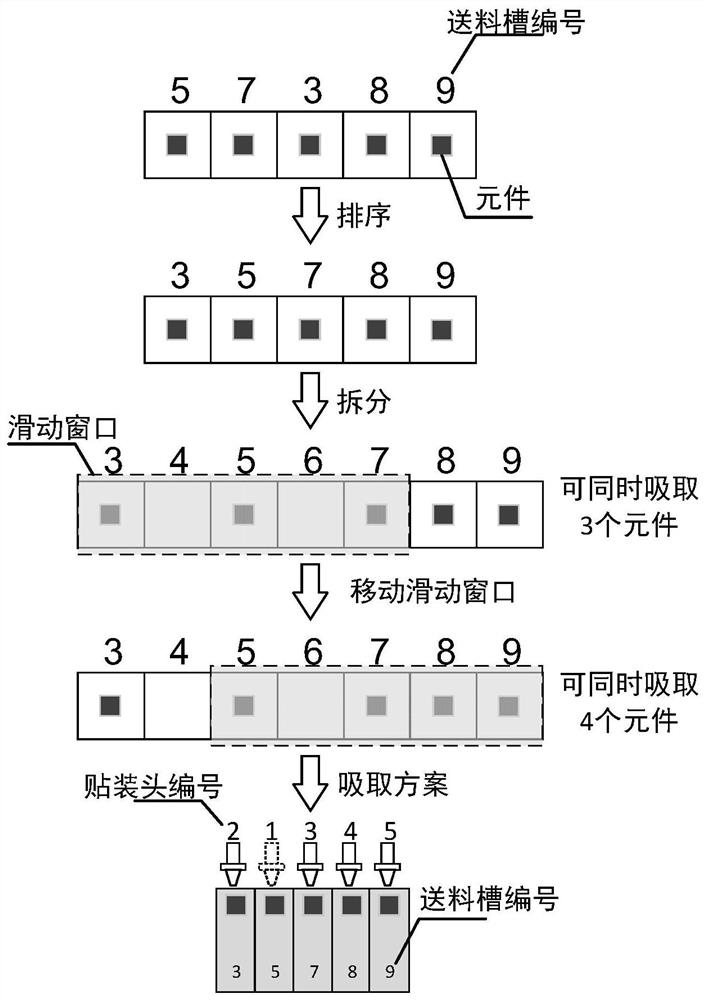

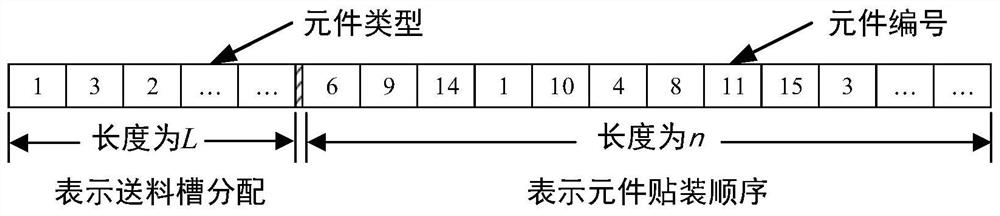

[0066] S1: Construct the main body code and hidden layer code for placement by the placement machine, the body code includes the allocation of feed slots and component placement sequences, and the hidden layer code includes the assignment of placement heads an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More