System-level integrated circuit DC voltage drop parallel analysis method and system

An integrated circuit and DC voltage drop technology, applied in CAD circuit design, special data processing applications, design optimization/simulation, etc., can solve problems such as huge memory, CPU time, and high time cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] The purpose of the present invention is to provide a parallel analysis method and system for DC voltage drop of system-level integrated circuits, so as to realize fast and accurate analysis of DC voltage drop of system-level VLSI.

[0066] In order to make the above objects, features and advantages of the present invention more comprehensible, the invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

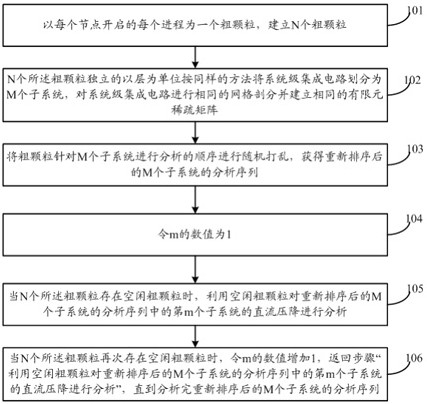

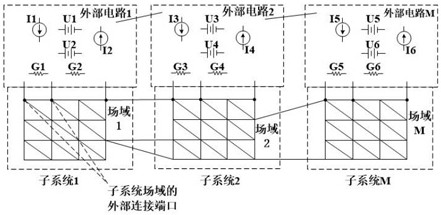

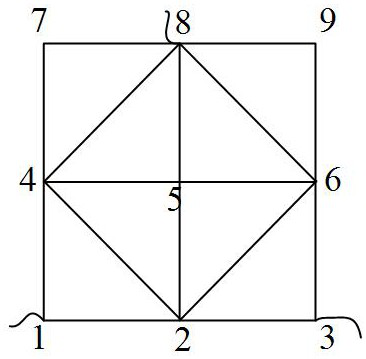

[0067] In order to solve the above problems, the present invention proposes a parallel analysis method for DC voltage drop of a system-level integrated circuit as a method for quickly and accurately analyzing the DC voltage drop of a system-level VLSI in combination with a delta-star transformation. The complex integrated circuit layout with a scale ranging from centimeters to nanometers is meshed. For field-based problems, the finite element stiffness matrix is written using the finite element method....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More