System for achieving data processing acceleration based on FPGA and acceleration method thereof

A data processing and data technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of flexible topology expansion that is not suitable for hardware accelerators, inflexible data transmission, etc., to achieve flexible data transmission and topology configuration, The effect of expanding application scenarios and improving processing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

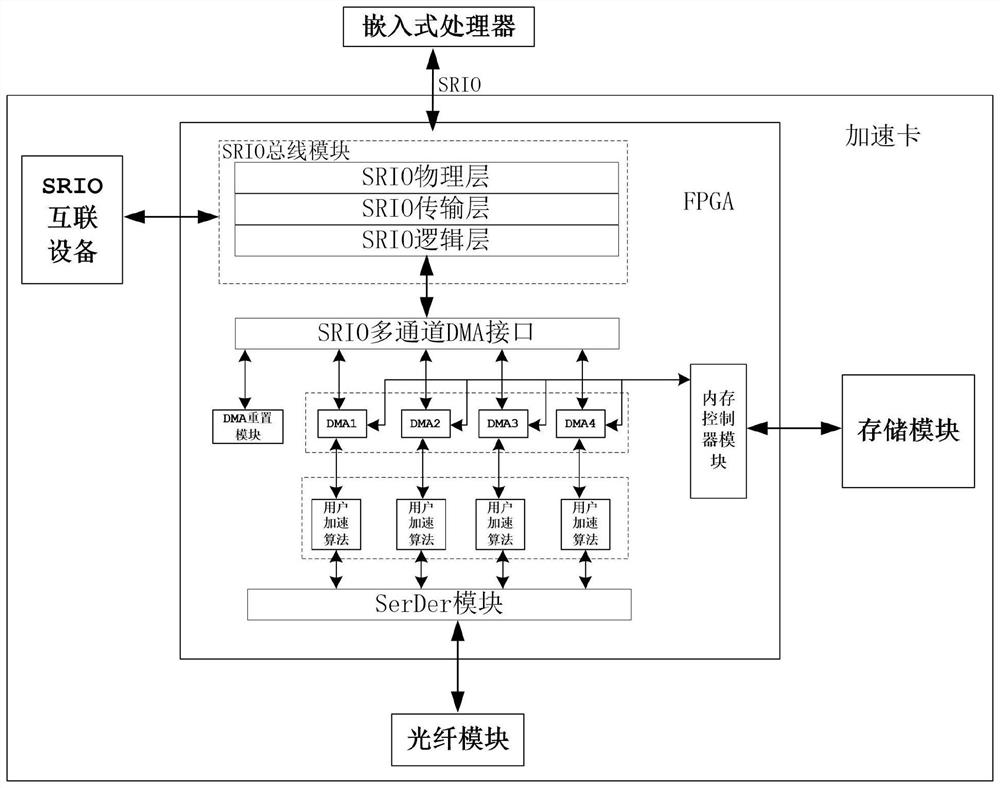

[0049] The system for realizing data processing acceleration based on FPGA can greatly improve the processing speed by realizing data processing tasks with gate-level circuits through FPGA. The data processing acceleration algorithm in this embodiment is realized by programmable gate array in FPGA. The device can realize different data processing acceleration functions by loading different FPGAbit flow files, which has greater flexibility than traditional hardware accelerators. In addition, the FPGA chip is directly connected to the processor through the SRIO bus in the present invention, and the SRIO bus protocol The feature is that the data transmission method is more flexible than the PCIe bus. It can directly read and write the address space of the target device through NWRITE, NWRITE_R, SWRITE, NREAD, ASTOMIC and other transactions. In the absence of visibility into the address space of the target device, SRIO A message delivery mechanism is also provided. The user sends t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More