Universal alternate sampling ADC system

A technology of acquisition circuit and clock management, applied in the field of electronics, can solve the problems affecting the versatility and design cycle and difficulty of alternate sampling ADC, ADC output spectrum spurious, and difficulty in PCB layout design, so as to improve chip versatility and resistance to resistance. Interference ability, optimizing timing mismatch and bandwidth mismatch, reducing the effect of thermal design difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0028] In the existing alternate sampling technology, there are four kinds of mismatch problems among the ADCs: offset mismatch, gain mismatch, timing mismatch and bandwidth mismatch, which lead to spurs in the ADC output spectrum and a decrease in the overall performance of the system. The existing technology In order to ensure the system performance, the alternate sampling ADC system needs to be redesigned and debugged in different circuits, which greatly affects the versatility, design cycle and difficulty of the alternate sampling ADC.

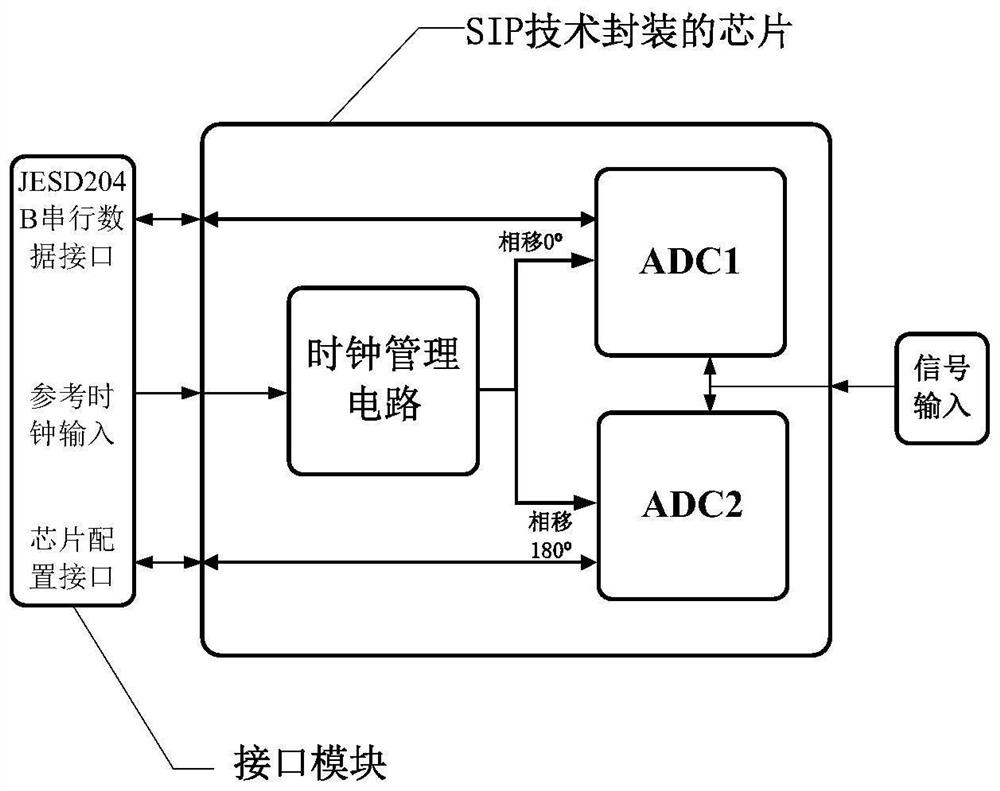

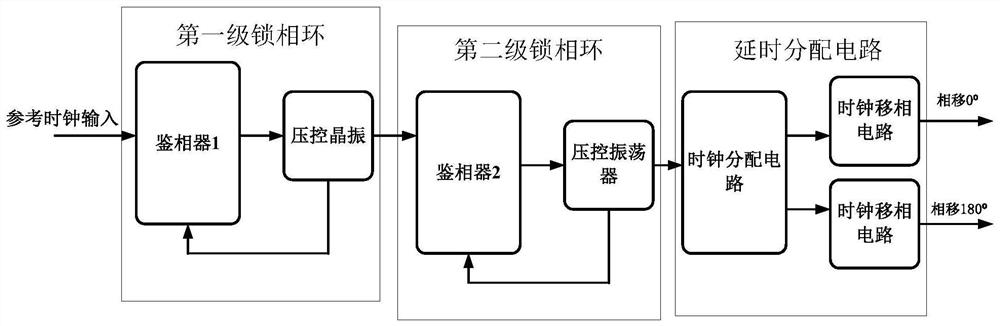

[0029] Therefore, if figure 1 As shown, a kind of general alternate sampling ADC system of the present invention comprises an ADC acquisition circuit composed of an interface module, a clock management circuit, and several independently working ADCs, and the interface module is composed of a data interface, a reference clock input, and a chip configuration interface, and is characterized in that , the ADC acquisition circuit is communicati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More