Semiconductor device package assembly and manufacturing method thereof

A device package and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve semiconductor device damage, reduce device and/or system reliability, shorten devices or related The operating life of components and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

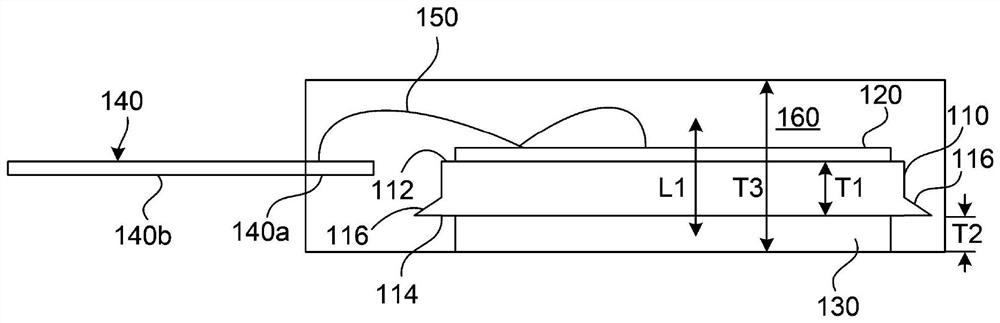

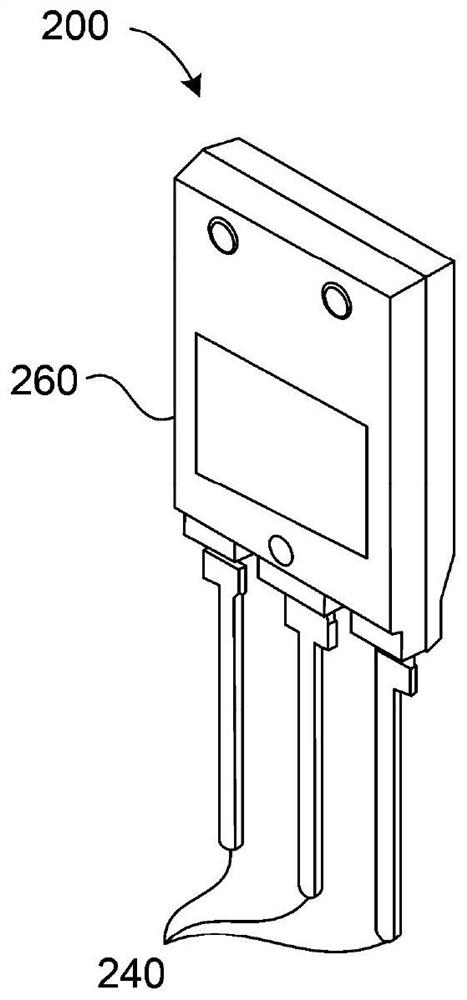

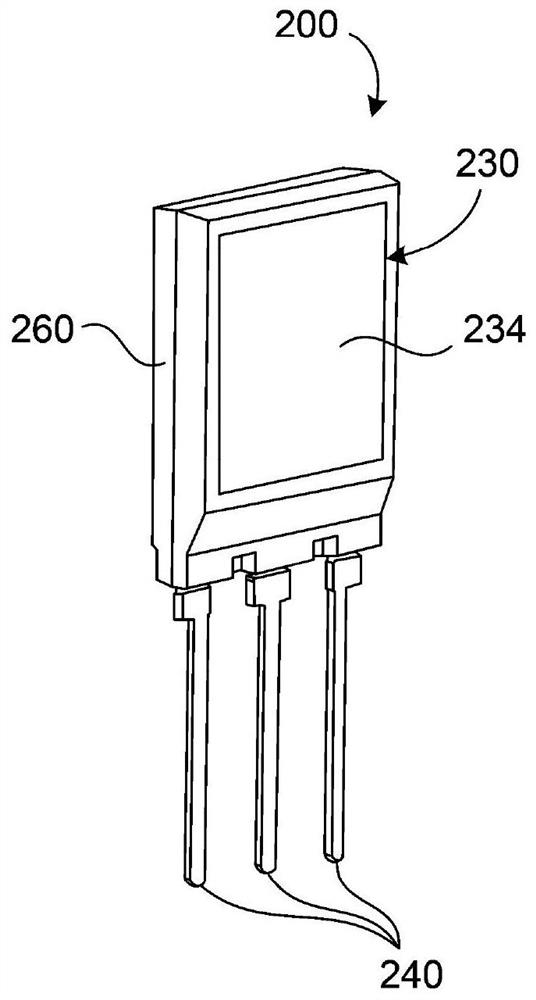

[0014] A semiconductor device assembly (e.g., semiconductor device package, packaged semiconductor device, packaged device, etc.), such as those described herein, may include a die attach paddle, one or more semiconductor die (e.g., disposed on die attach paddle), one or more signal leads, one or more wire bonds that electrically couple the one or more semiconductor dies and / or the one or more signal leads to each other, and isolation substrate. Exemplary implementations described herein may overcome at least some of the disadvantages discussed above. For example, in some implementations, the isolation substrate can include a ceramic substrate that separates an external heat dissipation surface (eg, a metal layer disposed on the ceramic substrate) from one or more semiconductor die, die-attached Connect to the blades and other electrical isolation. Additionally, the use of an isolating substrate, such as in the exemplary implementations described herein, may allow for the el...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com