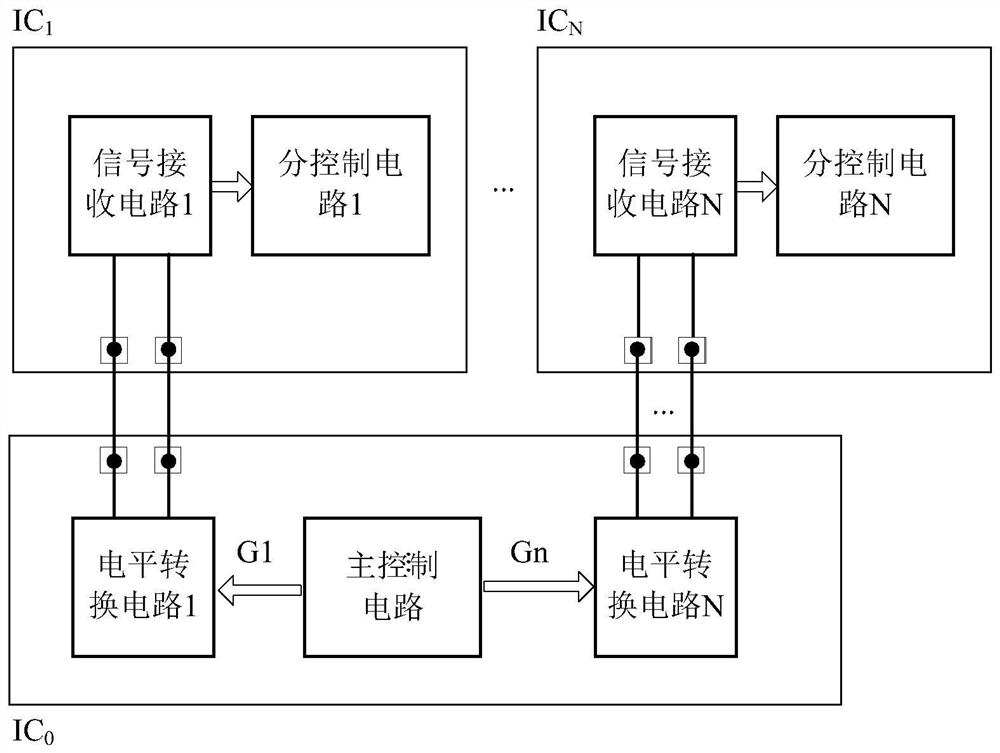

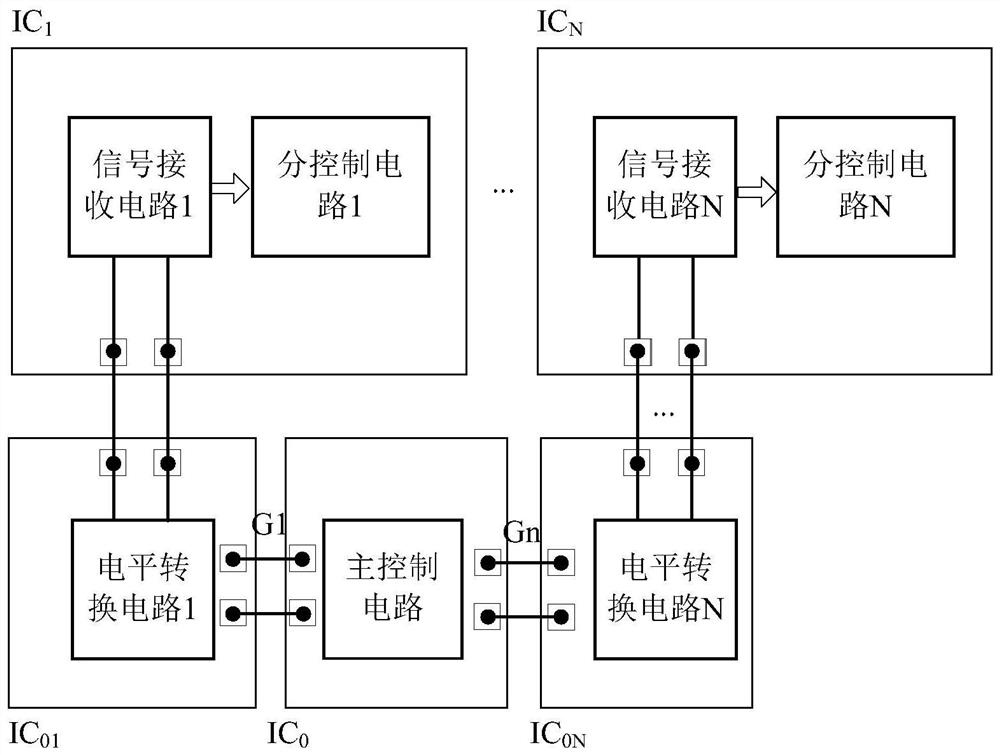

Communication control circuit applied to power supply chip

A communication control and power chip technology, applied in the field of power electronics, can solve the problems of high cost, large chip area, long chip production cycle, etc., and achieve the effect of reducing cost and process difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

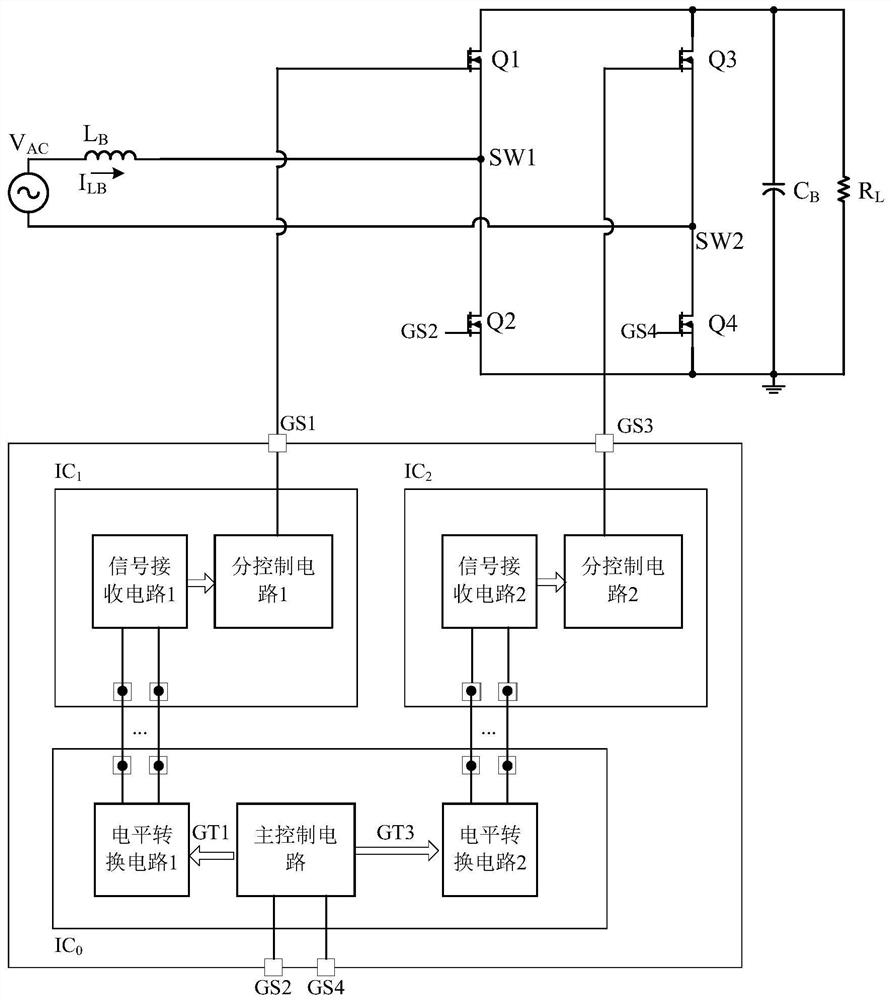

Embodiment Construction

[0027] The present invention is described below based on examples, but the present invention is not limited to these examples. In the following detailed description of the invention, some specific details are set forth in detail. The present invention can be fully understood by those skilled in the art without the description of these detailed parts. In order not to obscure the essence of the present invention, well-known methods, procedures, procedures, components and circuits have not been described in detail.

[0028] Additionally, those of ordinary skill in the art will appreciate that the drawings provided herein are for illustrative purposes and are not necessarily drawn to scale.

[0029] Meanwhile, it should be understood that in the following description, "circuit" refers to a conductive loop formed by at least one element or sub-circuit through electrical connection or electromagnetic connection. When an element or circuit is said to be "connected to" another eleme...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More