Write depth test system and method for memory chip

A technology for memory chips and depth testing, applied in static memory, instruments, etc., can solve problems such as poor convenience, and achieve the effect of simple operation, satisfying wide voltage testing, and convenient testing operation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below through specific embodiments in conjunction with the accompanying drawings. These embodiments are only used to illustrate the present invention, and are not intended to limit the protection scope of the present invention.

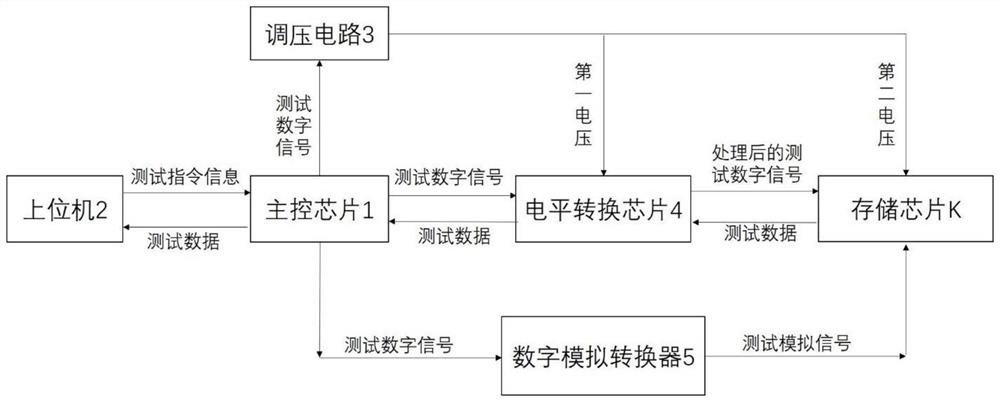

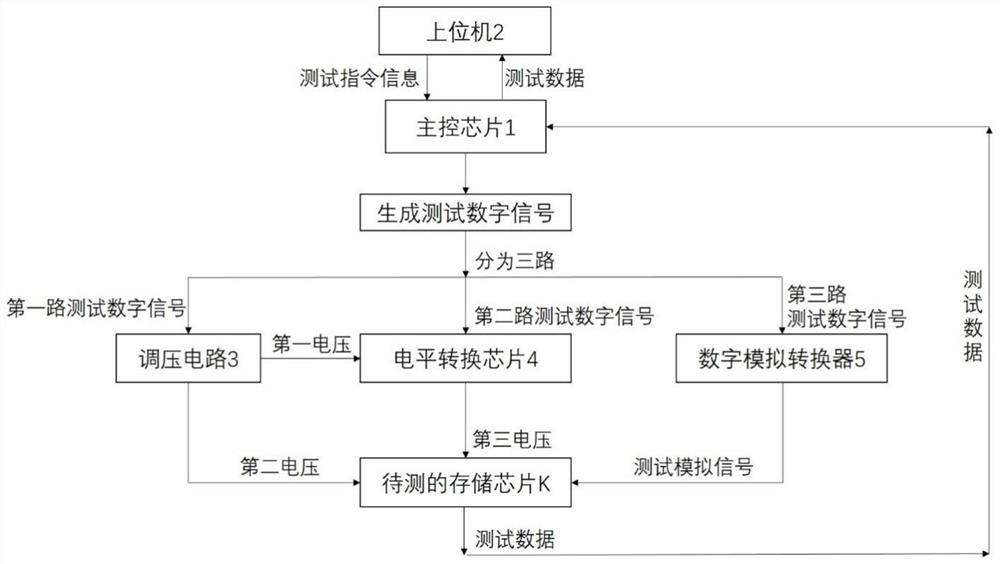

[0032] The present invention provides a write-in depth test system for memory chips. The write-in depth test system adopts a highly integrated board-level design. In this embodiment, the write-in depth test system has a size of 15cm×10cm; Such as figure 1 As shown, it includes: a main control chip 1 , a host computer 2 , a voltage regulating circuit 3 , a level conversion chip 4 and a digital-to-analog converter (DAC) 5 .

[0033] Wherein, the tester inputs the test instruction information of the writing depth test in real time through the host computer 2; Instruction information to generate test digital signals.

[0034] The input terminal of the voltage regulating circuit 3 is connected with t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More