Method and appts. for access complex vector located in DSP memory

A vector and complex number technology, applied in the field of processor storage addressing and storage address generation, can solve problems such as difficult memory relocation and low memory application efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

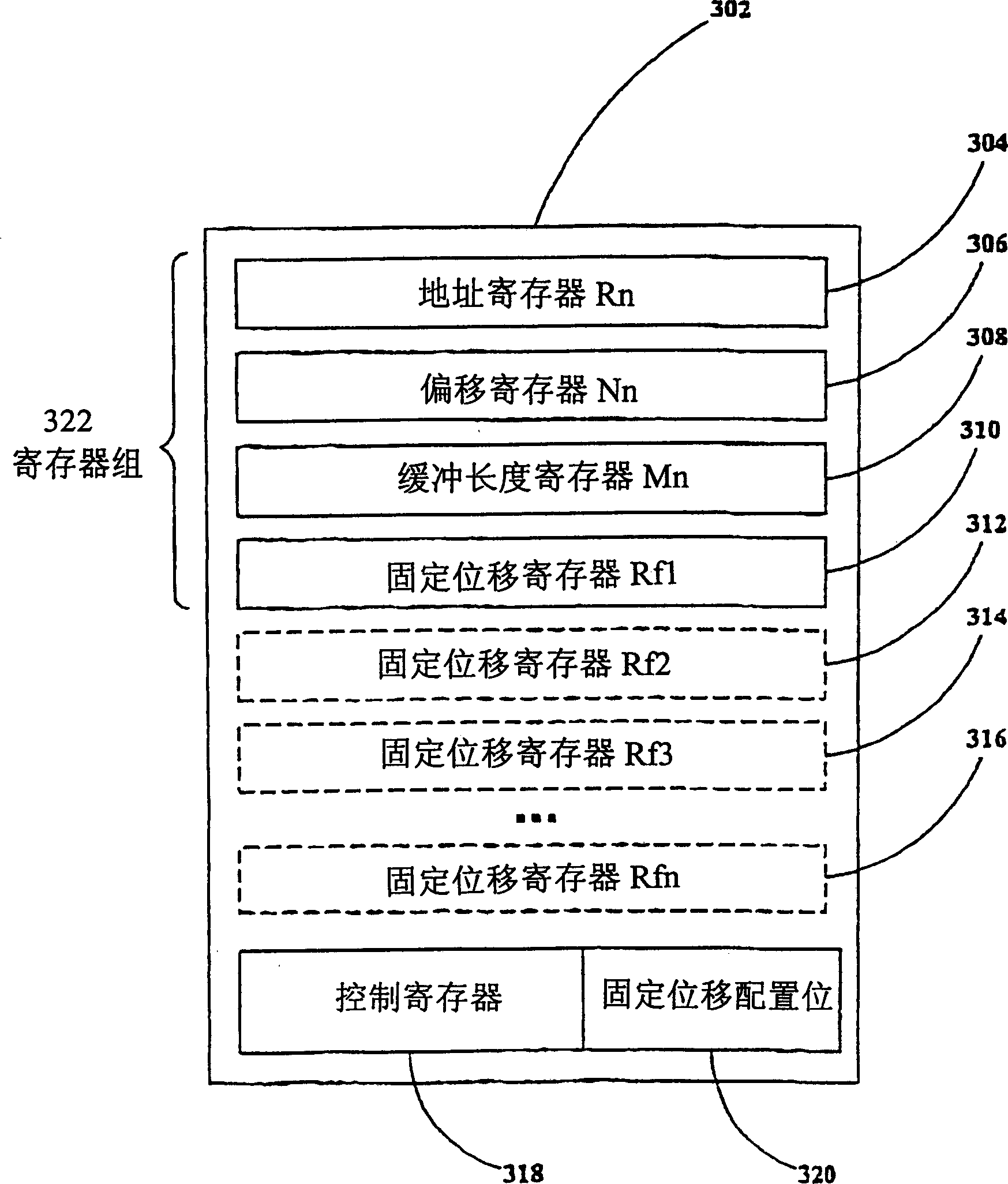

[0026] The principle and operation of a method and device according to the present invention can be explained with the accompanying drawings and corresponding descriptions, and the important part of the device address generating unit of the present invention is shown in image 3 In, the steps of the method of the present invention are in Figure 4 They are illustrated in the flowcharts of , which are implemented in a digital signal processor or other processor according to the invention. These steps implement the fixed displacement mode, which is a new processor mode according to the invention.

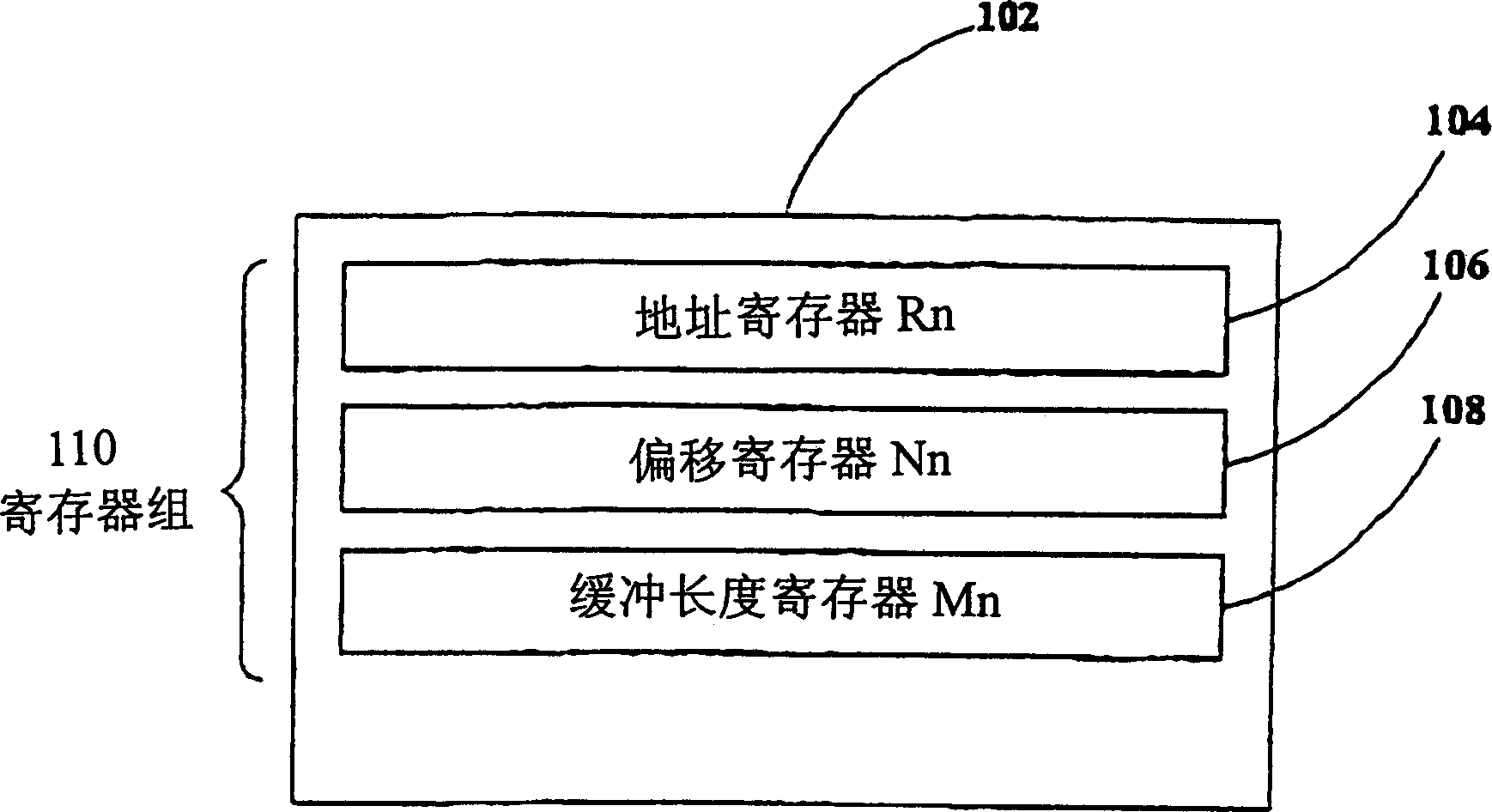

[0027] as in image 3 As explained, it is first necessary to provide certain additional hardware capabilities. In particular, the processor must have a fixed shift register 310 in the address generation unit 302, denoted by Rf1. The fixed shift register should be software programmable like all other registers in address generation unit 302 . It is also possible, but not required, to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More