High-speed ADC parallel-serial conversion circuit

A serial conversion and circuit technology, which is applied in the field of high-speed ADC parallel-serial conversion circuit, can solve the problems of high production cost and large occupied area, and achieve the effect of reducing circuit power consumption, circuit area and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

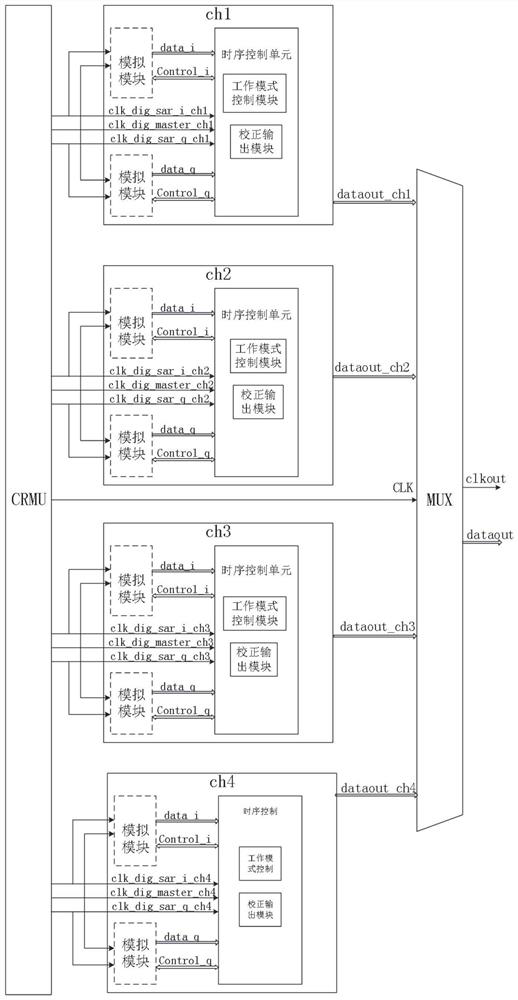

[0019] A high-speed ADC parallel-to-serial conversion circuit, including a clock reset management unit, n timing control units and data selection output units, this embodiment takes n=4 as an example, and the specific structure refers to figure 1 .

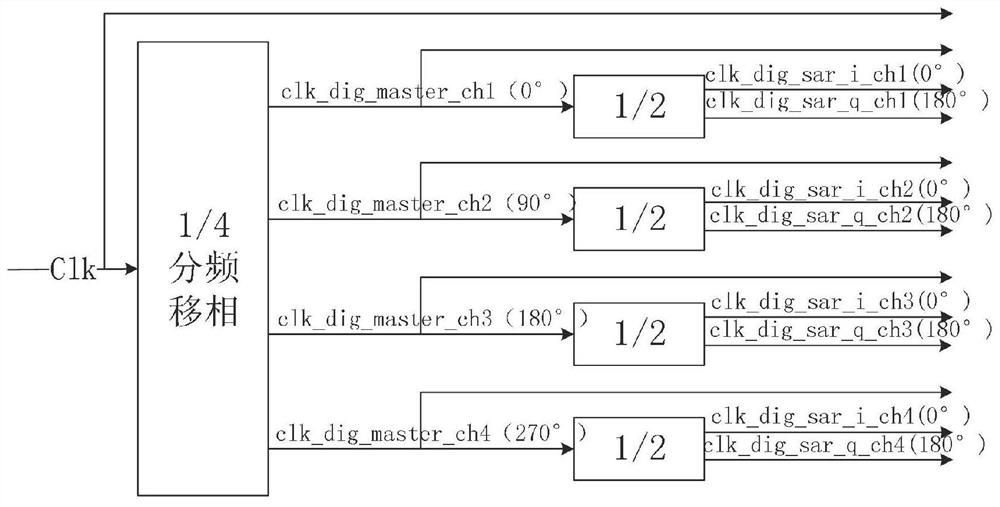

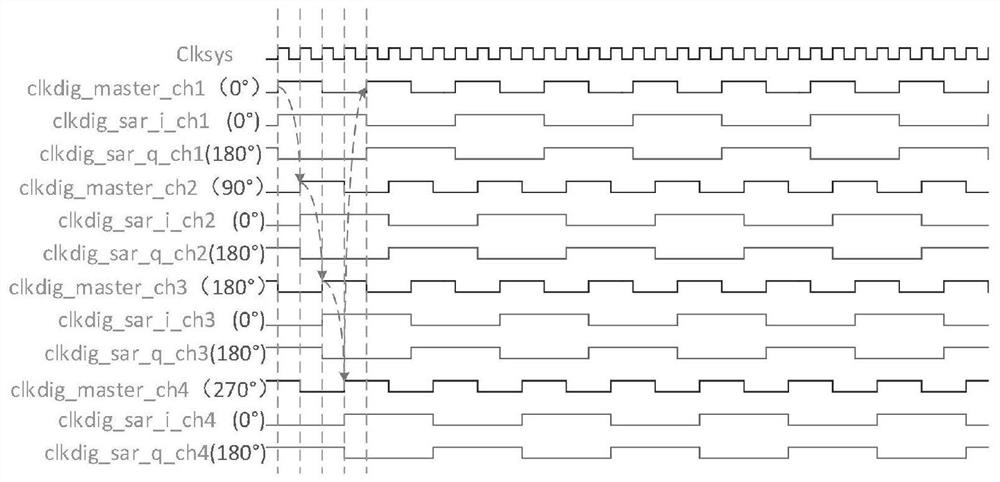

[0020] The clock reset management unit CRMU provides clock signals and reset signals for each timing control unit, and its clock block diagram is as follows figure 2 As shown, the main clock Clk is divided by 4 and phase-shifted to generate channel working clocks clk_dig_master_ch1, clk_dig_master_ch2, clk_dig_master_ch3, and clk_dig_master_ch4 corresponding to the four timing control units. The four channel working clocks are divided by 2 to generate clk_dig_sar_i_ch1, clk_dig_sar_i_ch2, clk_dig_sar_i_ch3, clk_dig_sar_i_ch4; after 2 frequency division and inversion, clk_dig_sar_q_ch1, clk_dig_sar_q_ch2, clk_dig_sar_q_ch3, clk_dig_ch4sar_q are generated.

[0021] The channel working clocks of each timing control unit have ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com