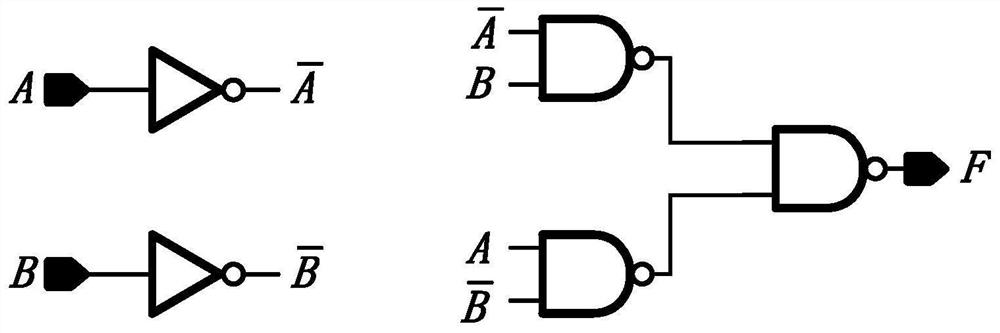

Fast compact XOR gate circuit

A gate circuit, fast technology, applied in the direction of XOR circuit, logic circuit, logic circuit with logic function, etc., can solve the problems of large number of transistors, high power consumption, slow speed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

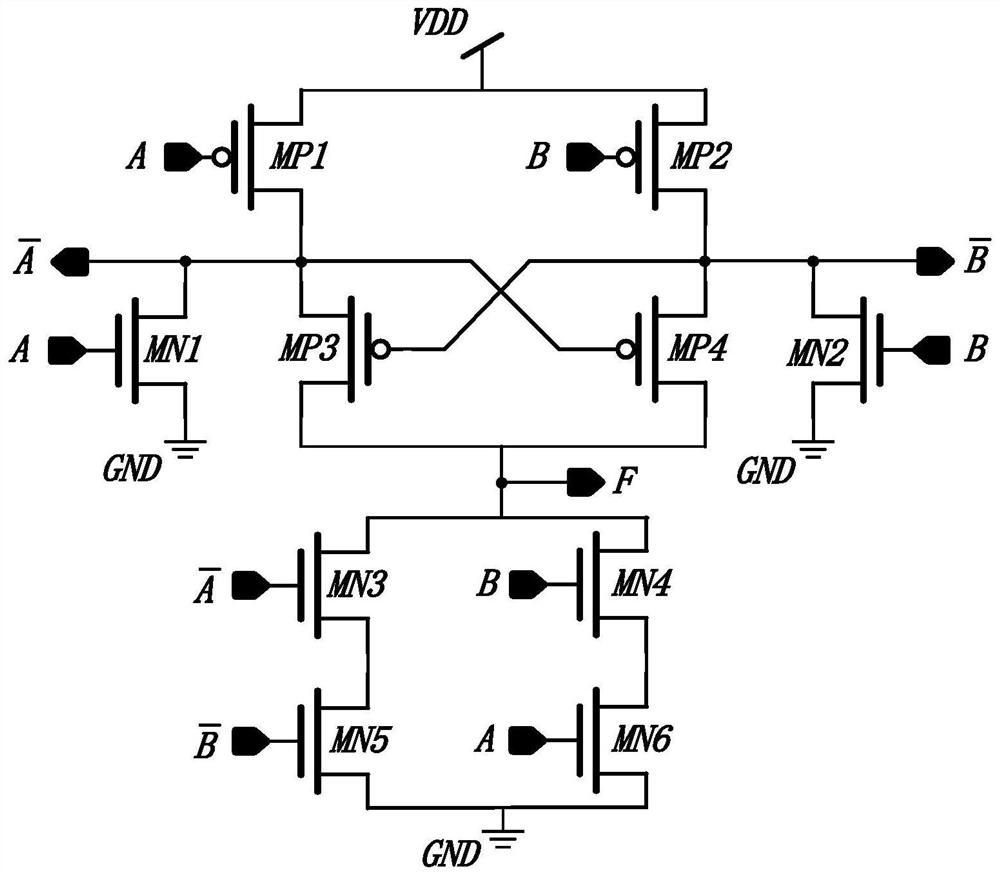

[0016] Below in conjunction with accompanying drawing, technical solution of the present invention is described in detail:

[0017] like figure 2 Shown is a circuit diagram of a fast and compact XOR gate proposed by the present invention, including six NMOS transistors and four PMOS transistors.

[0018] The components of the XOR gate circuit PMOS transistors include a first PMOS transistor MP1, a second PMOS transistor MP2, a third PMOS transistor MP3, and a fourth PMOS transistor MP4; wherein, the third PMOS transistor MP3 and the fourth PMOS transistor MP4 form an intersection Coupling structure, this structure can improve the transmission speed of the circuit; the components of the NMOS tube include the first NMOS tube MN1, the second NMOS tube MN2, the third NMOS tube NM3, the fourth NMOS tube MN4, the fifth NMOS tube MN5, the sixth NMOS tube MN6.

[0019] Transistors related to the input signal A: the gates of the first PMOS transistor MP1, the first NMOS transistor M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More