High-precision low-jitter delay pulse generator

A pulse generator and low jitter technology, applied in the field of sub-nanosecond delay pulse generation devices, can solve the problems of limited delay dynamic range, low pulse output jitter, and inability to obtain, and reduce system integration and cost. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

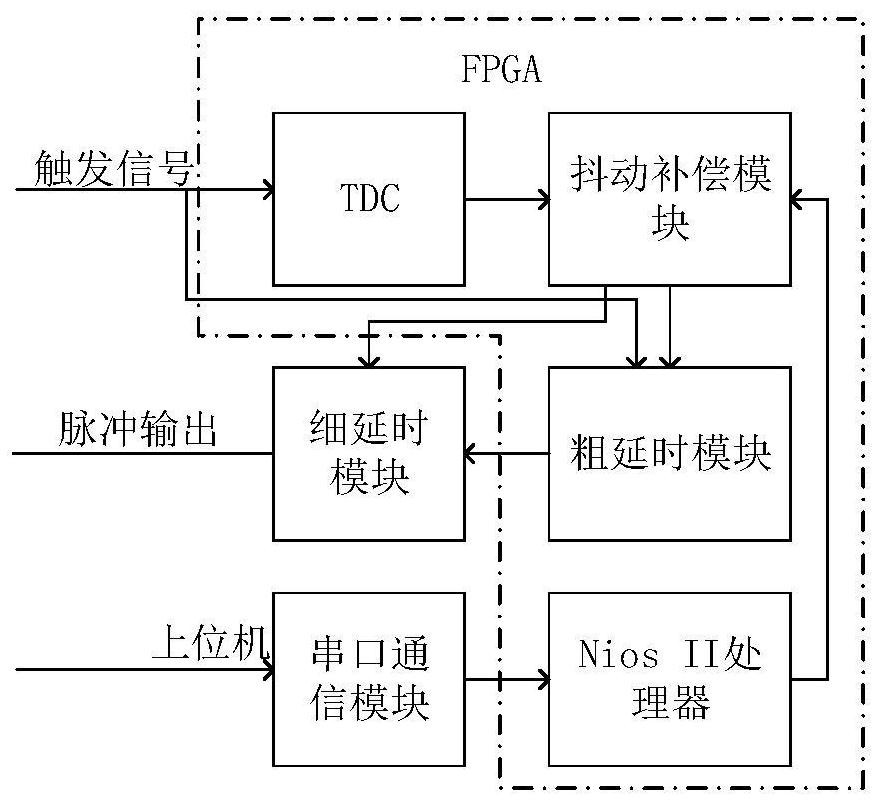

[0018] Such as figure 1 The high-precision low-jitter delay pulse generator shown is composed of TDC module, jitter compensation module, coarse delay module, Nios II processor module, serial port communication module, fine delay module and other parts, among which TDC module, jitter compensation, The coarse delay module and the Nios II module are all inside the same FPGA.

[0019] The external trigger signal enters the delay system through the trigger signal input interface, the trigger level is 3.3V LVTTL, and the input impedance is 50Ω.

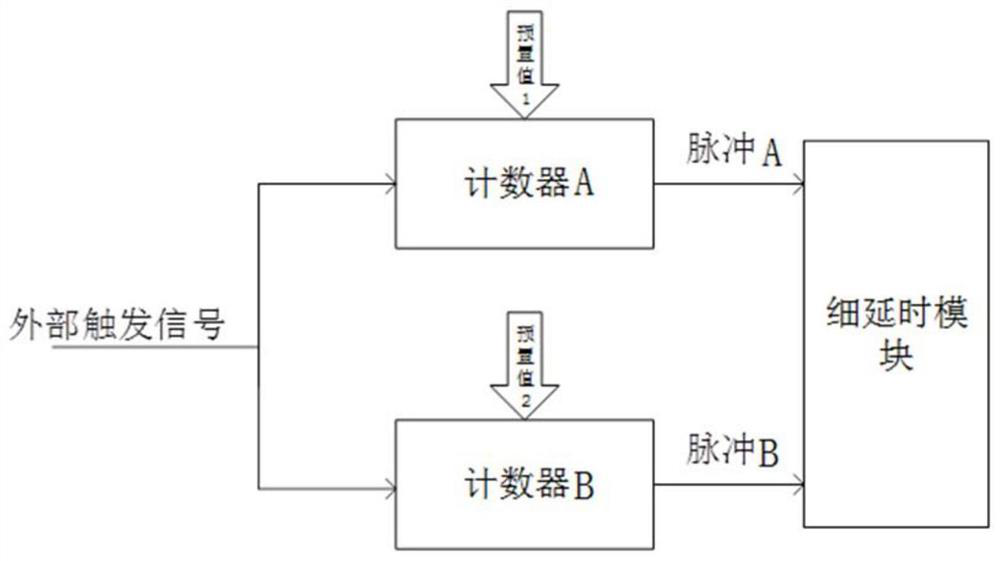

[0020] Such as figure 2 The structure diagram of the TDC module is shown. After the external trigger signal arrives, it will propagate along t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More