Method for optimizing access efficiency of DDR4 SDRAM in FPGA

An optimization method and access efficiency technology, applied in program control design, instrumentation, electrical digital data processing, etc., can solve problems such as reducing the access efficiency of DDR4 SDRAM, and achieve the effect of reducing the impact of access efficiency and improving access efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

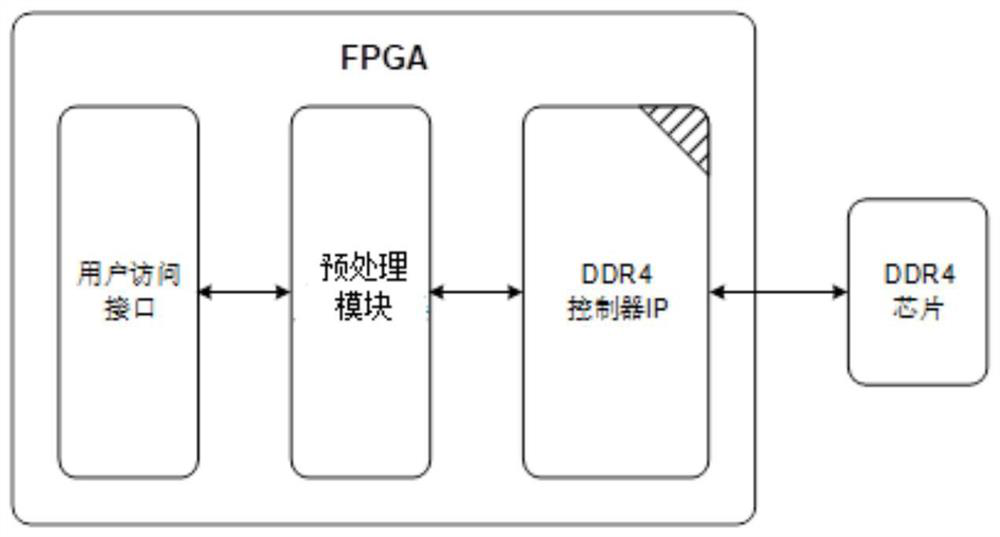

[0024] The present invention is described in further detail now in conjunction with accompanying drawing. These drawings are all simplified schematic diagrams, which only illustrate the basic structure of the present invention in a schematic manner, so they only show the configurations related to the present invention.

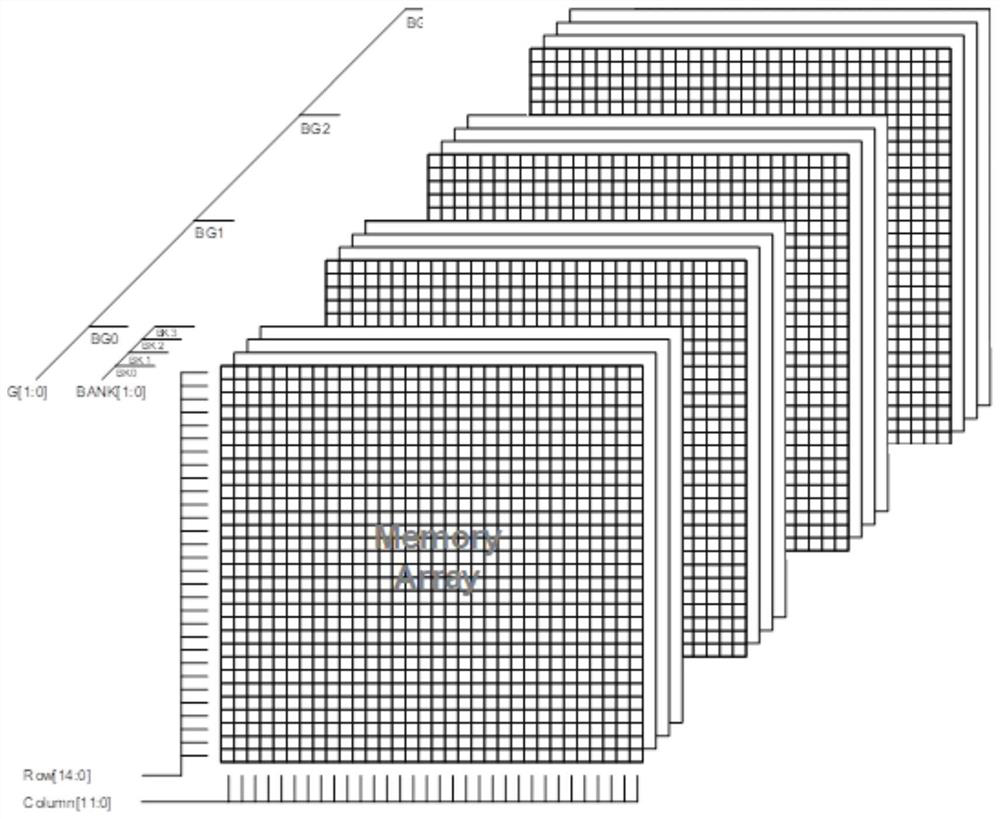

[0025] Such as figure 1 As shown, the internal storage structure of the DDR4 SDRAM chip is usually divided into several Bank groups, each Bank group has several Banks (usually 4-8 banks), each Bank has several row storage spaces, and each row There are several column storage spaces, so the storage address of DDR4 SDRAM is composed of BG (Bank group) address, Bank address, Row (row) address, and Column (column) address.

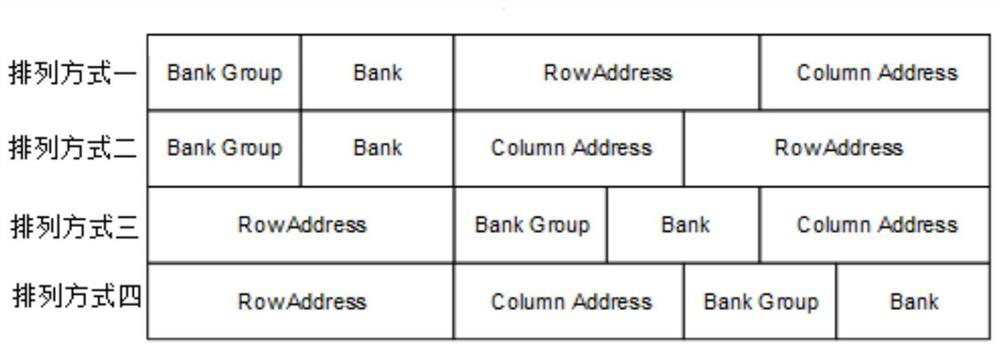

[0026] The arrangement of the access address of the access command for the user to access the memory space of DDR4 SDRAM can refer to figure 2 , figure 2 Although four arrangements are shown in , the addresses in each arrangement have BG ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More