Cover plate, chip wafer packaging method and chip airtight packaging method

A technology of wafer packaging and packaging methods, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of high cost and large volume of airtight packaging, and achieve the effect of low cost and small volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

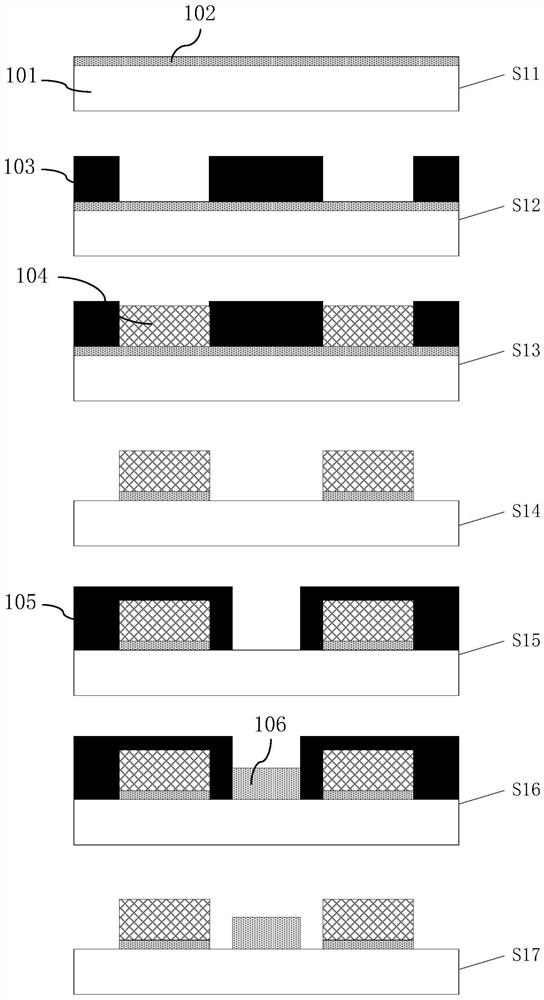

[0053] Such as figure 1 as shown, figure 1 It is a work flow chart of a cover wafer packaging method provided in Embodiment 1 of the present invention, including:

[0054] Step S11: making the first metal layer 102 on the front of the cover plate 101;

[0055] Step S12: making a first mask 103 on the first metal layer 102 to wrap the area to be sealed or the sensing area of the chip;

[0056] Step S13: making a first circuit pattern 104 in the gap of the first mask 103;

[0057] Step S14: removing the first mask 103 and performing etching to obtain a cover wafer.

[0058] Specifically:

[0059] Step S11, electroless copper plating: electroplate a metal layer on the front of the cover plate 101 by electroless copper plating, sputtering or vapor deposition of metals such as Ti, TiW, Cr, Co, etc., to play the role of a barrier layer and an adhesion layer. The cover plate 101 The material can be silicon, glass, metal and other wafer materials;

[0060] Step S12, electropla...

Embodiment 2

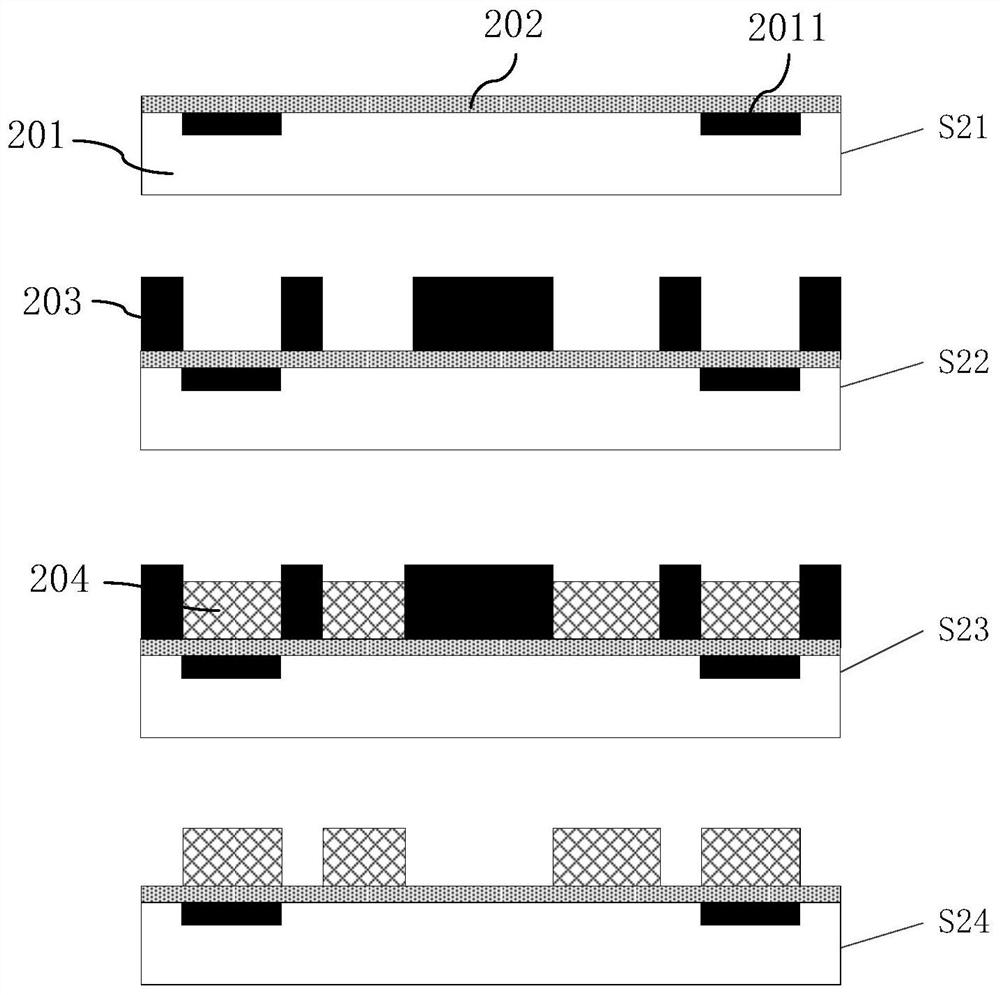

[0076] Such as figure 2 as shown, figure 2 It is a chip wafer packaging method provided in Embodiment 2 of the present invention, including:

[0077] Step S21: making a second metal layer 202 on the front side of the chip 201;

[0078] Step S22: making a third mask 203 at a position corresponding to the bonding pad 2011 of the chip 201 and the first circuit pattern of the cover wafer;

[0079] Step S23: making a third circuit pattern 204 within the gap of the third mask 203;

[0080] Step S24: removing the third mask 203 and performing etching to obtain a chip wafer.

[0081] Specifically:

[0082] Step S21, electroless copper plating: electroplating a metal layer on the front side of the chip 201 by electroless copper plating, sputtering or vapor deposition of metals such as Ti, TiW, Cr, Co, etc., to play the role of a barrier layer and an adhesion layer, and the chip 201 is completed Chips of application-specific integrated circuits or micro-electro-mechanical systems...

Embodiment 3

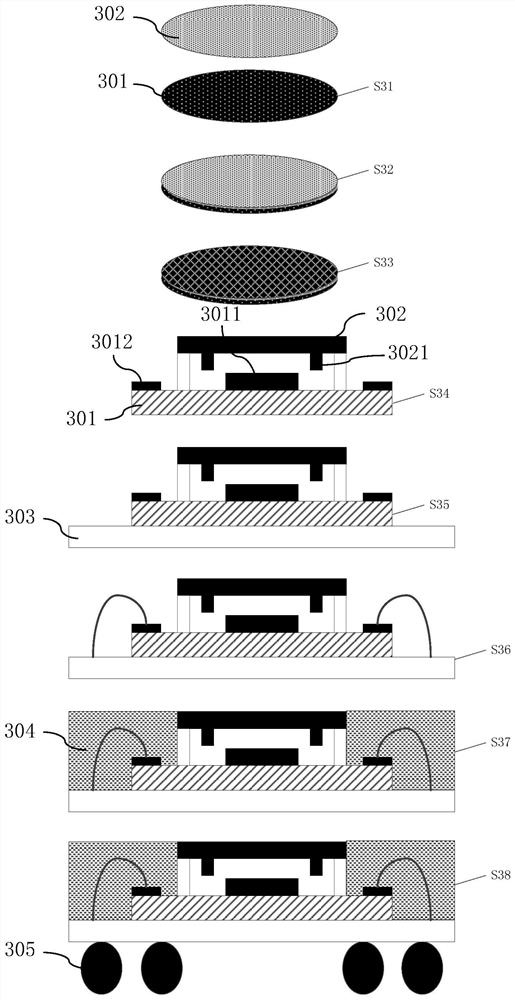

[0092] Such as image 3 as shown, image 3 It is a chip hermetic packaging method provided in Embodiment 3 of the present invention, including:

[0093] Step S31: use the aforementioned chip wafer packaging method to package the chip to obtain a chip wafer 301, and use the aforementioned cover wafer packaging method to package the cover to obtain a cover wafer 302;

[0094] Step S32: bonding the front surface of the cover wafer 302 and the front surface of the chip wafer 301 through the first metal layer and the second metal layer, so that the first circuit pattern of the cover wafer 302 wraps the chip wafer 301. Sealing area or sensing area 3011;

[0095] Step S33: Scribing the cover wafer 302 on the back side of the cover wafer 302, and exposing the bonding pads 3012 of the chip wafer 301;

[0096] Step S34: Scribing the chip wafer 301 at the position corresponding to the bonding pad 3012 of the chip wafer 301 to obtain a chip structure including the cover wafer 302 and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More