Chip packaging structure and preparation method thereof

A chip packaging structure and chip technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, semiconductor devices, etc., can solve the problems of reducing chip quality, chip failure, wire bonding, etc., to solve chip failure, The effect of expanding the scope of action and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

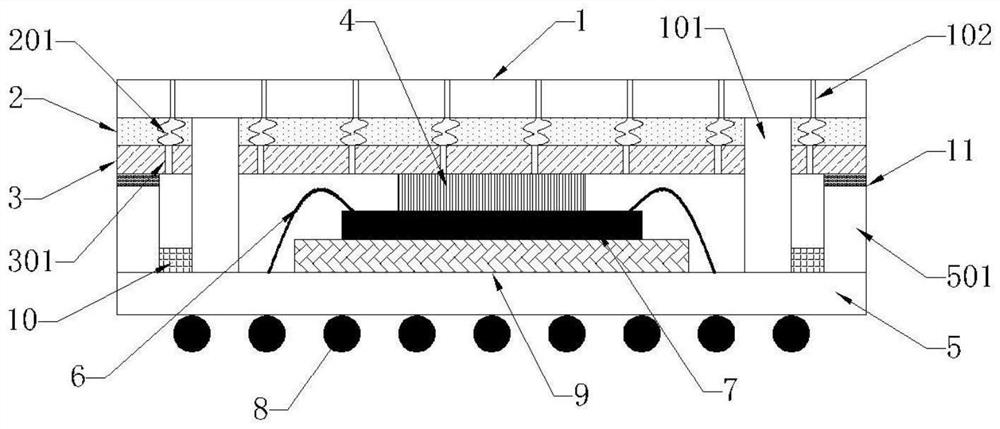

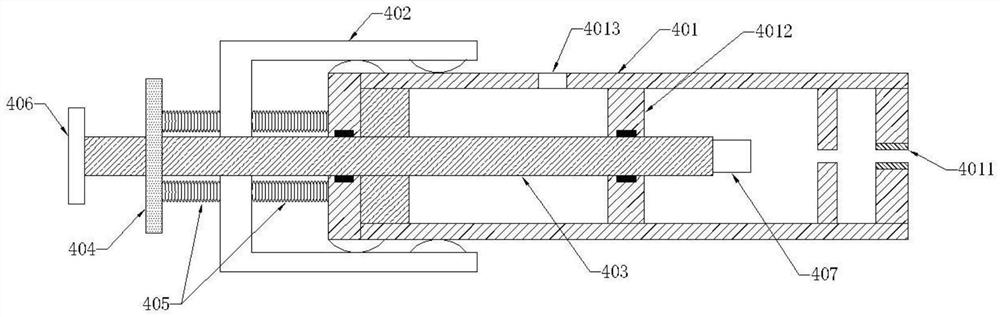

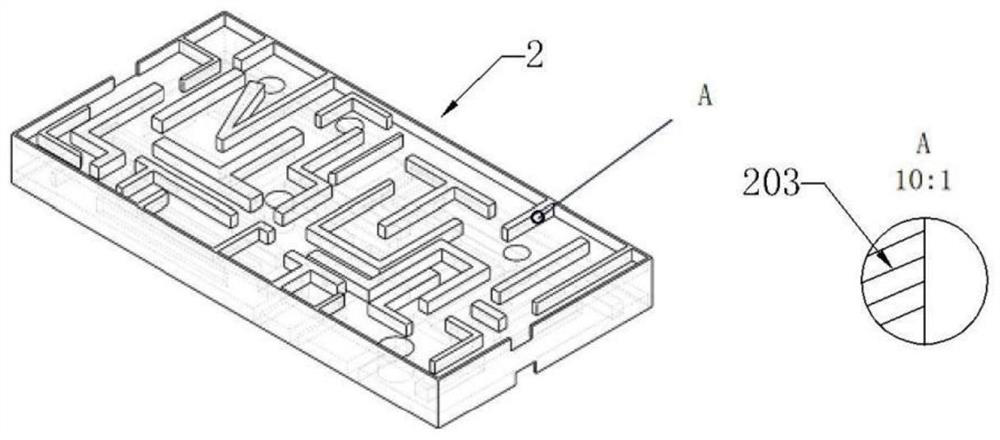

[0042] Such as Figure 1-7 As shown, a chip packaging structure is characterized in that it includes a cover plate and a base. The cover plate includes a cover plate base disc 1, a heat dissipation layer 2, and a moisture absorption layer 3 that are superimposed and fixedly connected layer by layer. 101, the cover plate retaining member 101 runs through the heat dissipation layer 2 and the moisture absorption layer 3 and extends out of the moisture absorption layer 3 for a predetermined distance, as a fitting part connecting the cover plate to the base; Several micro-holes 102 are opened at a distance, and several micro-fluidic channels 201 are opened corresponding to the micro-holes 102 in the heat dissipation layer 2. The micro-fluidic channels 201 communicate with the micro-holes 102, and several water-absorbing holes 301 are set on the moisture-absorbing layer 3. , the water absorption hole 301 has a Nepenthes structure, and the water absorption hole 301 communicates with...

Embodiment 2

[0055] Such as Figure 8-11 Shown, a kind of preparation method of chip packaging structure comprises the following steps:

[0056] S1: Using a ceramic, metal or glass wafer to prepare the cover plate substrate wafer 1, and making micro holes 102 on the cover plate base through the laser etching process or plasma etching process in the micro-nano processing technology;

[0057] S2: Use a metal or ceramic wafer to prepare the heat dissipation layer 2, make a mask on the heat dissipation layer material by coating photoresist, exposure, development and other processes, and use the laser etching process to manufacture the microfluidic channel 201, through rapid etching The process etches away the substrate other than the pattern of the microfluidic channel 201, removes the mask, and obtains the heat dissipation layer 2, and manufactures the gourd-shaped through hole 202 through the laser etching hole technology in the micro-nano processing technology, which is used to connect the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| pore size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More