Method for forming ion implantation region

A technology of ion implantation area and implantation area, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid device, etc., can solve the problems of difficult control of width, reduce IMP implantation energy, etc., and achieve the effect of preventing the change of junction depth morphology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

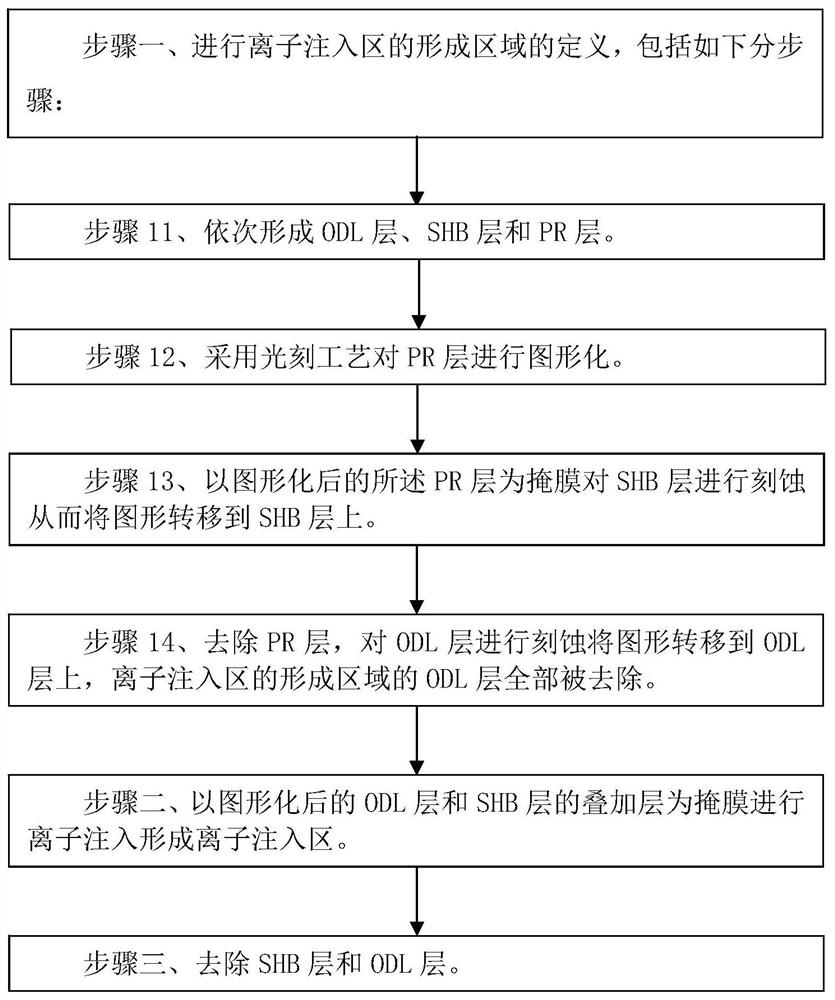

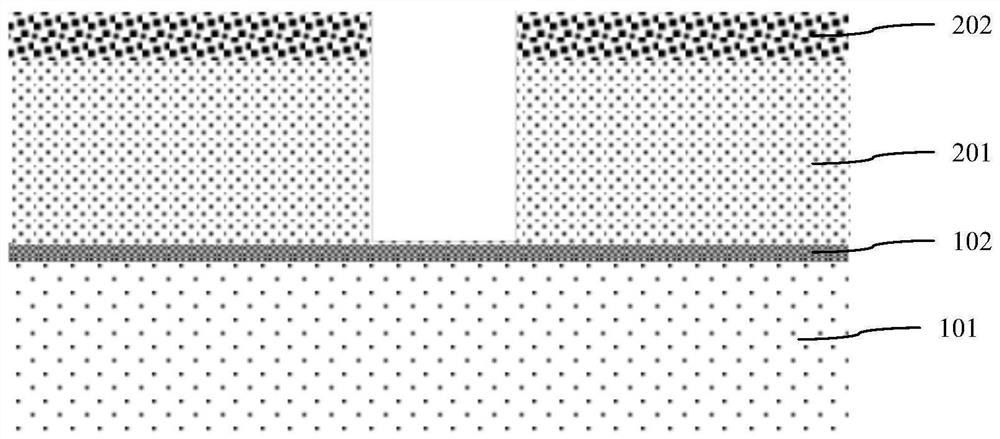

[0039] Such as figure 1 As shown, it is a flow chart of the method for forming the ion implantation region 103 according to the embodiment of the present invention; Figure 2A to Figure 2F As shown, it is a schematic diagram of the device structure in each step of the method of the embodiment of the present invention. The method for forming the ion implantation region 103 of the embodiment of the present invention includes steps:

[0040] Step 1, define the formation area of the ion implantation region 103, including the following sub-steps:

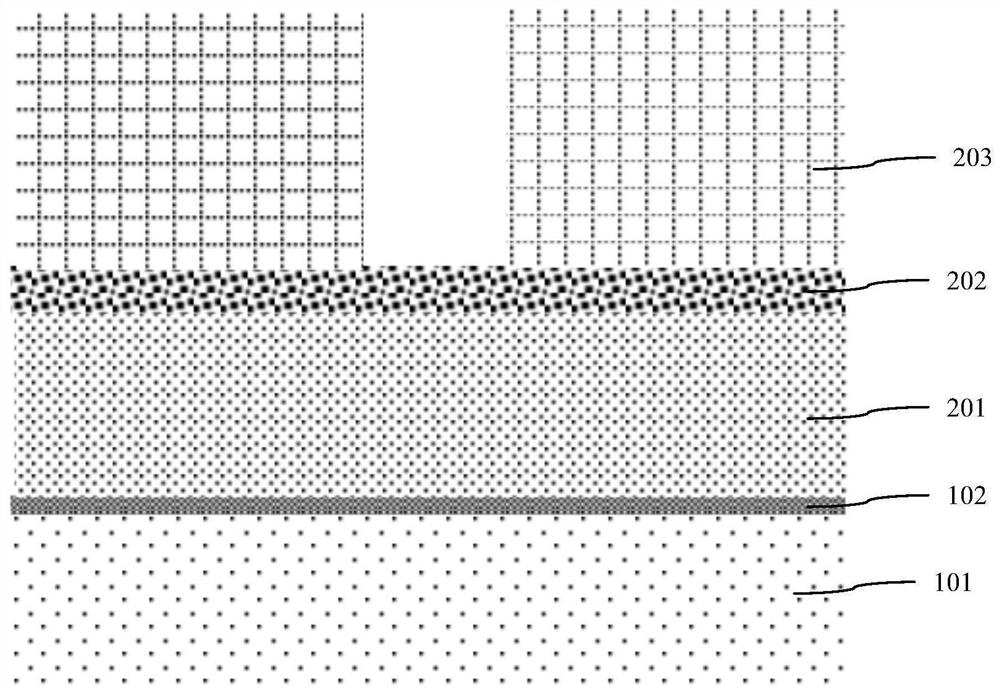

[0041] Step 11, such as Figure 2A As shown, an ODL layer 201 , a SHB layer 202 and a PR layer 203 are sequentially formed on the surface of the underlying structure where the ion implantation region 103 needs to be formed.

[0042] In the embodiment of the present invention, the ODL layer 201 adopts the first carbon coating.

[0043] The SHB layer 202 uses silicon bottom anti-reflection coating.

[0044] The ODL layer 201 , the SH...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More