Optimized digital wireless communication chip system

A communication chip and digital wireless technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems affecting the performance of digital wireless communication chips, complex algorithms of wireless communication systems, and elegant layout and wiring, etc., to achieve Provides radio frequency performance, simplifies board layout rules, and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

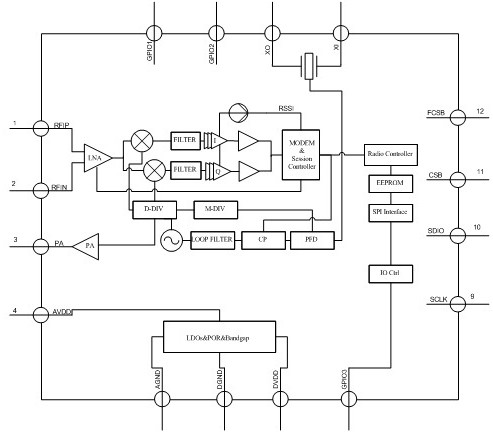

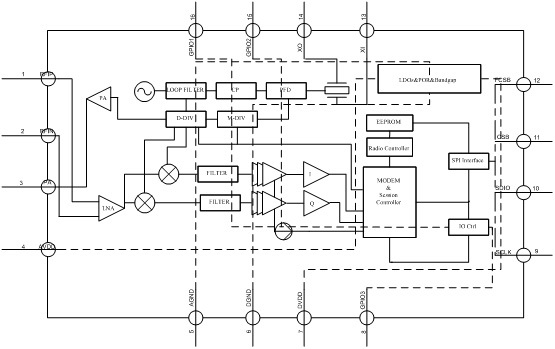

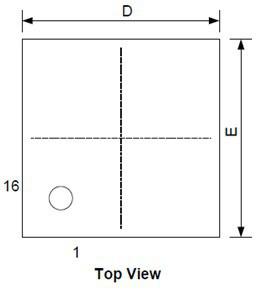

[0025] refer to figure 1 , The digital wireless communication chip system includes a radio frequency controller and EEPROM connected to it, data buffer FIFO, SPI interface, IO controller, RSSI detector, IQ demodulator, LNA, mixer, PA, PLL, VCO, QFN16 package.

[0026] The radio frequency controller adopts an FPGA, the EEPROM is an 8*128bit power-down storage and electric erasable memory array, the data buffer FIFO is a 8*64bits RAM, and the SPI interface is a logical main SPI interface , through CSB, FCSB, SCLK, SDIO four-wire connection to the RF controller, CSB, FCSB, SCLK, SDIO four-wire routing without special process, the connection is only for connection; the IO controller includes logic input and The output circuit is connected to the chip package pins GPIO1, GPIO2, and GPIO3; the RSSI detector is connected to the radio frequency controller, the IQ demodulator is connected to the radio frequency controller through an IPC channel, and the LNA is directly connected to T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More