Patents

Literature

35results about How to "Lower Design Barriers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

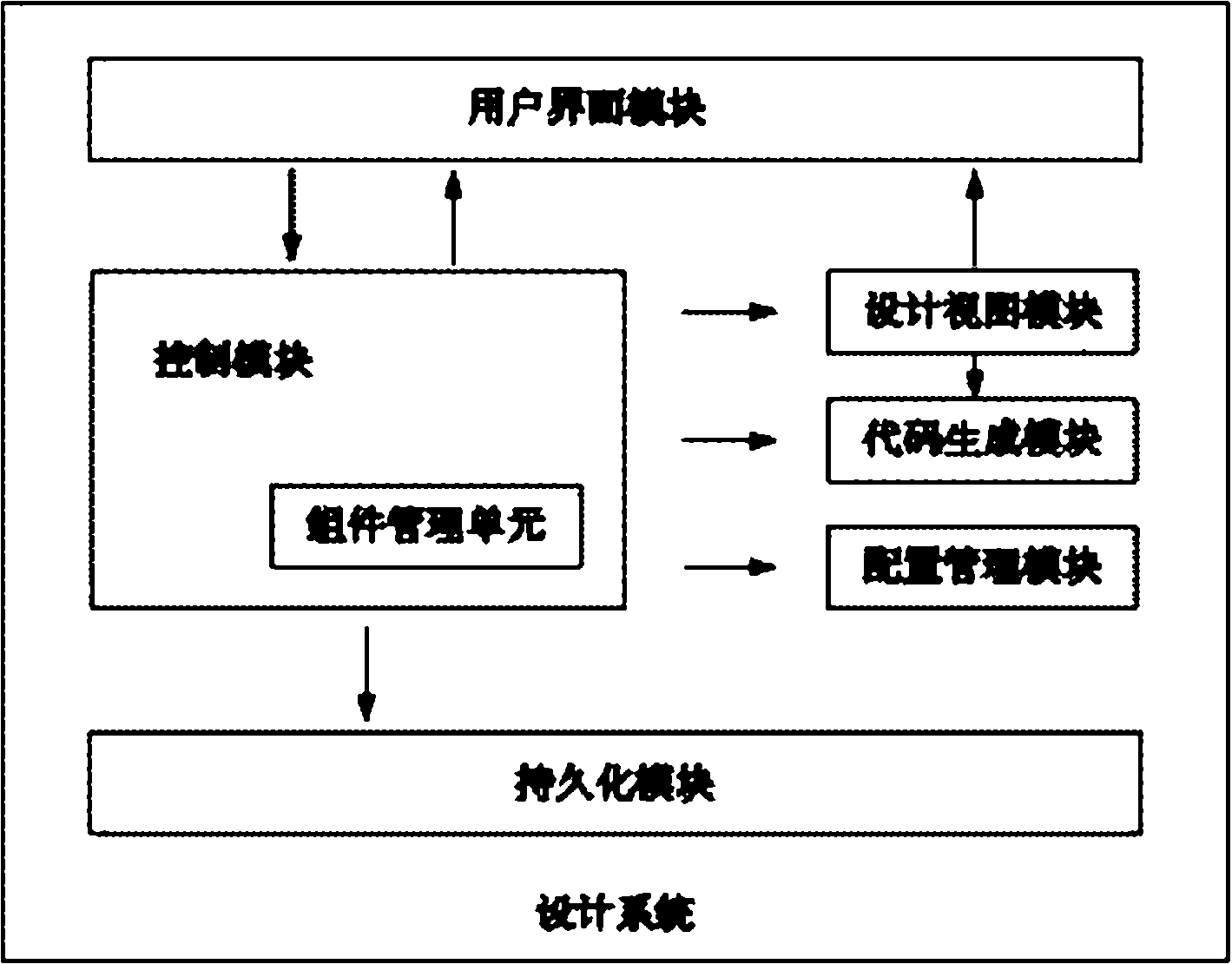

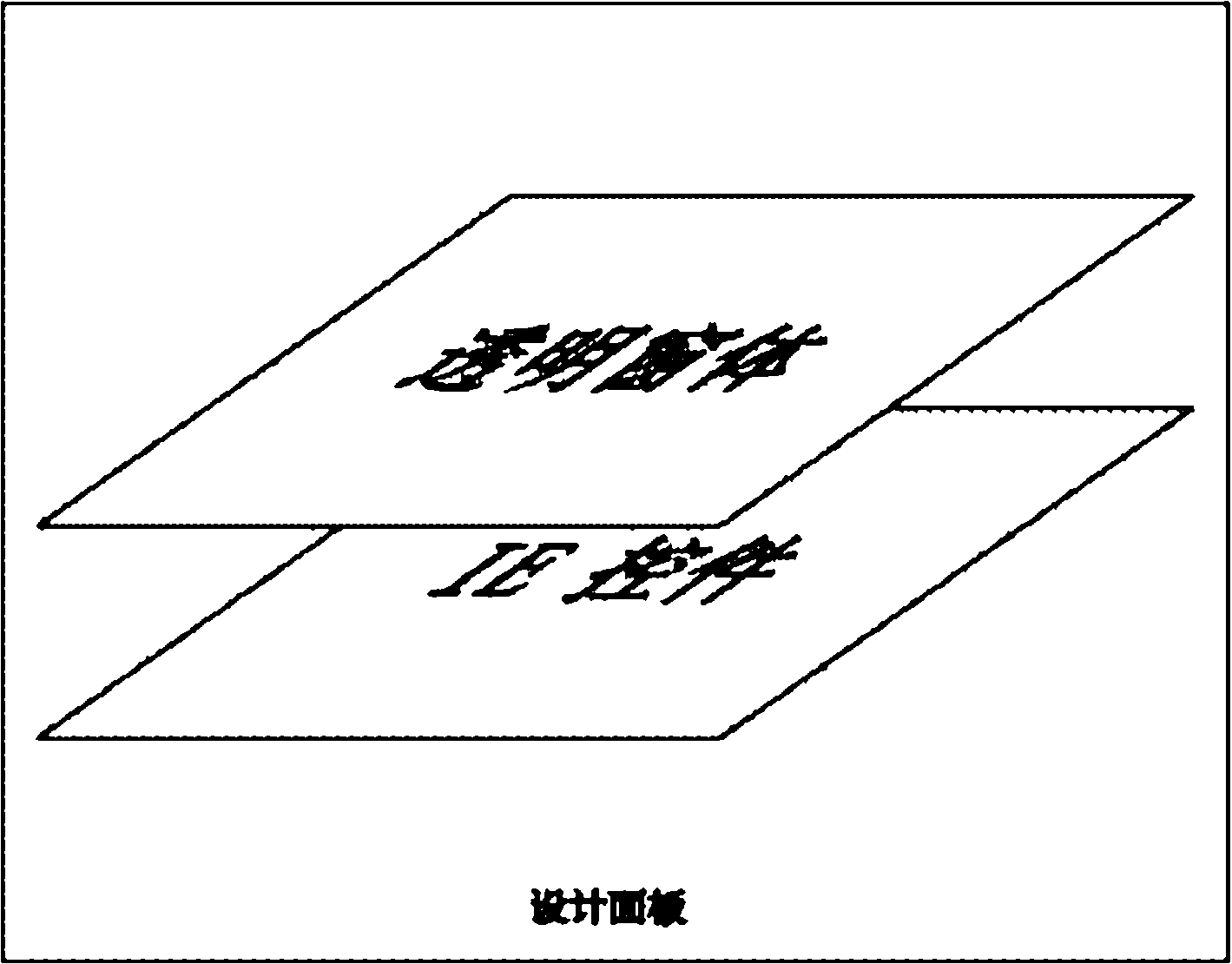

Web page design system and method for building same

InactiveCN102254049AImprove design experienceSimple design and operationSpecial data processing applicationsWeb designWYSIWYG

The invention discloses a Web page design system and a method for building the same. The system comprises: a design component, a design panel and a view control, wherein the design component includes at least one parameter, the design component corresponds to a logic which is capable of generating Hypertext Markup Language codes according to the design component and the parameter, and the logic can be configured by a Web page author; the design panel serves as a working area within which the Web page author performs design and is used for displaying a Web page browsing effect view in the area; and the view control is used for browsing the Web page content generated from the design of the Web page author and providing the Web page browsing effect view. The invention is capable of realizing the presentation of the Web page browsing effect, in particular the effect view after the execution of scripts, on the design panel, thereby enhancing the Web page design experience that what is seen is what is got; the Web page design operation is simplified, and the Web page design efficiency is improved; besides, the Web page design threshold is reduced so that the user group of the Web page design is enlarged.

Owner:程向明

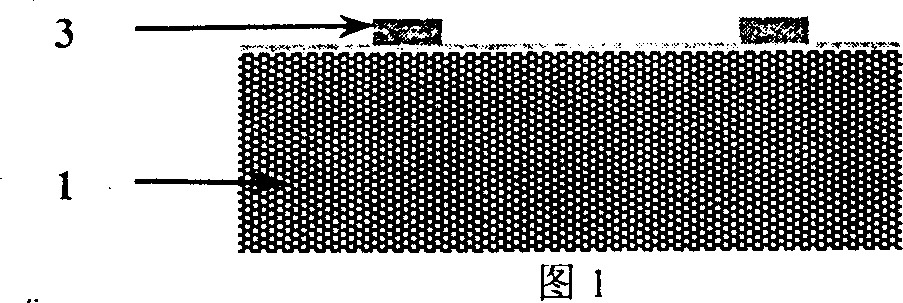

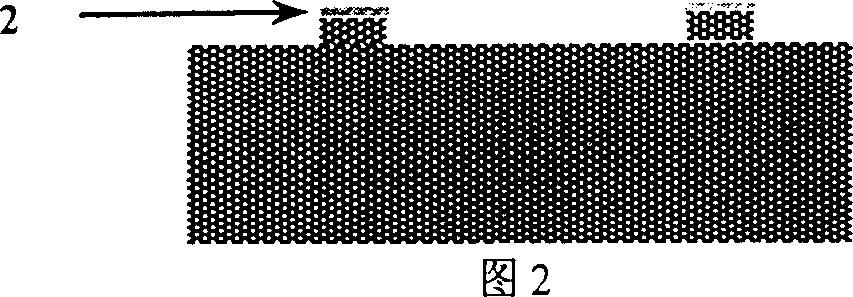

Detecting method and structure for microstructure binding process

InactiveCN1648634AApplicable processabilityApplicable detectabilitySurface/boundary effectScanning probe techniquesBonding processSilicon chip

The present invention relates to detection method and detection structure for micro structure bonding process result. The detection method includes first designing silicon structure pattern; preparing micro structure with silicon structure bonded with silicon substrate or glass substrate via bonding technological process, with the silicon structure having at least one end separated from the bonding surface and the bonding area being recorded; pushing the silicon structure on the no-bonding end with micro probe to make the silicon structure deform until the monocrystal silicon chip breaks from the bonding surface and recording the distance between the probe pushed point and the bonding surface, deformation and the breaking process parameters; and calculating the bonding strength based on the recorded data. The present invention completes MEMS device detection in a simple process.

Owner:PEKING UNIV

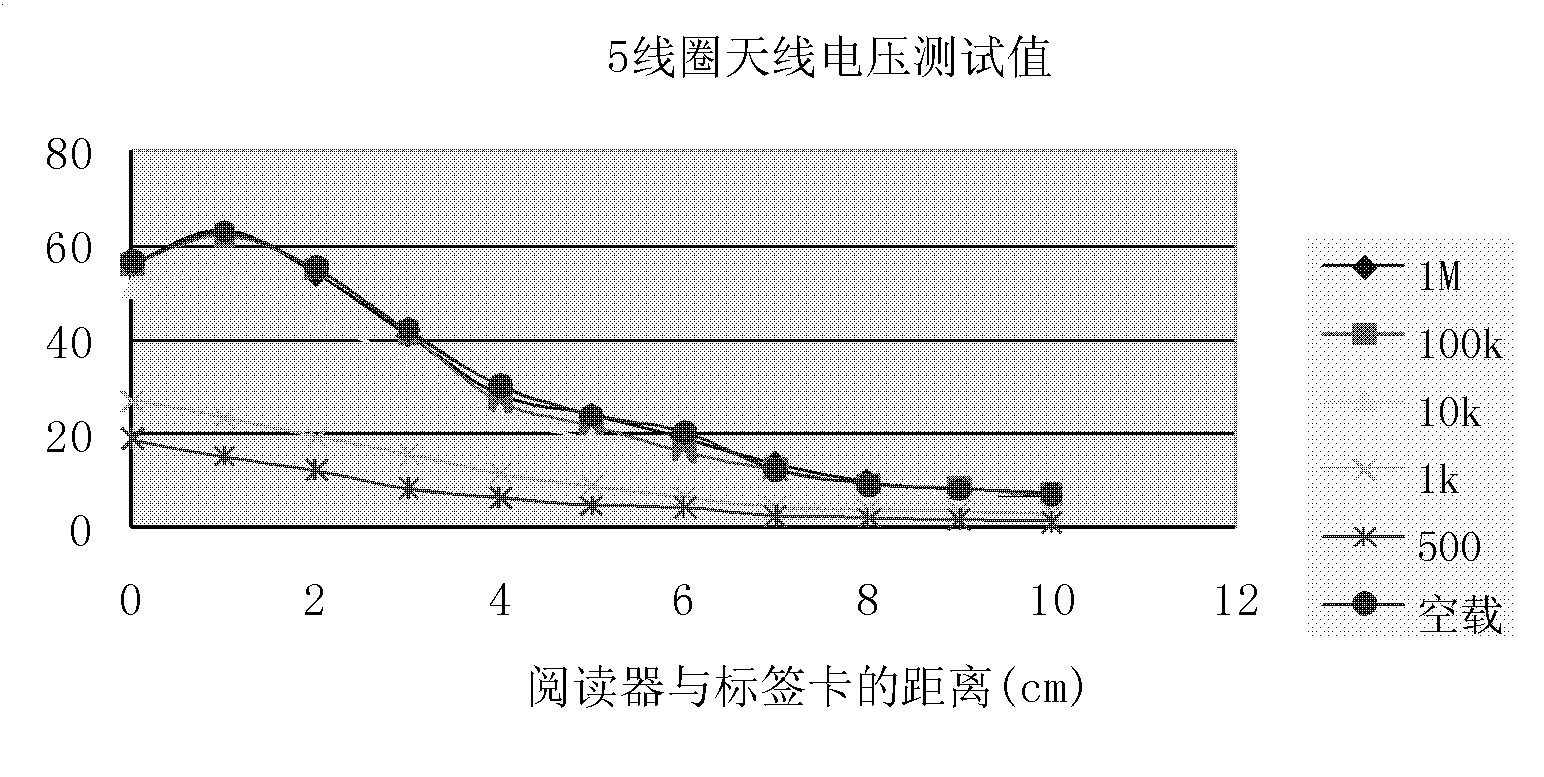

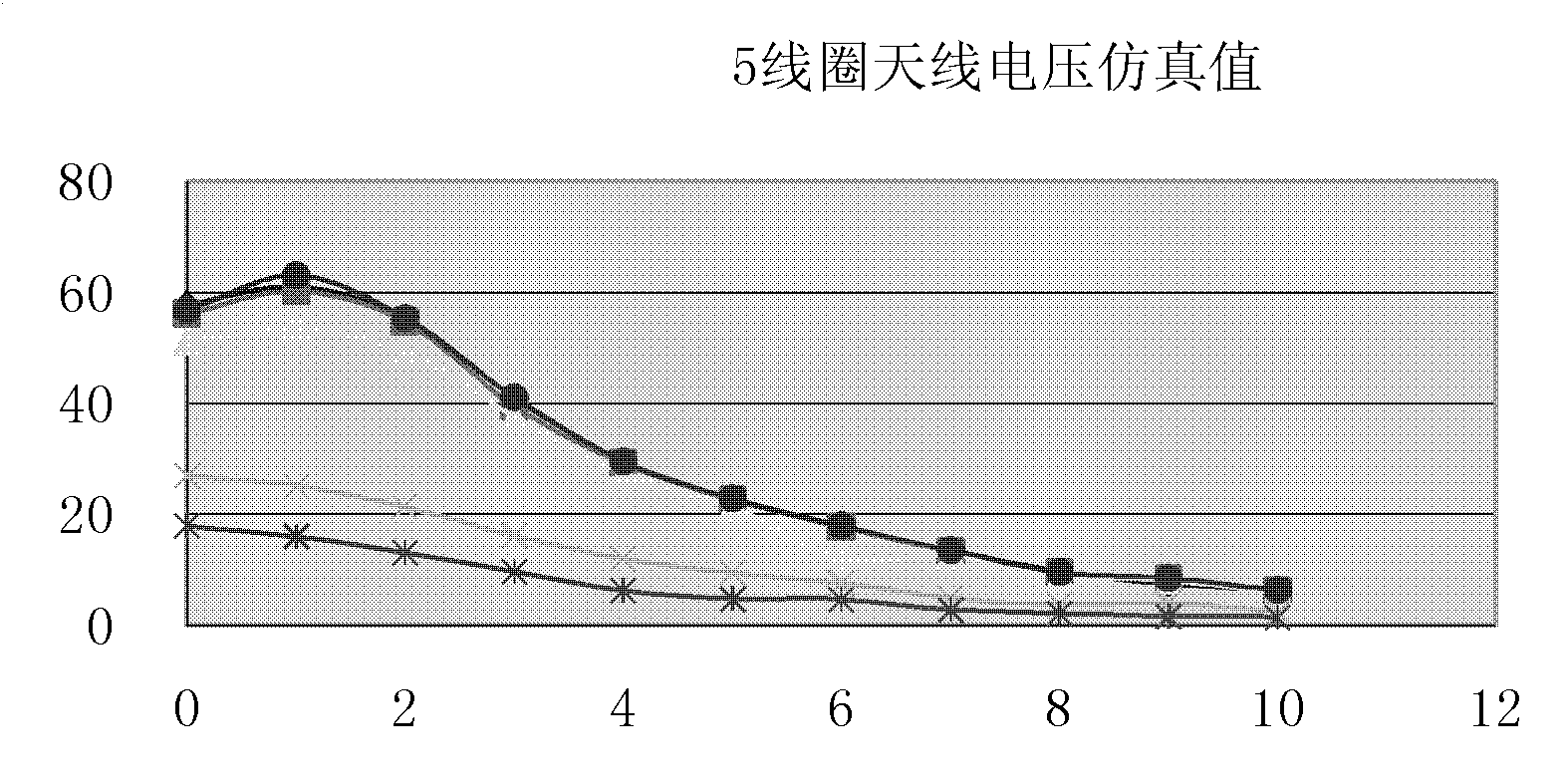

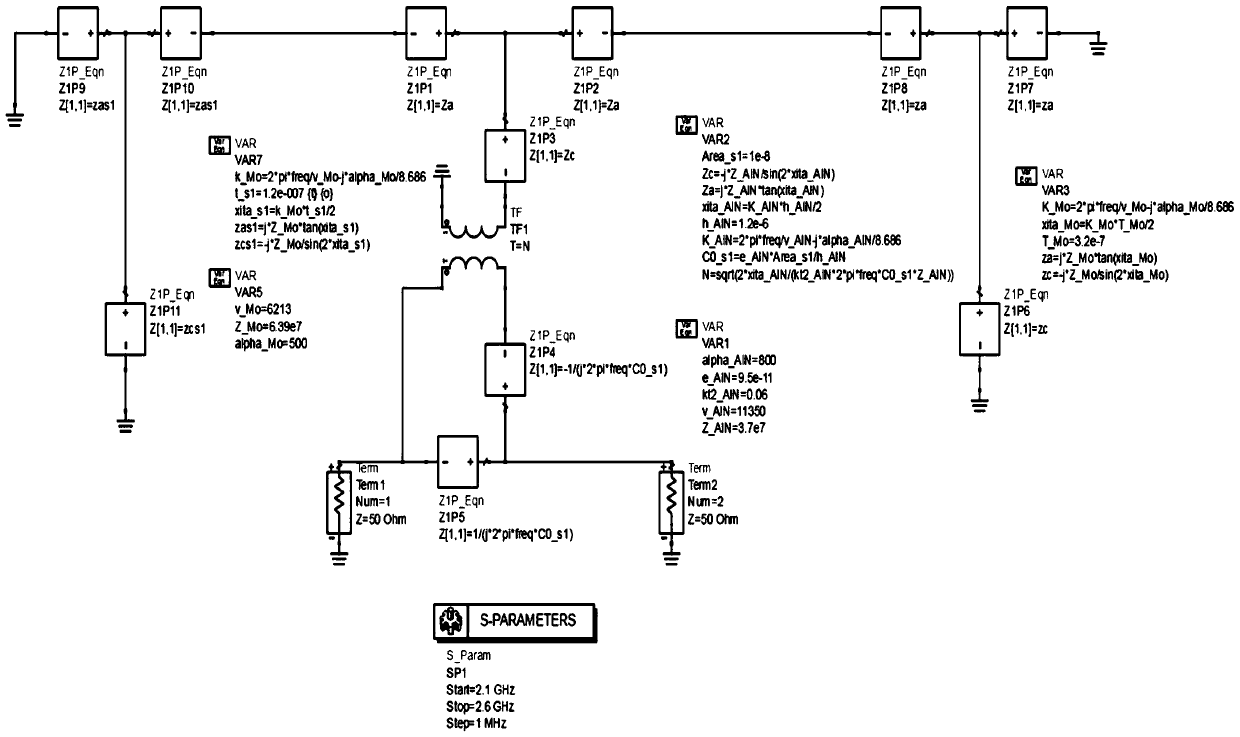

Circuit simulation model for radio frequency identification system

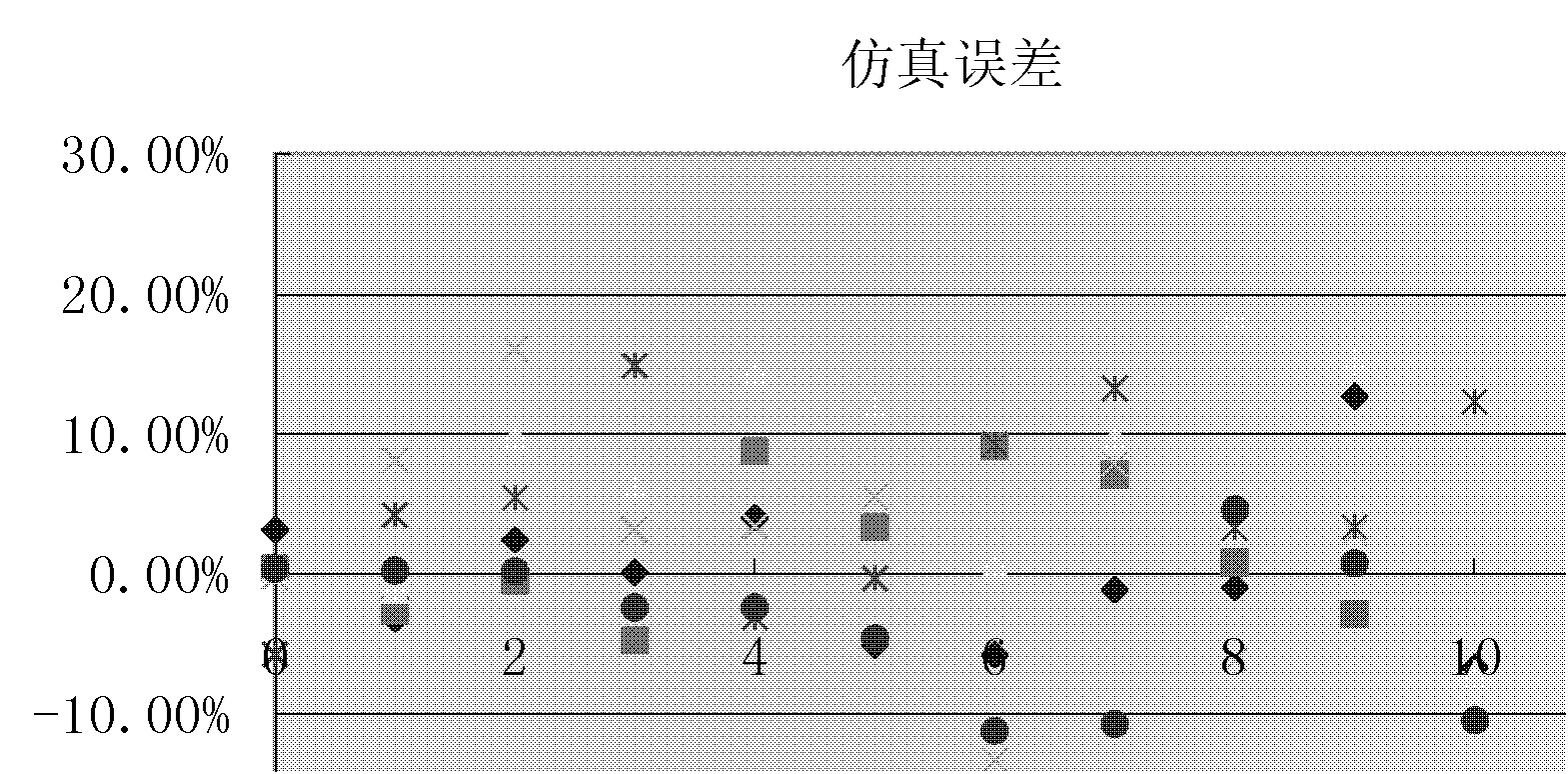

InactiveCN102184442AReduce wafer costShorten the development cycleRecord carriers used with machinesParasitic capacitorCapacitance

The invention discloses a circuit simulation model for a radio frequency identification system, which is used for evaluating the function and the performance of a radio frequency identification tag chip. The circuit simulation model comprises a reader model for simulating the equivalent circuit of an actual reader and generating a 100 percent amplitude shift keying (ASK) modulating signal, a tag card model for simulating the equivalent circuit of an entire tag card which actually comprises a tag chip, a sensing coil model for simulating the equivalent circuits of a printed circuit board (PCB) coil, an oscilloscope and a spectrum analyzer which actually test the depth of a subcarrier load modulation sideband, and a field intensity meter model for simulating the equivalent circuit of an actual field intensity meter. The reader model comprises a 100 percent ASK modulating signal generating circuit, a source impedor, a reader antenna matching network, a reader coil antenna and a reader antenna impedor; the tag card model comprises an on-card antenna inductor, a parasitic resistor, a card parasitic capacitor, a simulated front end circuit and a numerical equivalent load; the sensing coil model comprises two sensing coils, a coil resistor and a spectrum analyzer probe model; and the field intensity meter model comprises a coil inductor and a parasitic capacitor and a parasitic resistor thereof.

Owner:GUANGZHOU SYSUR MICROELECTRONICS

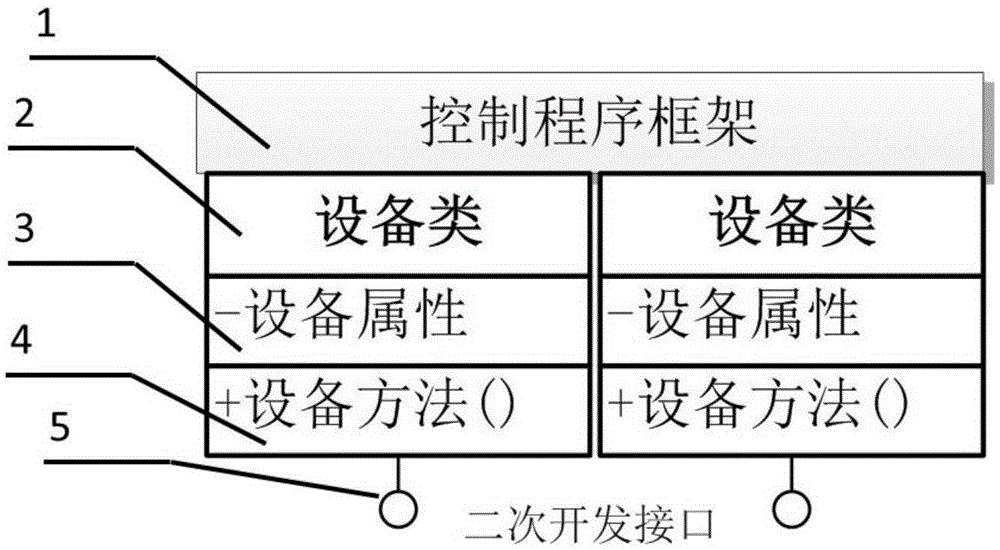

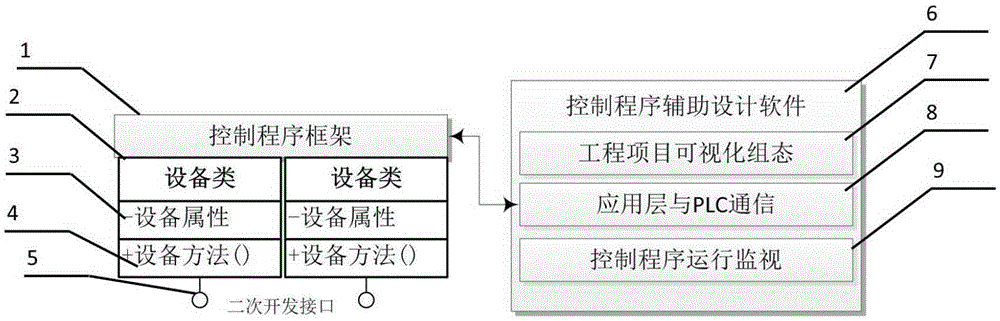

Object-oriented automation logistics control program design method

InactiveCN105302053ALower Design BarriersImprove design accuracyTotal factory controlProgramme control in sequence/logic controllersDevice typeLogistics management

The invention discloses an object-oriented automation logistics control program design method, consisting of a control program framework running in a controller, a device type model, and a control program auxiliary design software running in the computer. The object-oriented automation logistics control program design method reduces the threshold of the control program design by the engineering personnel, improves the programming efficiency, and greatly improves the design accuracy of the control program.

Owner:KUNMING KSEC LOGISTIC INFORMATION IND

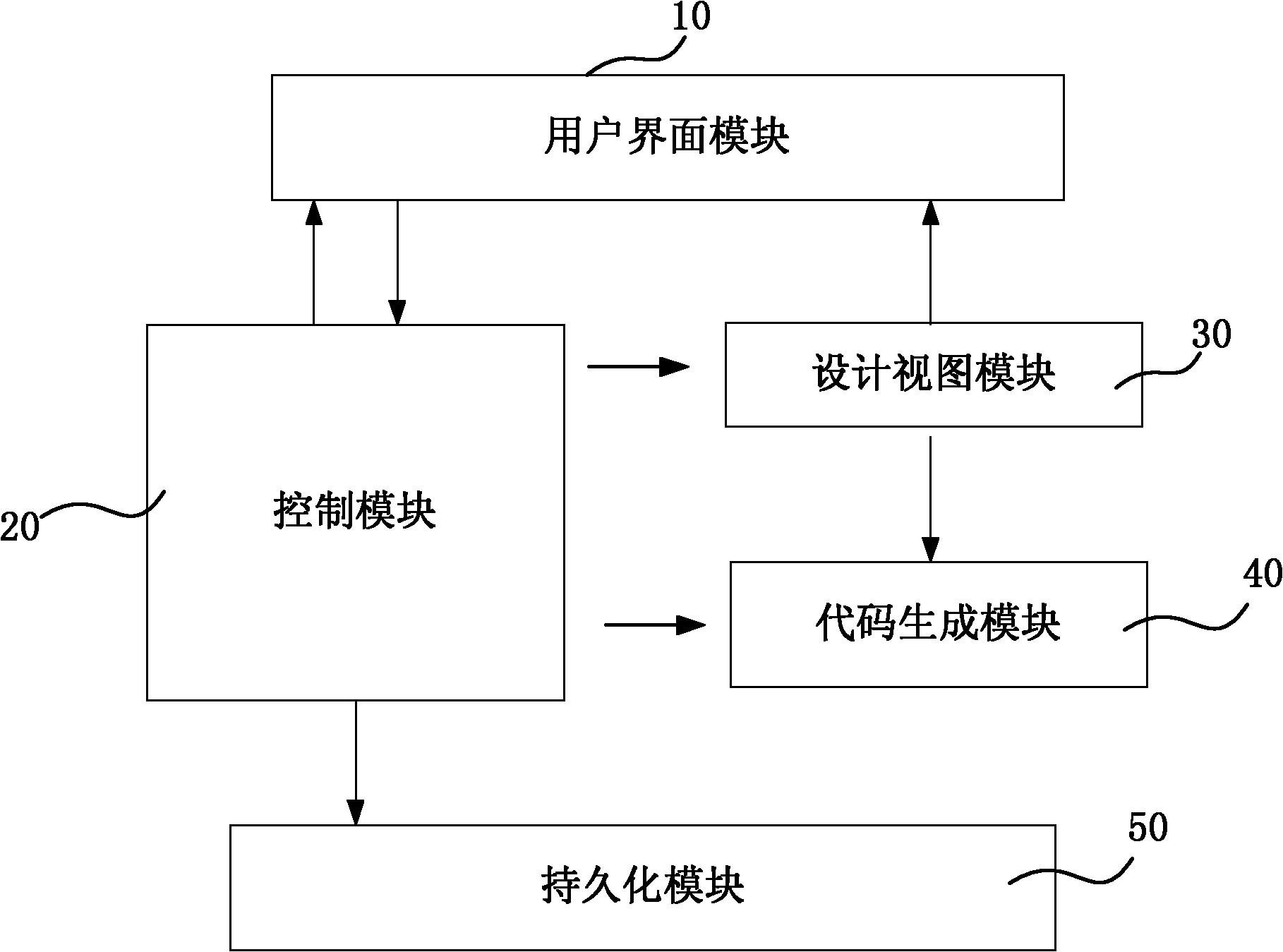

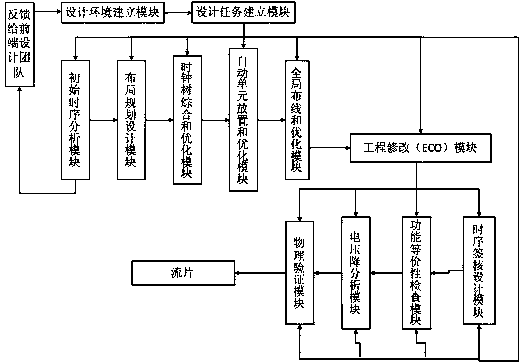

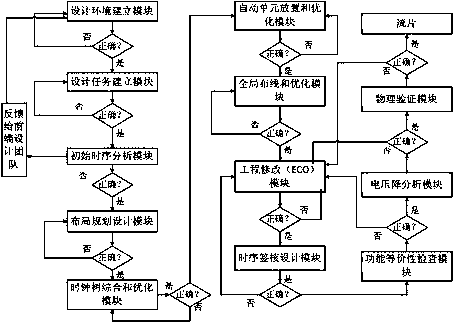

Integrated circuit back end design system and method

InactiveCN108133069AVersatileLower Design BarriersSpecial data processing applicationsLayout planningUltrasound attenuation

The invention discloses an integrated circuit back end design system. The system comprises an environment building module, a design task module, a layout planning design module, an automatic unit placement optimization module, a clock tree synthesis optimization module, a global routing optimization module, a functional equivalence checking module, a timing sign-off design module, a voltage attenuation design module and a physical verification module. According to the integrated circuit back end design system, design sequence standardization is carried out on the main design links of the backend design, so that the design has good universality, thus the design threshold of the back end design is greatly reduced, the labor cost is reduced, the design efficiency is improved, and the designquality is ensured.

Owner:嘉兴倚韦电子科技有限公司

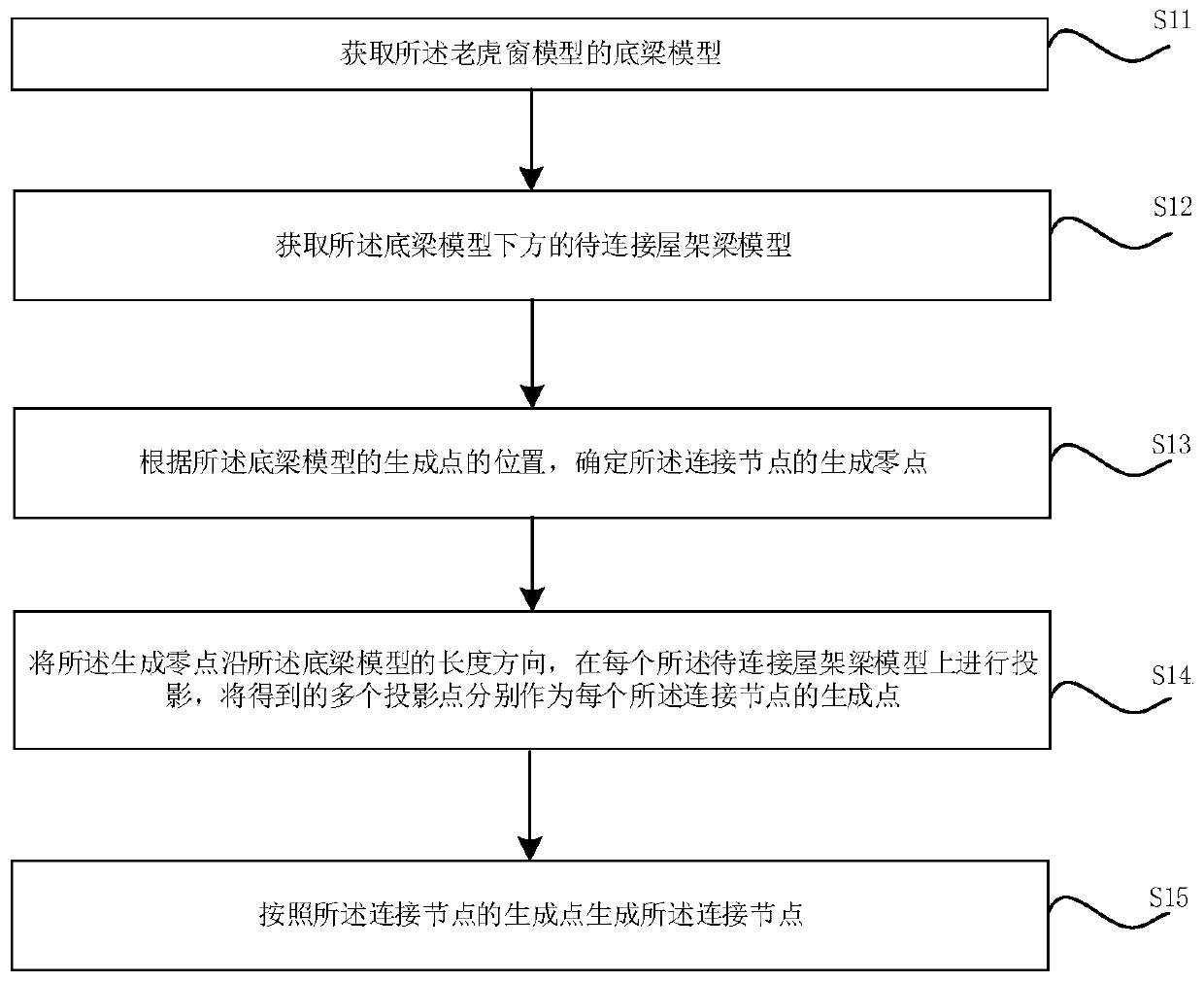

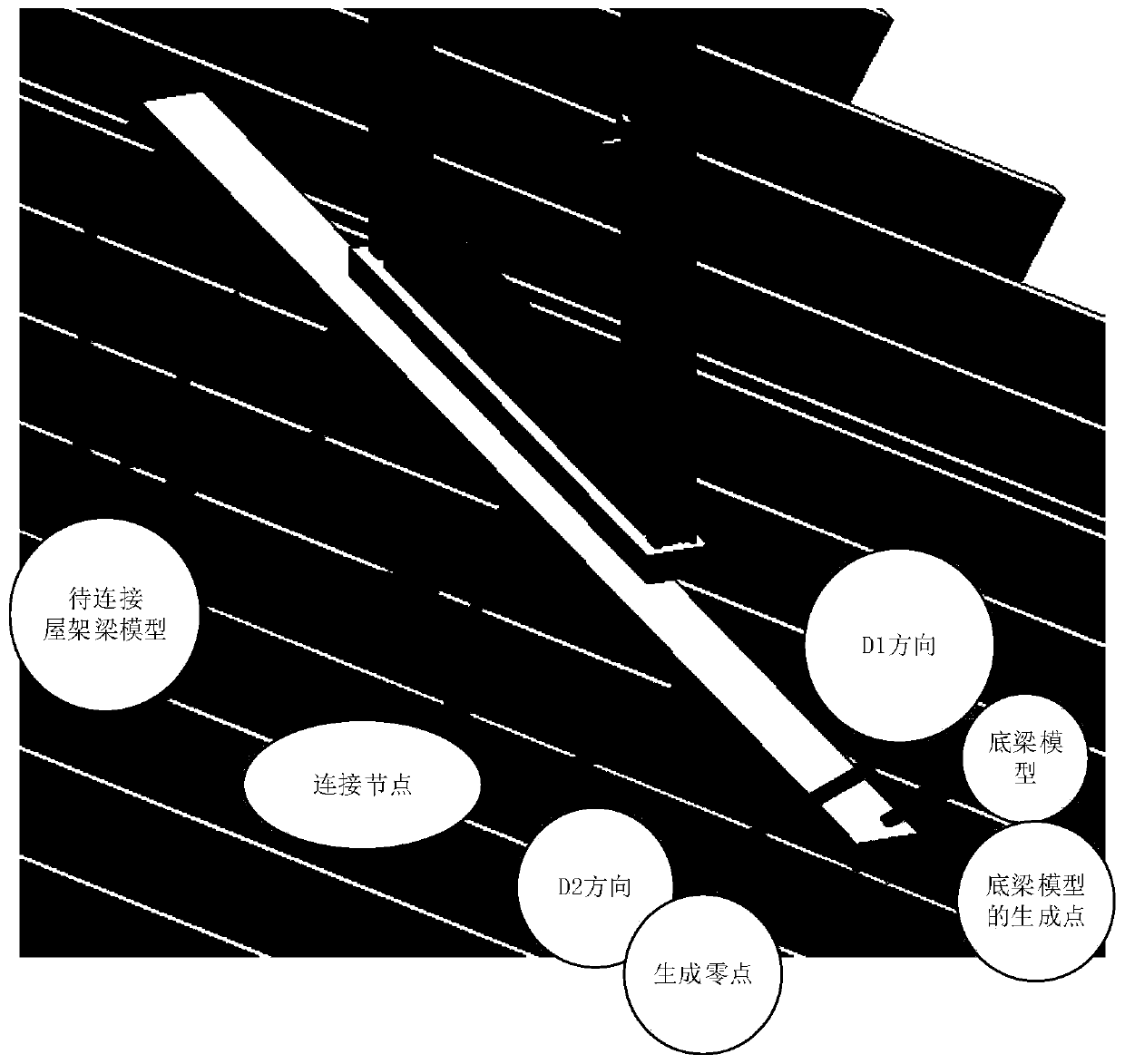

Method and product for placing connection nodes between tiger window model and roof truss beam model

ActiveCN110704898AImplement automatic placementImplementation inefficienciesGeometric CADDesign optimisation/simulationAlgorithmStructural engineering

The invention relates to a method and a product for placing a connection node between a tiger window model and a roof truss beam model. The method comprises the following steps: 1, ; obtaining a bottom beam model of the tiger window model and a to-be-connected roof truss beam model below the bottom beam model; the method comprises the steps of obtaining a plurality of to-be-connected roof truss beam models, determining generation zero points of connection nodes according to positions of generation points of the bottom beam models, then projecting the generation zero points on each to-be-connected roof truss beam model in the length direction of the bottom beam models, taking the obtained projection points as the generation points of each connection node, and finally generating the connection nodes according to the generation points of the connection nodes. According to the method, the placing difficulty of the connection node and the placing efficiency of the connection node are improved.

Owner:久瓴(江苏)数字智能科技有限公司

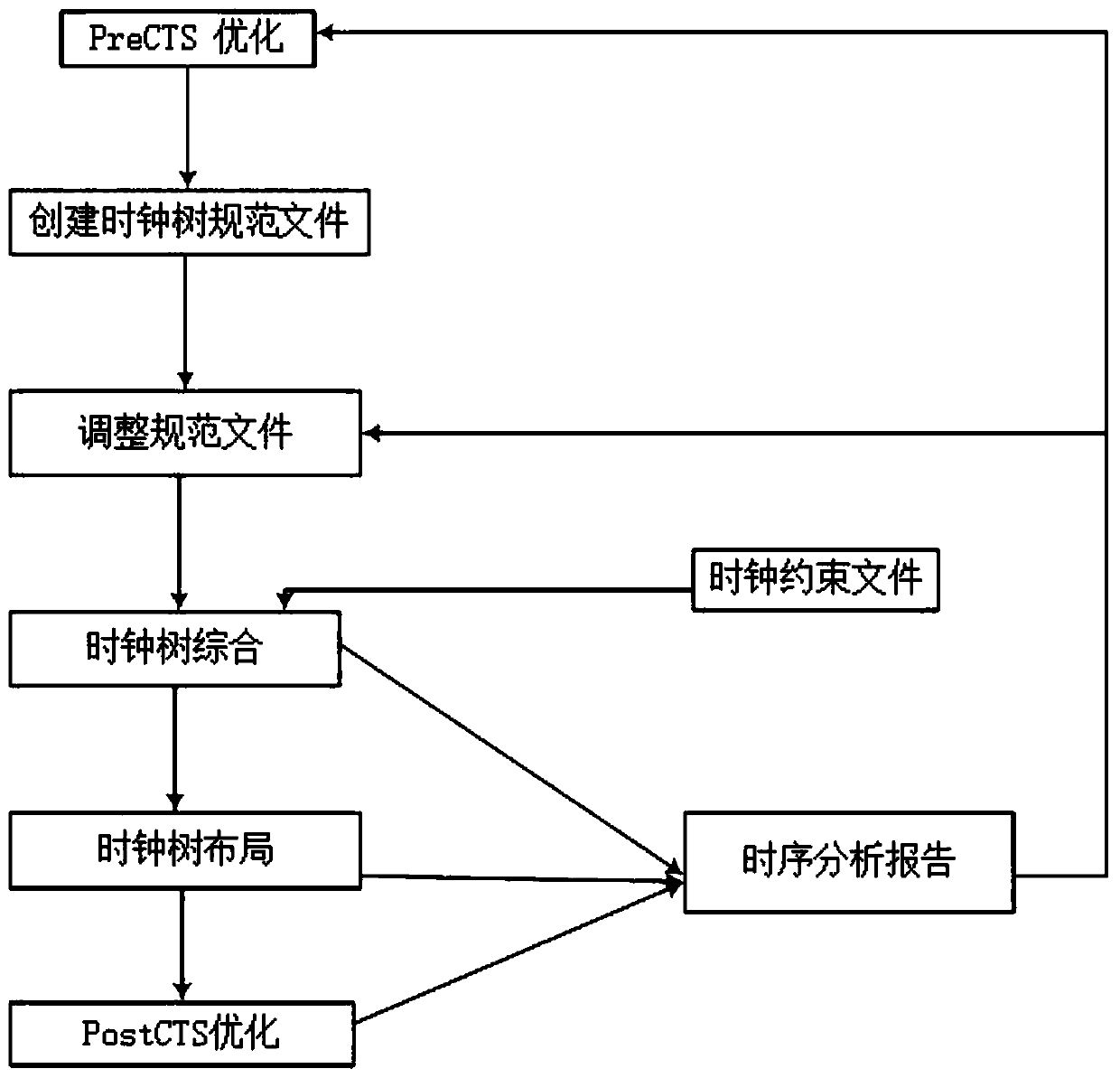

Integrated circuit clock tree comprehensive optimization method

InactiveCN110807295AIncrease the probability of being rightLower Design BarriersComputer aided designSpecial data processing applicationsIntegrated circuitClock signal

The invention relates to the technical field of integrated circuit design industry automation (EDA), and provides an integrated circuit clock tree comprehensive optimization method, which comprises the following steps of S1, presetting parameters in a clock tree constraint file; s2, automatically generating a line layout according to the parameters; s3, adjusting the positions of registers in thecircuit layout to enable the difference value between the clock source and the wiring length of each register to be within a preset range; s4, arranging a plurality of driving units at the clock signal source, wherein the driving units are used for driving loads of the clock tree; and S5, replacing the driving units to enable the driving capacities of the driving units to be the same. Through thedesign, the most important clock tree comprehensive design link in the integrated circuit rear-end design process is subjected to design sequence standardization, so that the clock tree comprehensivedesign link has good universality, the design threshold of the rear-end link is reduced, the labor cost is reduced, the design efficiency is improved, and the design quality is ensured.

Owner:SHANGHAI UNIV

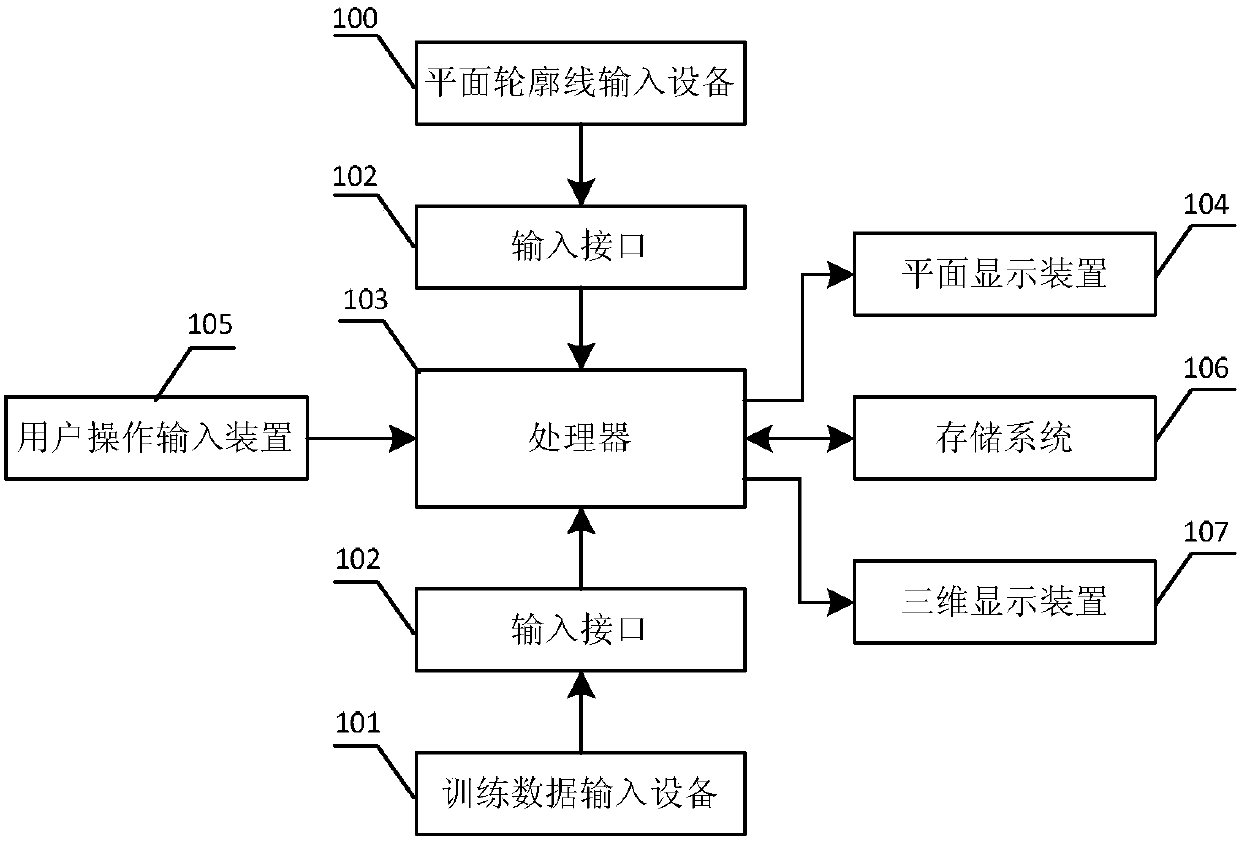

Device and method for automatically generating contour line of plane of shoe last

InactiveCN108062782AImprove efficiencyOmit the iterative modification processDrawing from basic elementsModifying/creating image using manual inputStochastic gradient descentComputer graphics (images)

The invention provides a device and a method for automatically generating a contour line of the plane of a shoe last, and relates to the technical field of generation of digital models of shoe lasts.The invention aims at solving the problem that artificial design is low in efficiency of shoe last model drawing. A sample database is established by using the contour lines of the planes of existingshoe lasts or shoe lasts in drawings, and generator networks are trained by using a random gradient descent method and samples in the sample database, so that the optimal generator network is obtained. Part of the contour line, drawn by a user, of the plane of the shoe last is collected, and the contour line of the plane is input into the optimal generator network, so that the contour line, conforming to the style of the user, of the plane of the shoe last can be obtained.

Owner:哈尔滨福特威尔科技有限公司

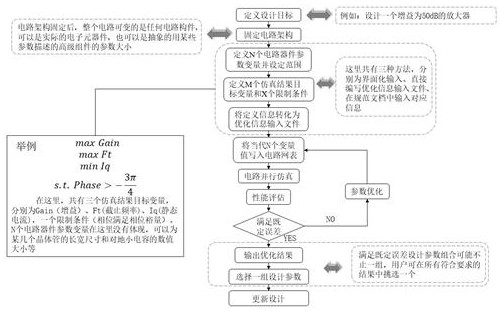

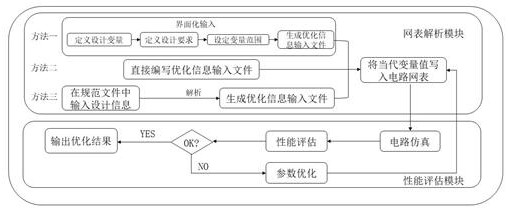

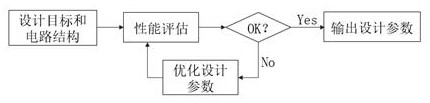

Analog integrated circuit design parameter automatic optimization scheme based on artificial intelligence algorithm

PendingCN112417803AImprove design efficiencyLower Design BarriersCAD circuit designSpecial data processing applicationsAlgorithmEngineering

The invention discloses an analog integrated circuit design parameter automatic optimization scheme based on an artificial intelligence algorithm, and relates to the technical field of integrated circuit design, and the scheme comprises the following steps: A1, defining a design target; A2, fixing a circuit architecture; A3, defining N circuit device parameter variables and setting a range; and A4, defining M simulation result target variables and X limiting conditions, wherein the steps comprise a method I, a method II and a method III. According to the analog integrated circuit design parameter automatic optimization scheme based on an artificial intelligence algorithm, the whole optimization process is unified into one environment, so that the whole design is more convenient and efficient, three solutions are given in the netlist analysis module, and the use habits of different users can be met.

Owner:苏州复鹄电子科技有限公司

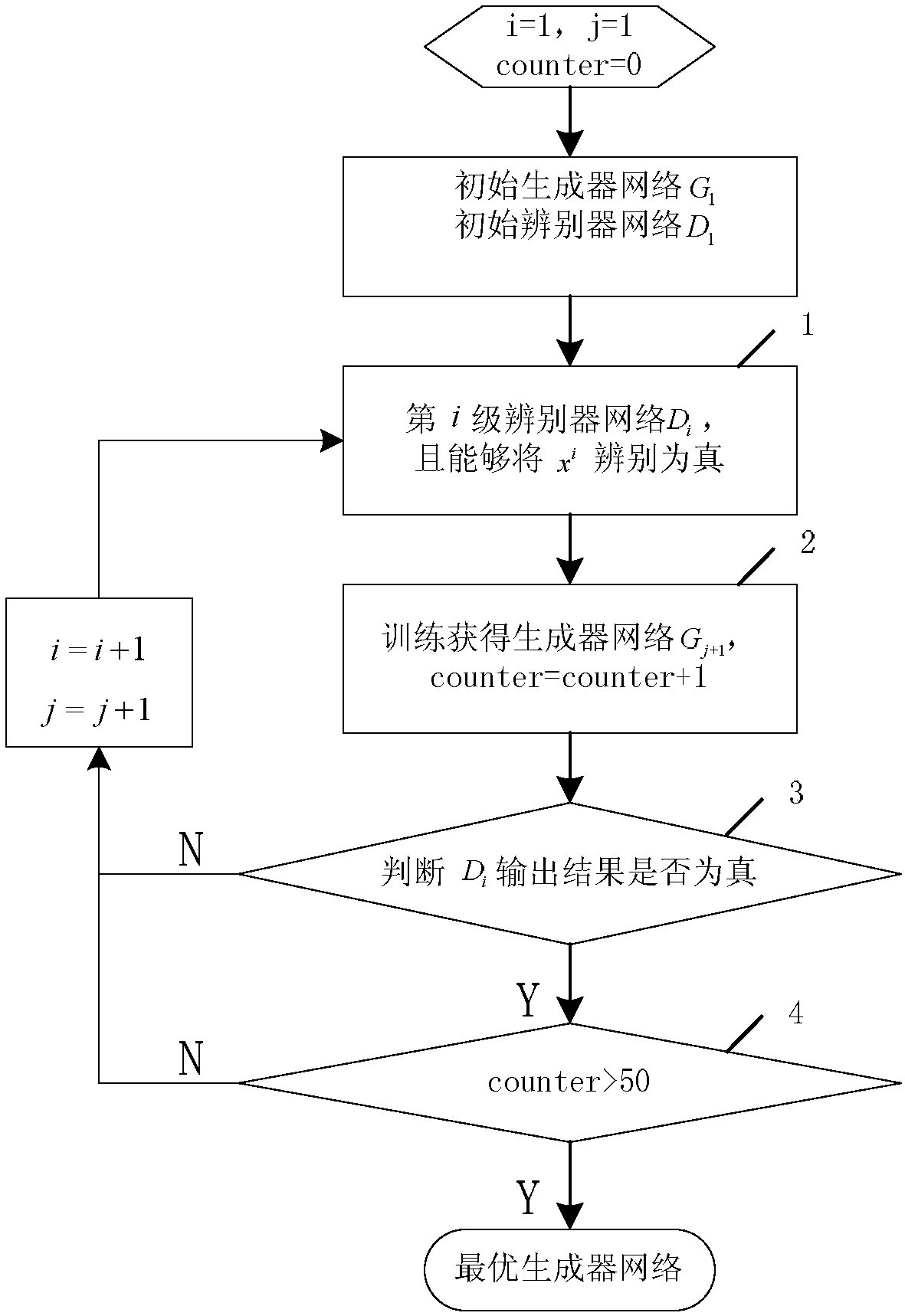

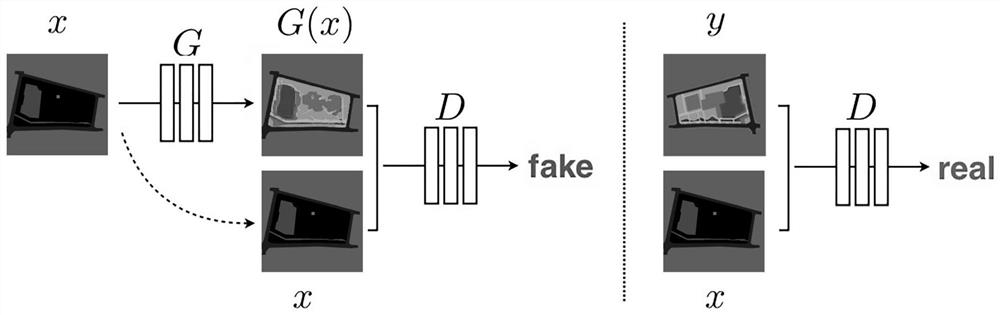

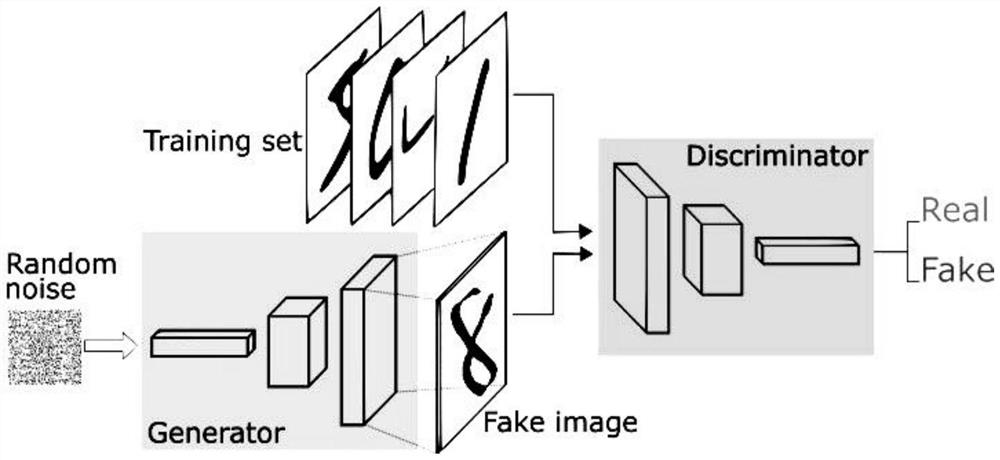

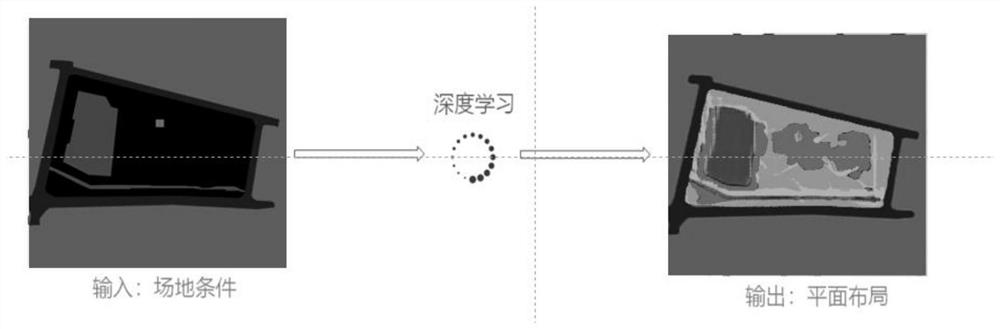

Image processing method and system in garden design based on generative adversarial network

InactiveCN112861217ABroaden your mindLower Design BarriersGeometric CADDesign optimisation/simulationData setImaging processing

The invention belongs to the technical field of image processing in garden design, and discloses an image processing method and system in garden design based on an adversarial generative network. The method comprises the steps: obtaining a data set for training, the data sets are respectively a site environment condition graph before design and a garden design plane layout conceptual graph after design, then training the data sets according to a GAN iterative training method and a picture translation generation method, and generating the garden design plane layout conceptual graph. The GAN comprises a generator which is used for generating tasks, has one input according to different tasks, and then outputs corresponding pixel images. The discriminator is used for discriminating whether the picture is true or false, the input is the picture, and the output is a label for discriminating the picture. A traditional design mode can be changed by utilizing an intelligent generation design technology, and the effects of reducing the design threshold, improving the design efficiency, optimizing the design quality, expanding the thought of a designer and stimulating the design inspiration of the designer are achieved.

Owner:CHONGQING JIAOTONG UNIVERSITY +1

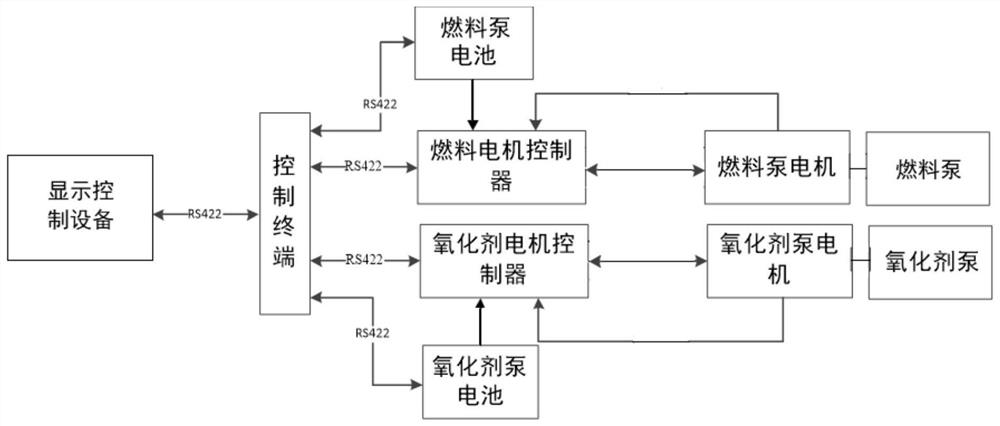

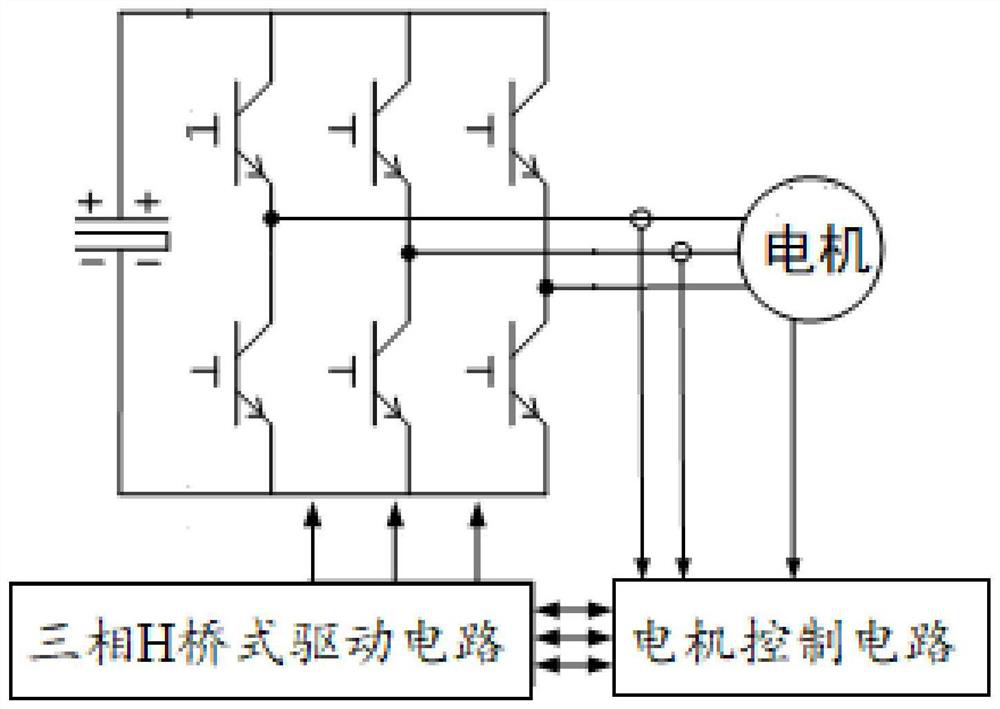

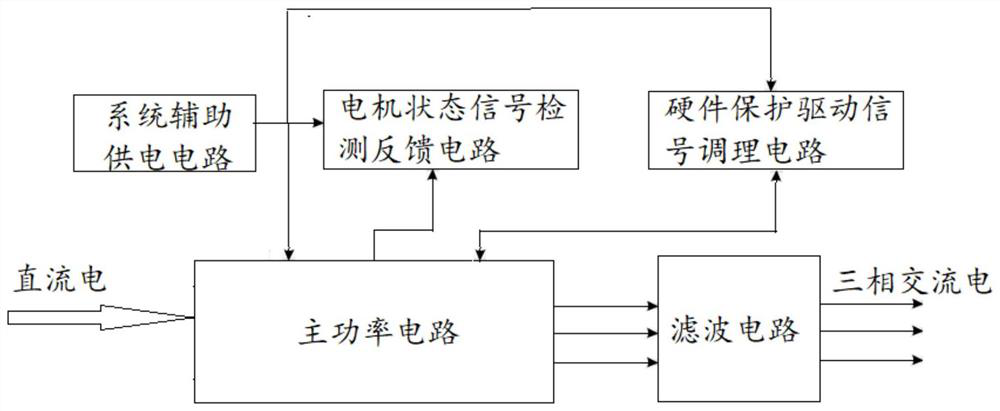

Variable thrust liquid engine electric drive control propellant supply system

InactiveCN111654227APrecise adjustment of thrustThrust changeAC motor controlMultiple motor speed/torque controlMotor speedElectric machine

The invention provides a variable thrust liquid engine electric drive control propellant supply system, which comprises: a control terminal used for controlling the on-off of a power supply, the rotating speeds of a fuel pump motor and an oxidant pump motor, and the opening and closing of various valves of an engine; a fuel pump motor controller used for adjusting the rotating speed of the fuel pump motor; an oxidant pump motor controller used for adjusting the rotating speed of the oxidant pump motor; the fuel pump motor for driving a fuel pump; the oxidant pump motor used for driving an oxidant pump; the fuel pump for conveying fuel to a thrust chamber; the oxidant pump used for conveying an oxidant to the thrust chamber; and a direct-current power supply used for supplying power to thefuel pump motor controller and the oxidant pump motor controller. According to the invention, the original mechanical turbine is replaced by an electric drive motor control mode, and the fuel pump motor and the oxidant pump motor are controlled by the control terminal to be repeatedly started and paused, so that the purposes of repeated starting of the liquid engine and accurate thrust adjustmentare achieved, and the practicability of the liquid engine in the field of recycling and reusing is greatly improved.

Owner:江苏深蓝航天有限公司

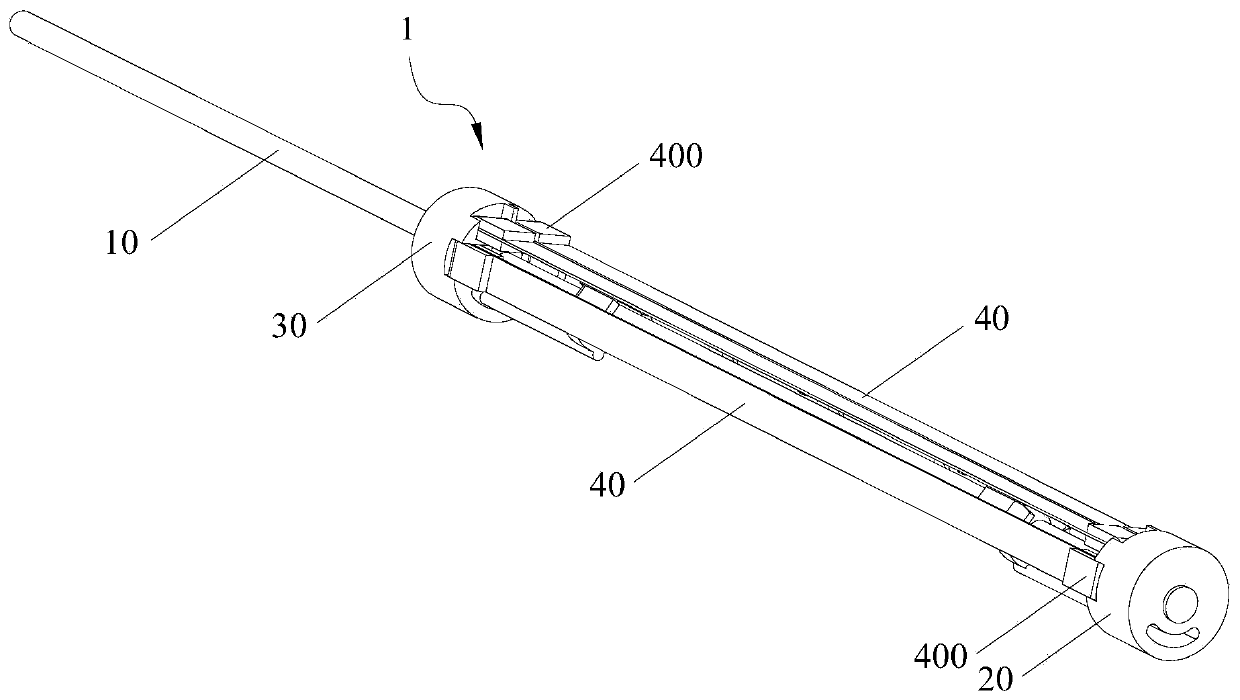

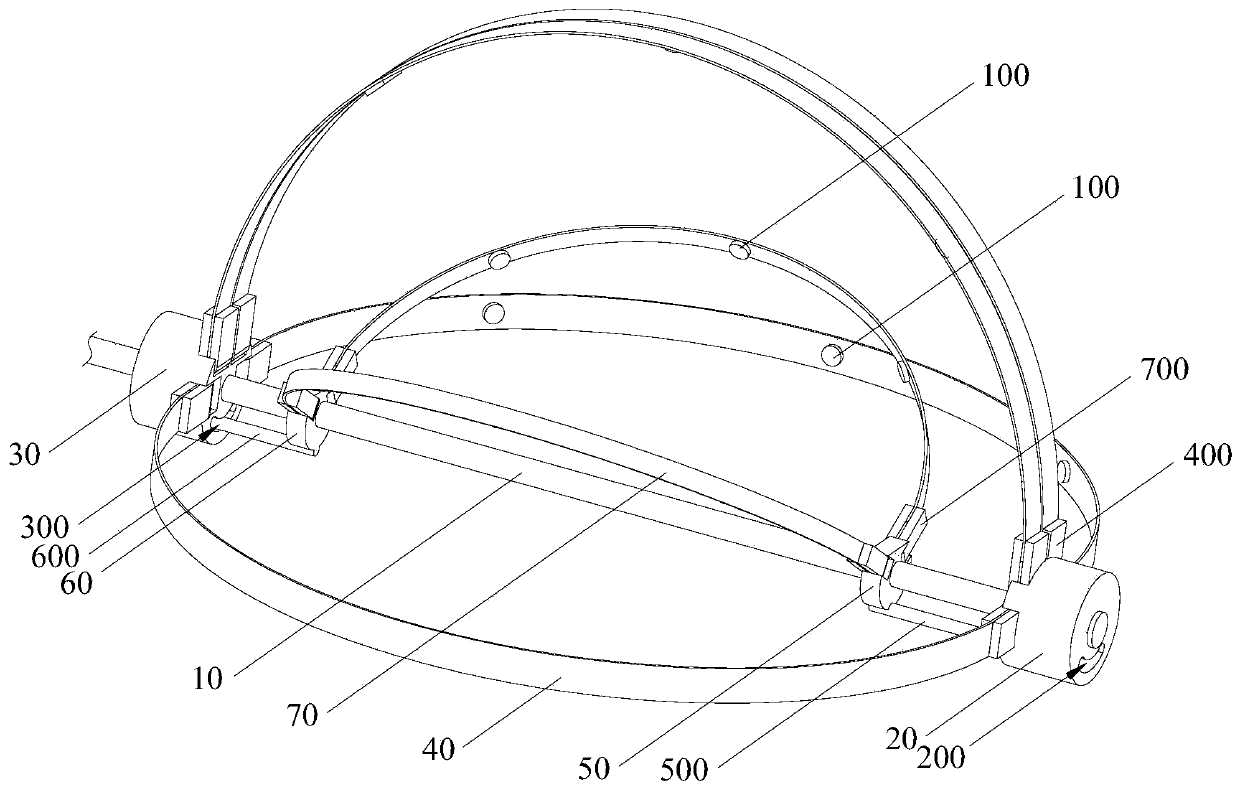

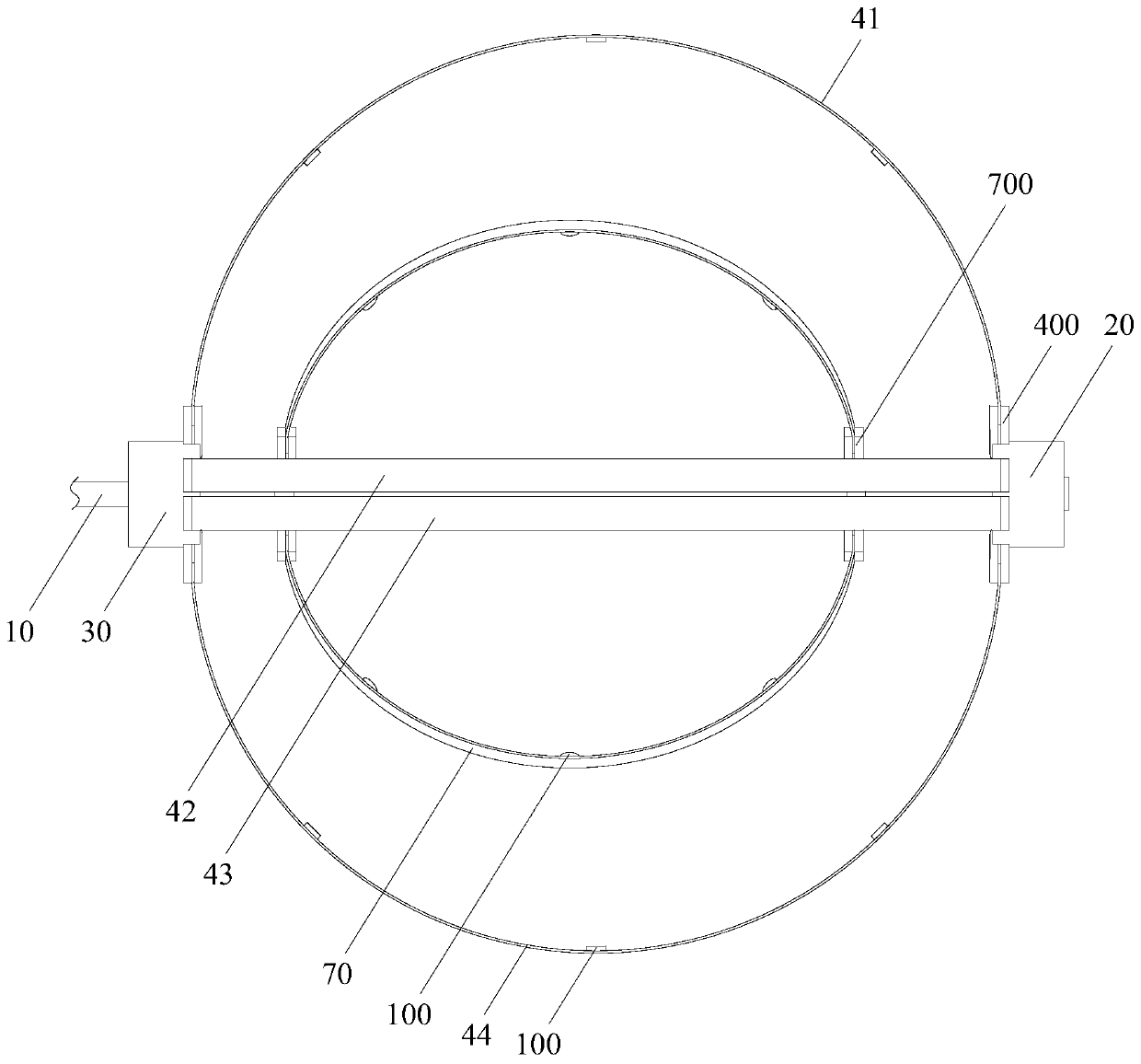

Auxiliary device for natural orifice transluminal endoscopic surgery

ActiveCN110693541AIncrease operating spaceImprove operational flexibilitySurgical field illuminationLaparoscopesEndoscopic Procedure

The invention provides an auxiliary device for natural orifice transluminal endoscopic surgery, which comprises a support rod; a fixing block fixed at one end of the supporting rod; a sliding block arranged on the supporting rod in sleeving manner and capable of reciprocating along the supporting rod; and at least three first elastic sheets distributed at intervals, the first end of the first elastic sheet being hinged to the fixing block, the second end of the first elastic sheet being hinged to the sliding block, and a permanent magnet being arranged on the inner surface of the first elasticsheet. According to the invention, the first elastic sheet is bent and arched by pushing the sliding block on the supporting rod; a larger operating space is formed within a target surgical area; surgical tools such as a laparoscope, an illumination light source and a clamp for abdominal surgery can be anchored in the operating space through the permanent magnet on the first elastic sheet; and therefore, It is convenient for doctors to perform surgery. The need for special surgical tools for natural orifice transluminal endoscopic surgery is avoided, so that the technical problem that a common abdominal operating instrument cannot meet the requirements of natural orifice transluminal endoscopic surgery is effectively solved.

Owner:深圳市文远实验室有限公司

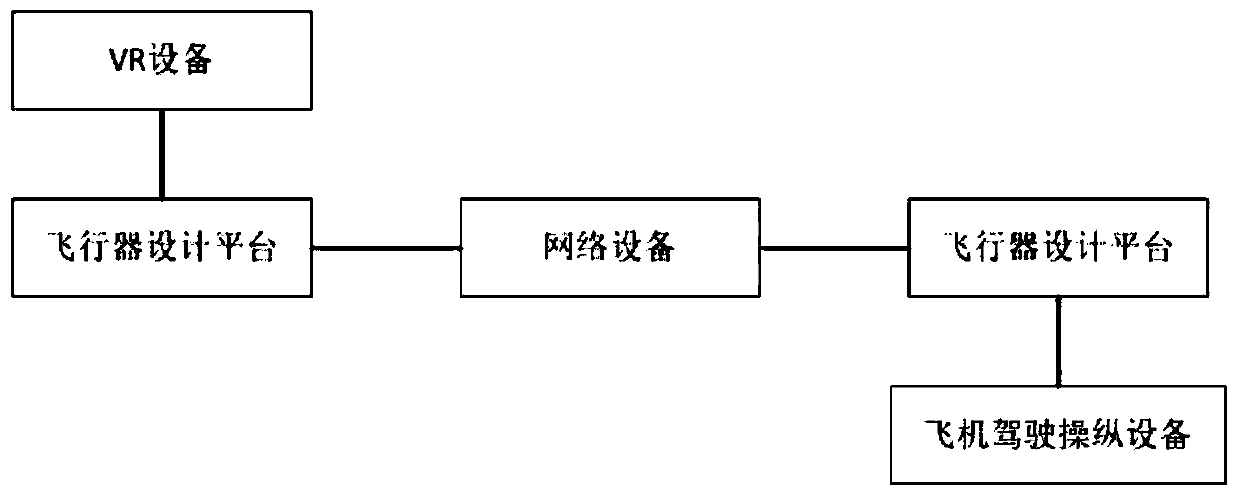

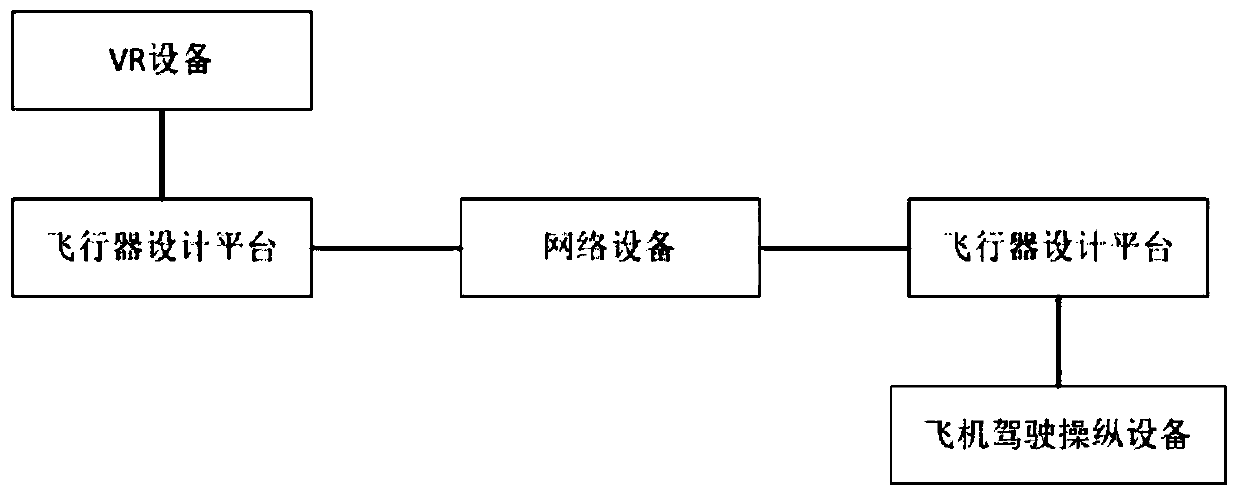

Aircraft design platform, aircraft design and software simulation system and method

ActiveCN110046455ALowering the Barrier to Access to Aircraft DesignLower Design BarriersGeometric CADConfiguration CADAviationSoftware emulation

The invention discloses an aircraft design platform, an aircraft design and software simulation system and method. The system comprises an aircraft design platform, an aircraft simulation system and an aircraft driving control device. The aircraft design platform is used for designing an aircraft model and storing configuration data of the aircraft model; aircraft simulation system. The aircraft simulation system is in data communication with the aircraft design platform and is used for receiving configuration data of an aircraft model of the aircraft design platform and providing a test flight scene for the aircraft model, and the aircraft simulation system is also used for receiving a control instruction of aircraft driving control equipment and realizing test flight under the control ofthe control instruction. According to the system and the method, the aircraft is driven through the simulated aircraft, any safety risk is avoided, various competitive games can be handled, scientific and innovative spirits are spread, and promotion of aviation science popularization education is facilitated.

Owner:珠海大川航空科技有限公司

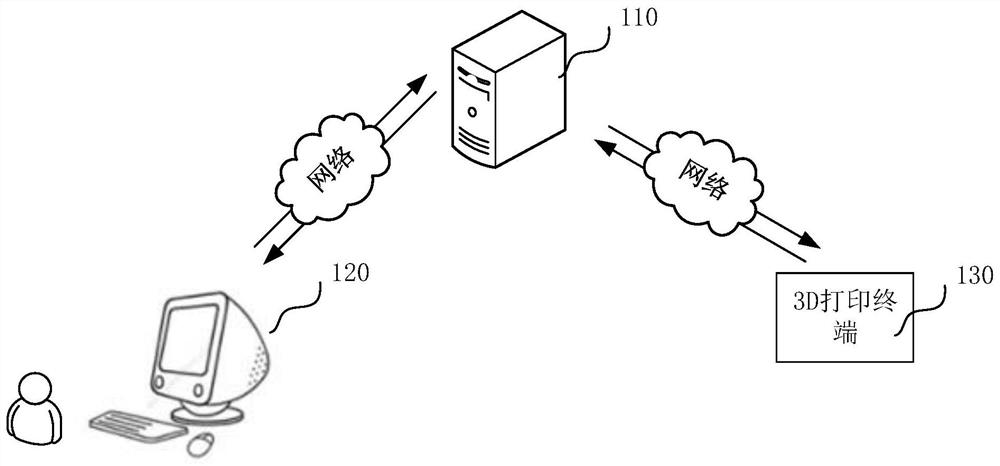

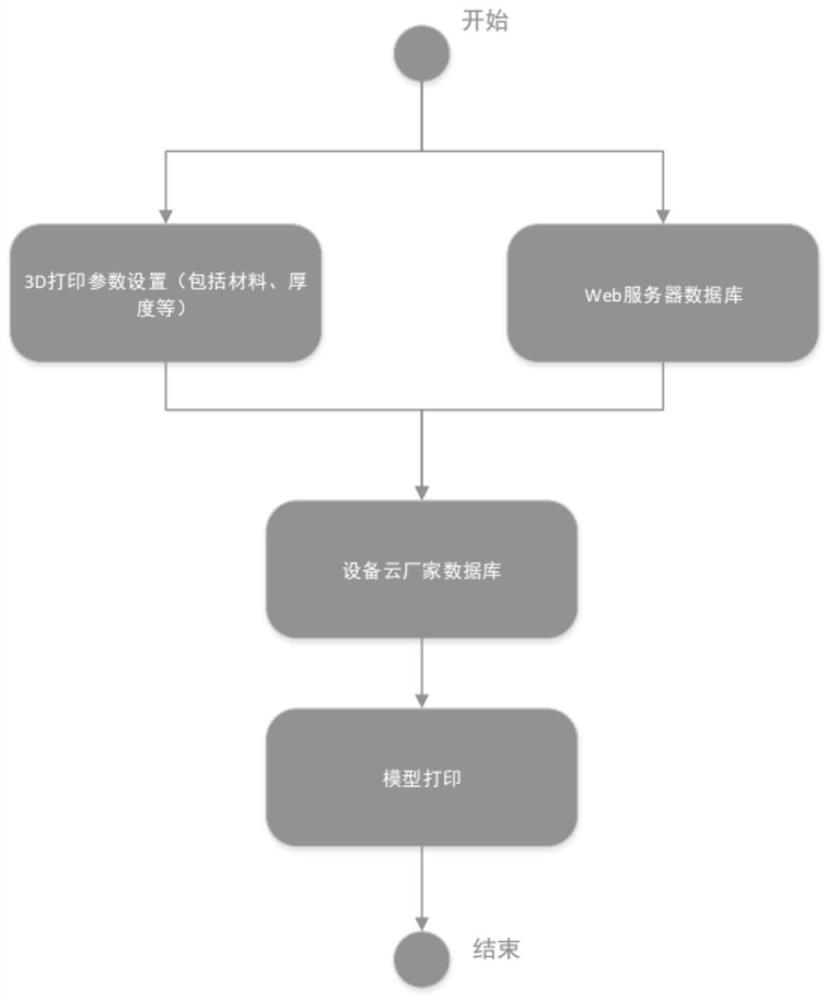

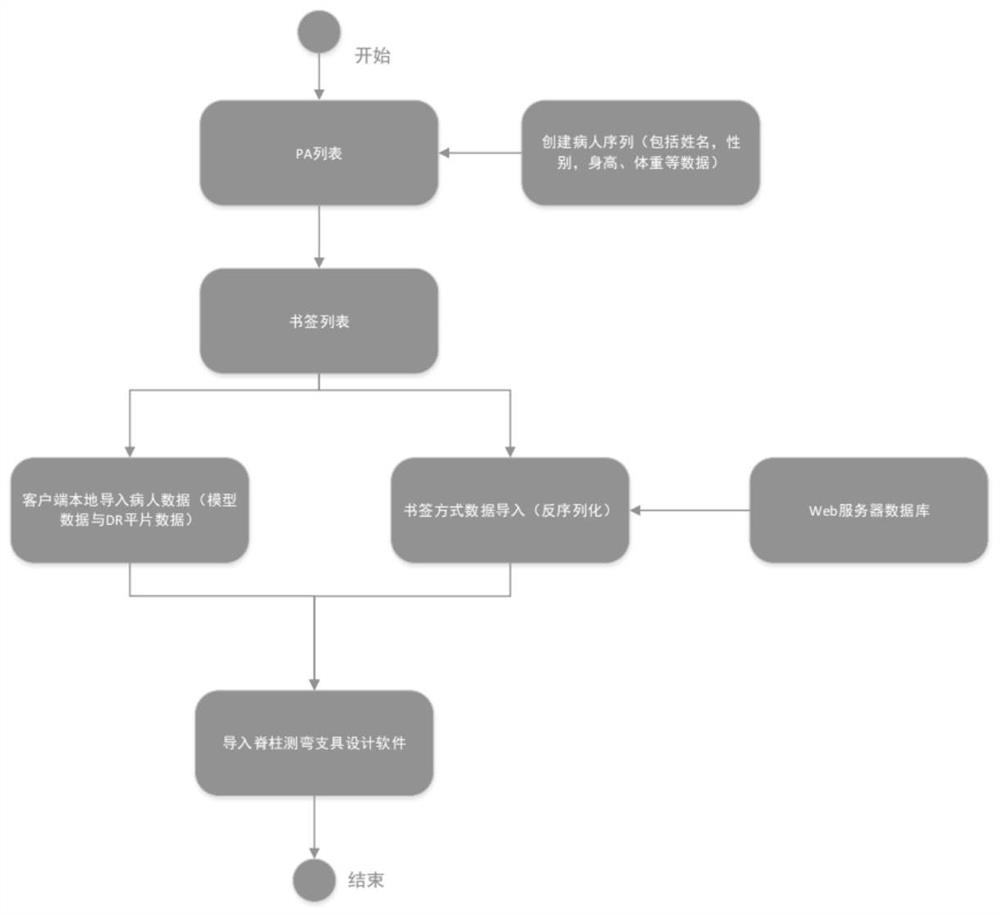

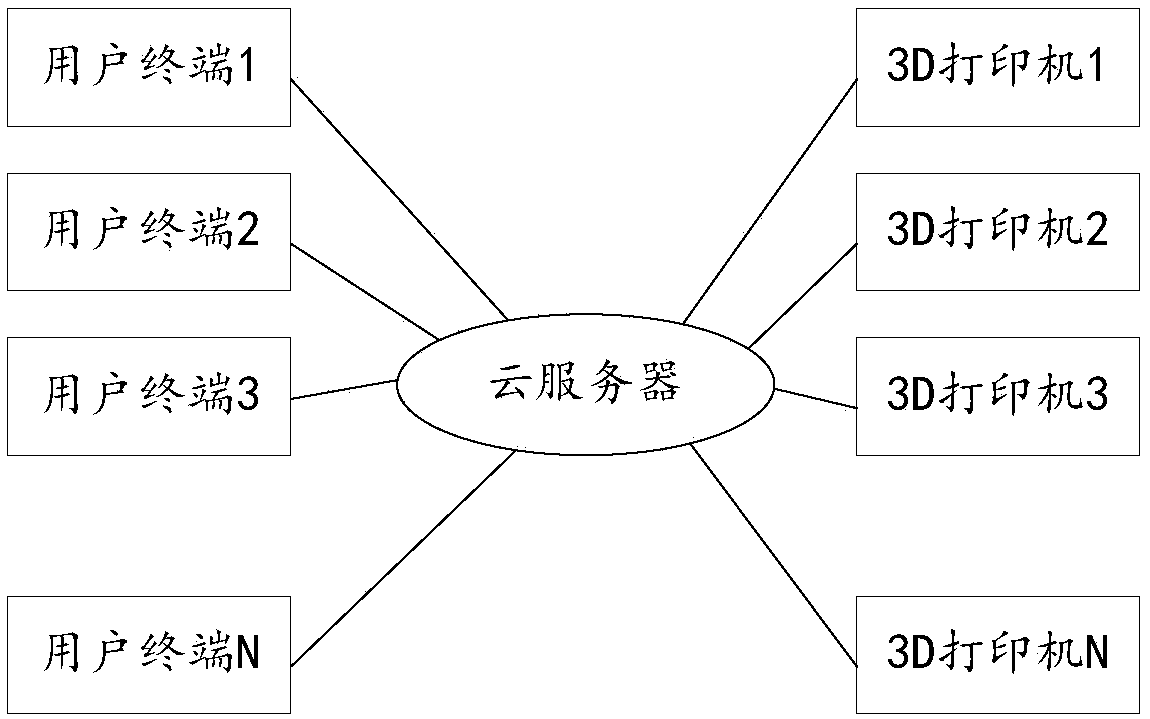

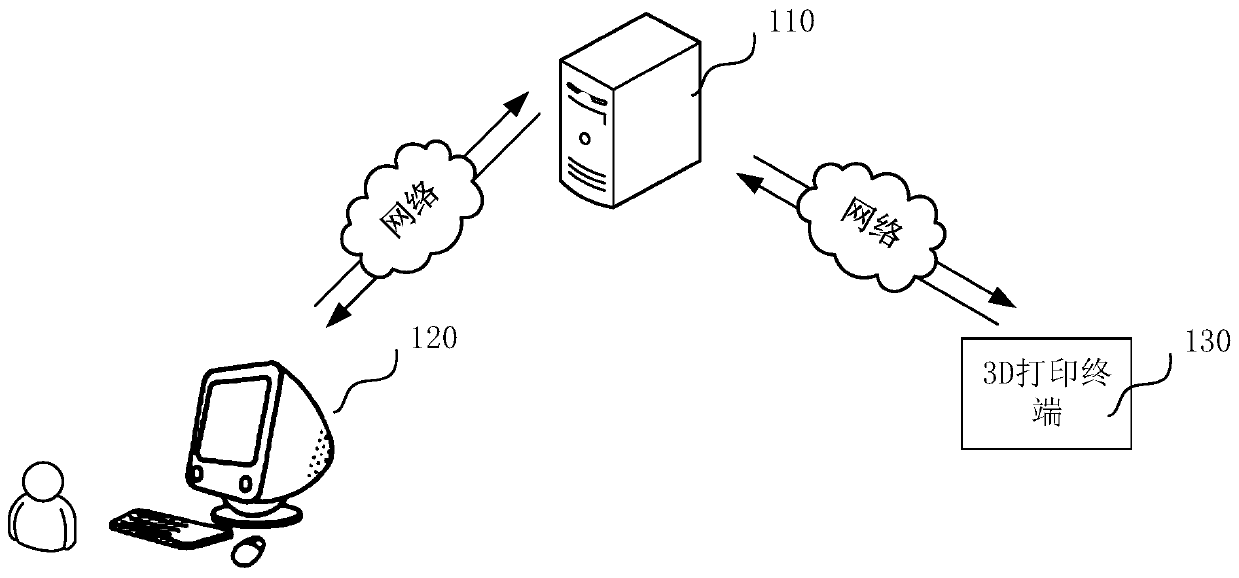

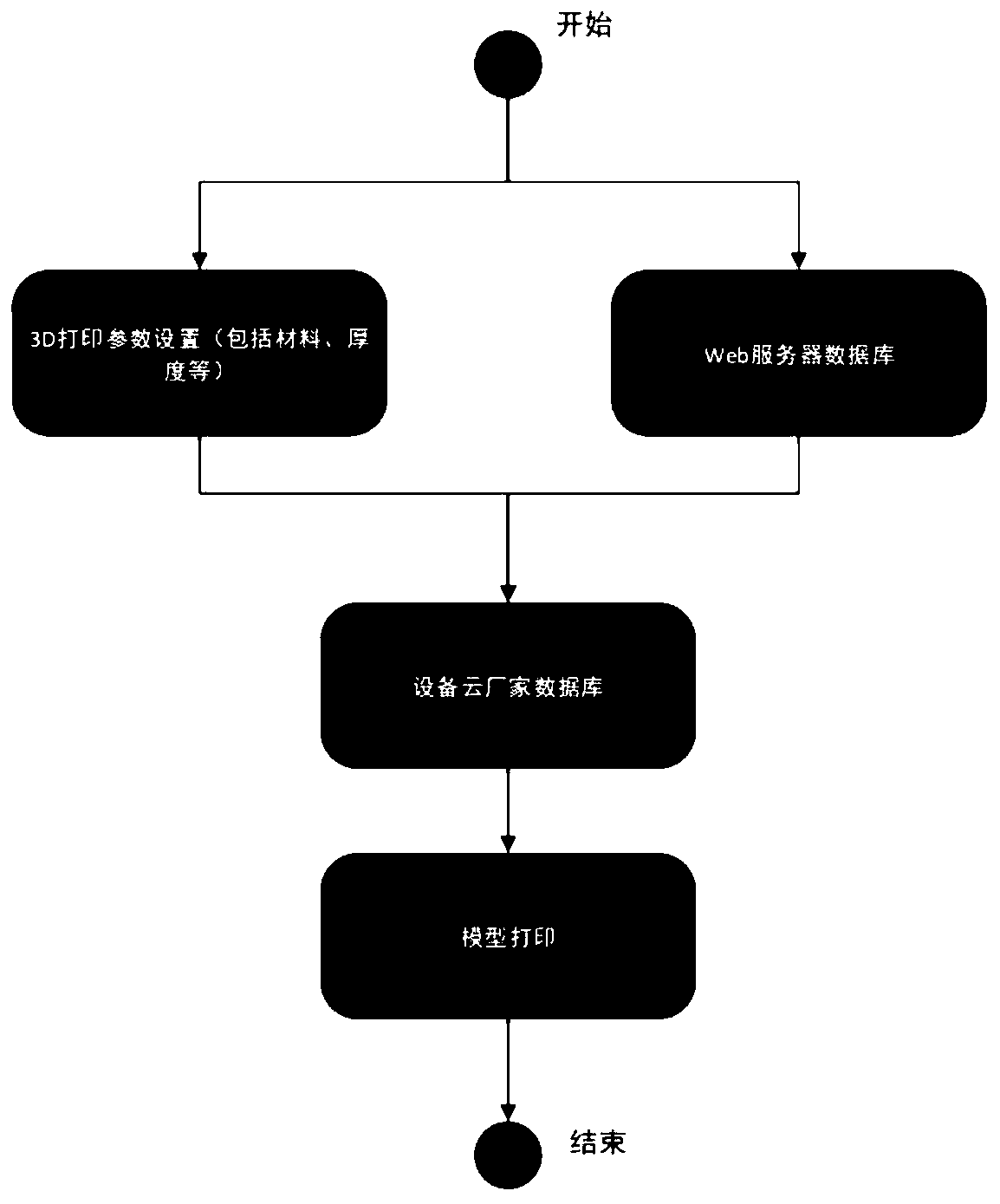

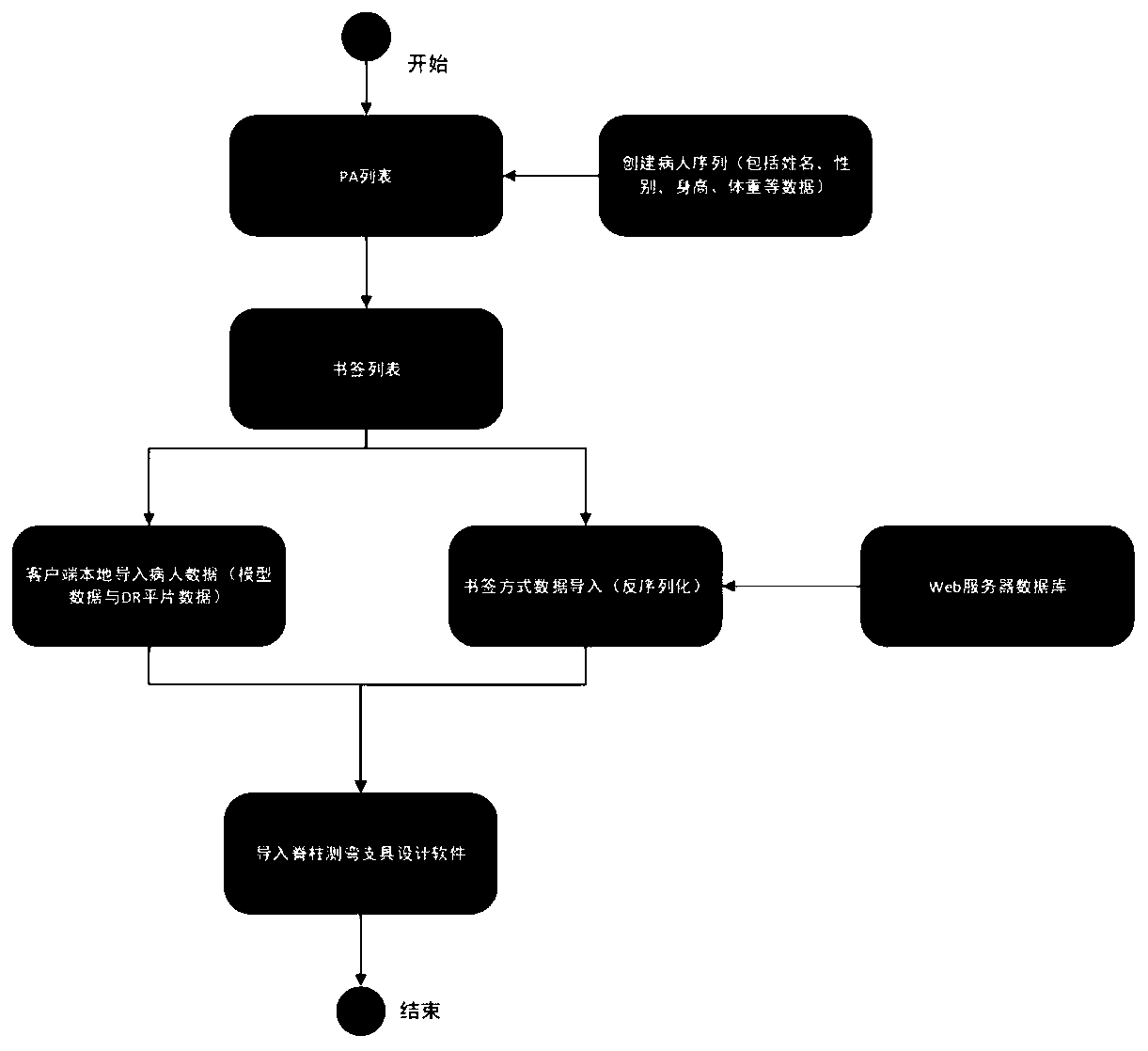

data management system

ActiveCN111324319BImprove design efficiencyShorten the timeAdditive manufacturing apparatusManufacturing data aquisition/processingWorkloadCloud storage

This application relates to a data management system. The system includes: a cloud storage server, a model design terminal and a cloud printing terminal, the model design terminal and the cloud storage server are connected in communication; the cloud storage server is used to decompose design tasks according to preset decomposition rules into a plurality of sub-design tasks, and distribute the plurality of sub-design tasks to the model design terminal; the model design terminal is used to run a plurality of brace design processes, and adopt the plurality of brace design processes for all The plurality of sub-design tasks are respectively used to generate braces to obtain a plurality of sub-brace models; the cloud storage server is used to receive a plurality of sub-brace models, and use preset synthesis rules to combine the plurality of sub-braces The brace model is combined to obtain the brace model; the cloud printing terminal is used to perform three-dimensional printing according to the brace model. The system lowers the design threshold and reduces the design workload of each designer.

Owner:WUHAN UNITED IMAGING HEALTHCARE CO LTD

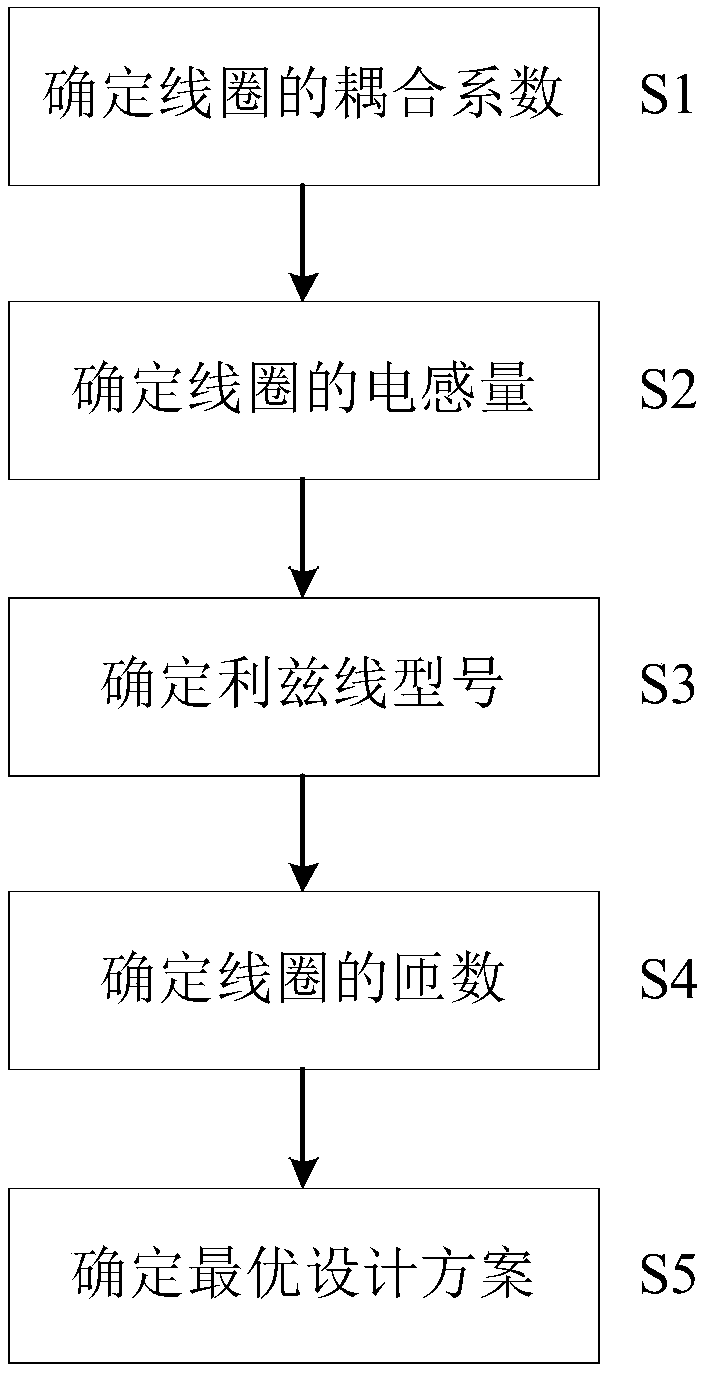

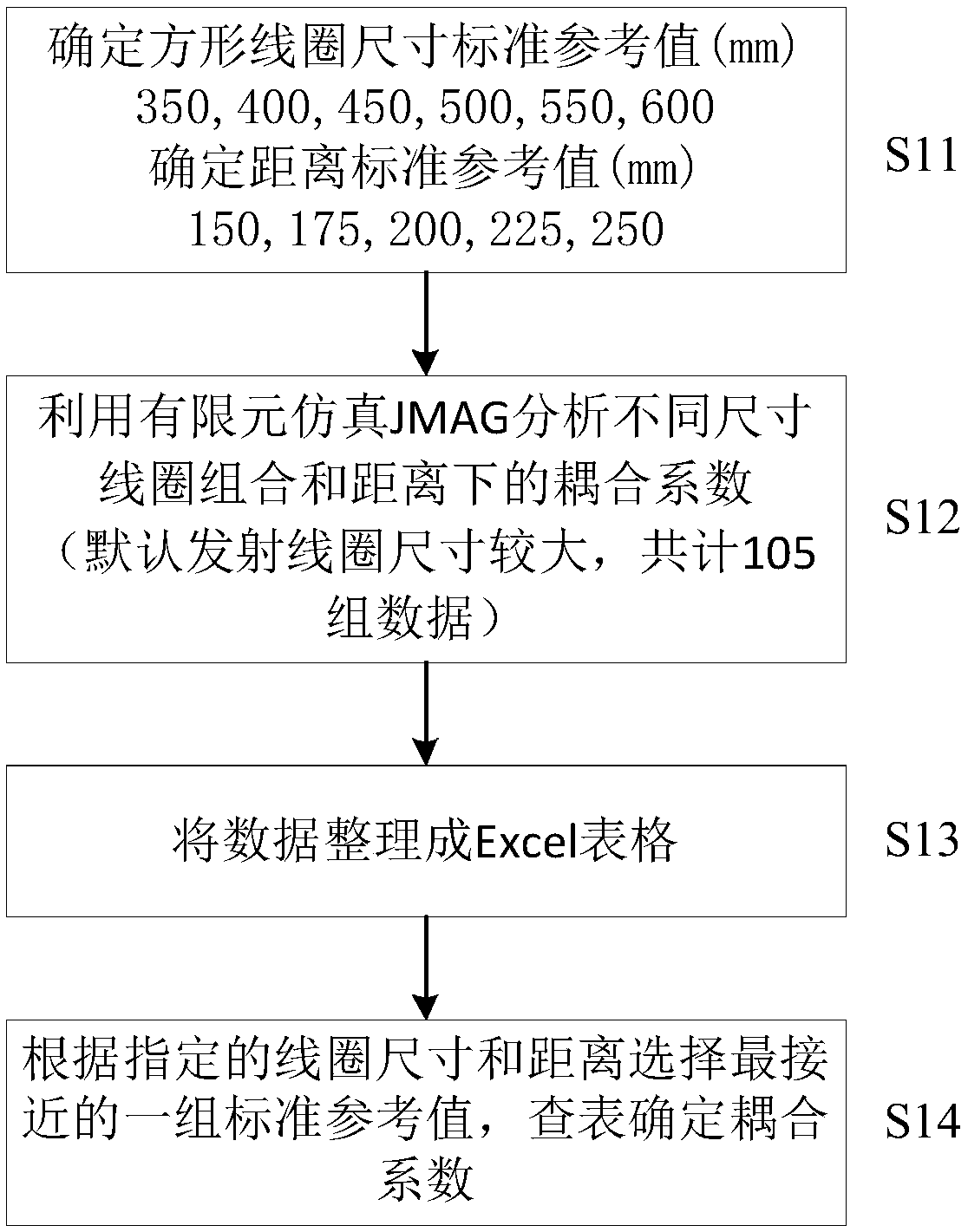

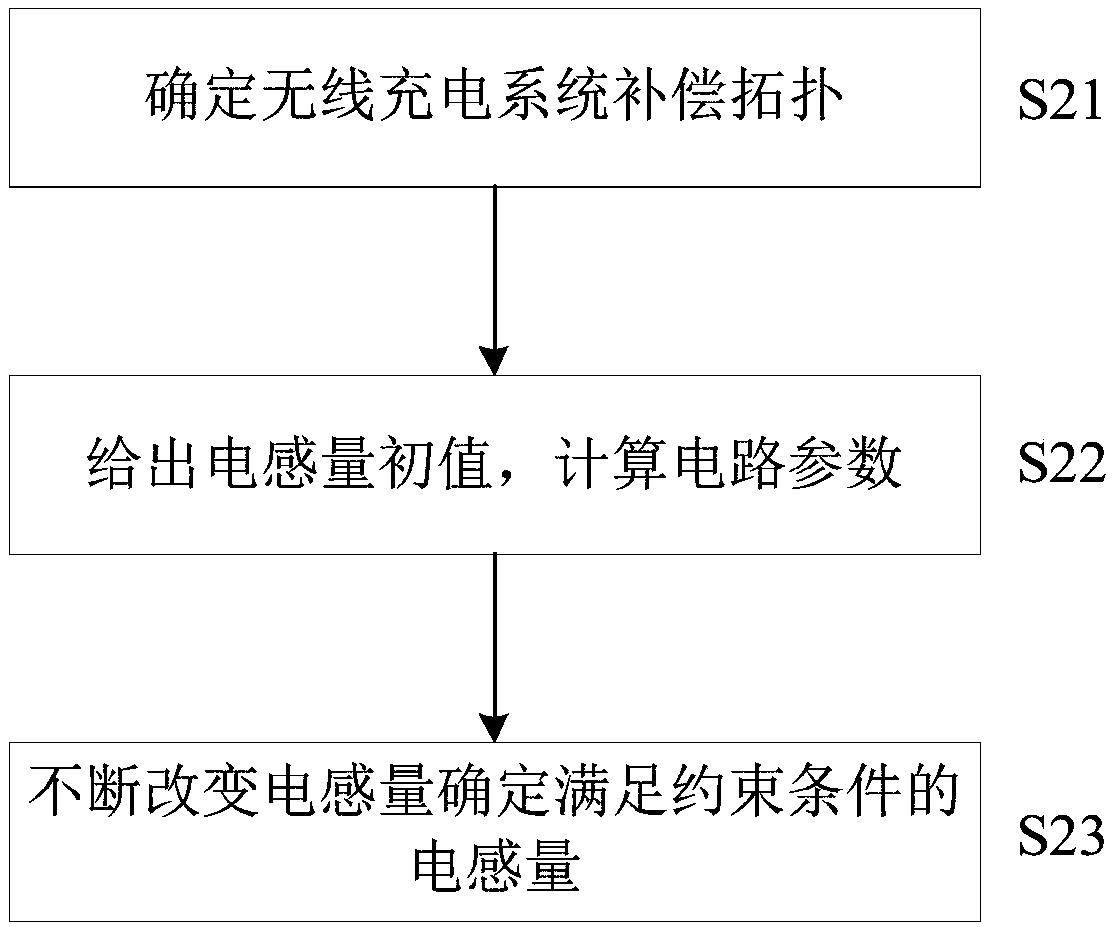

Wireless charging system coupling coil and preparation method thereof

InactiveCN106130191BManufacturing fits realityManufacturing actualBatteries circuit arrangementsTransformersPower flowCoupling

Owner:SHANGHAI JIAOTONG UNIV

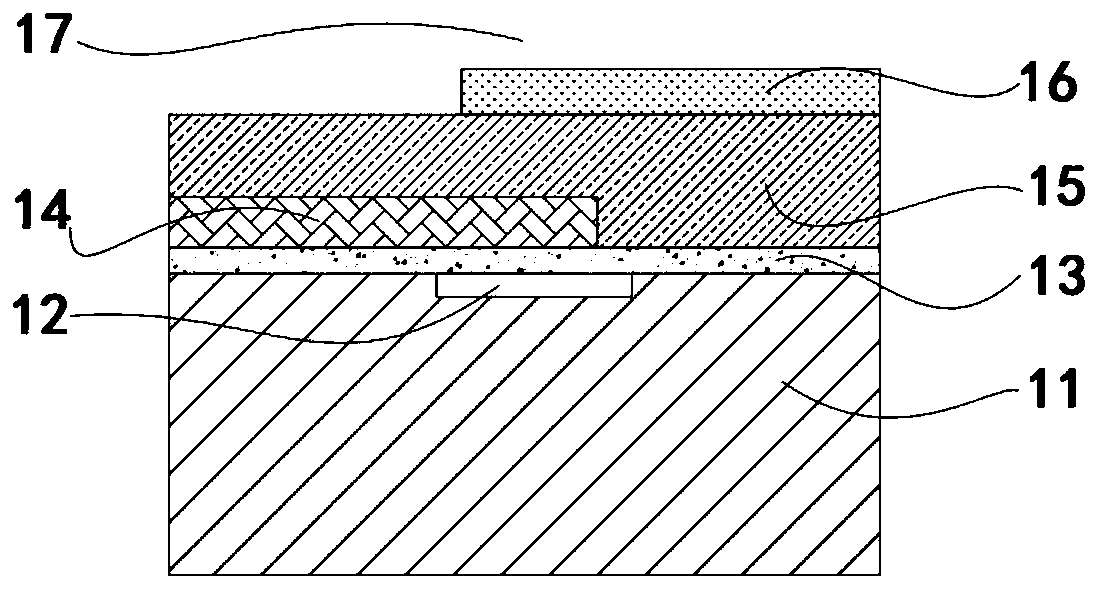

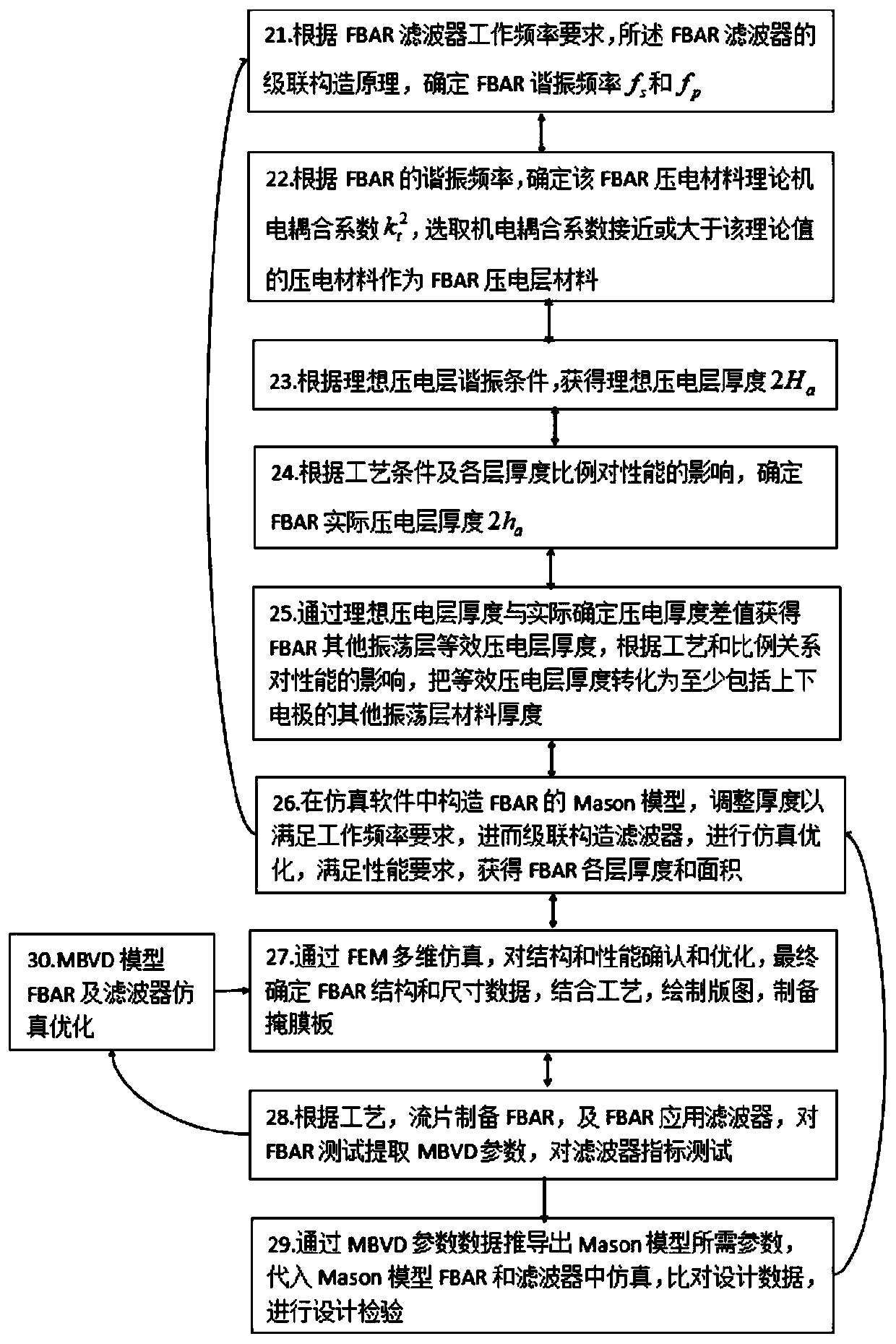

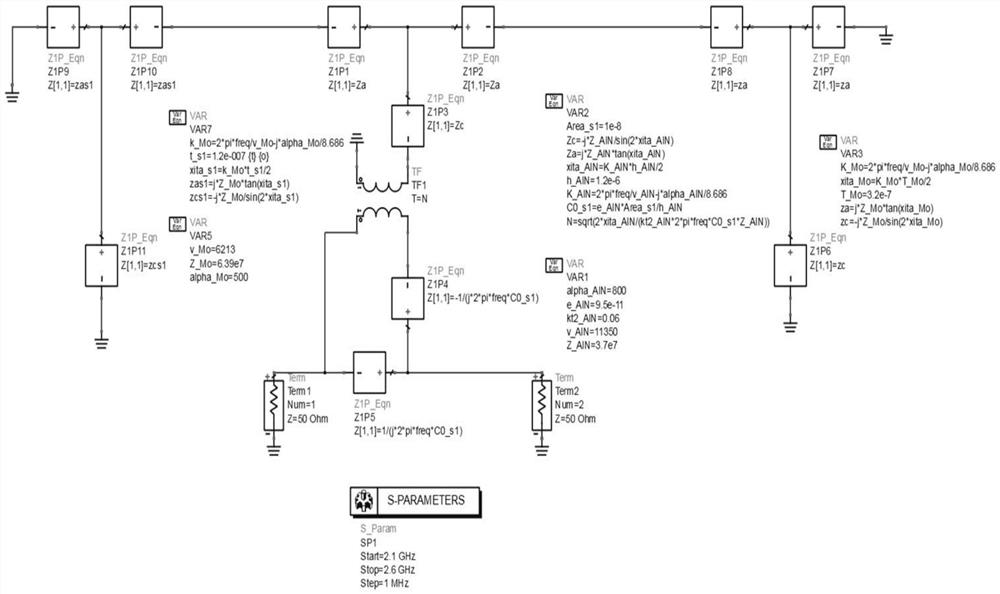

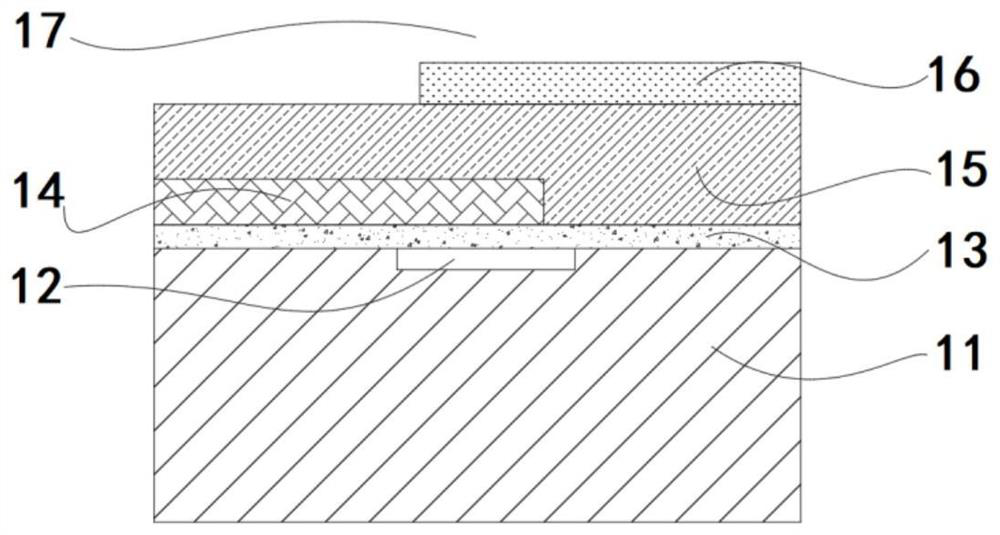

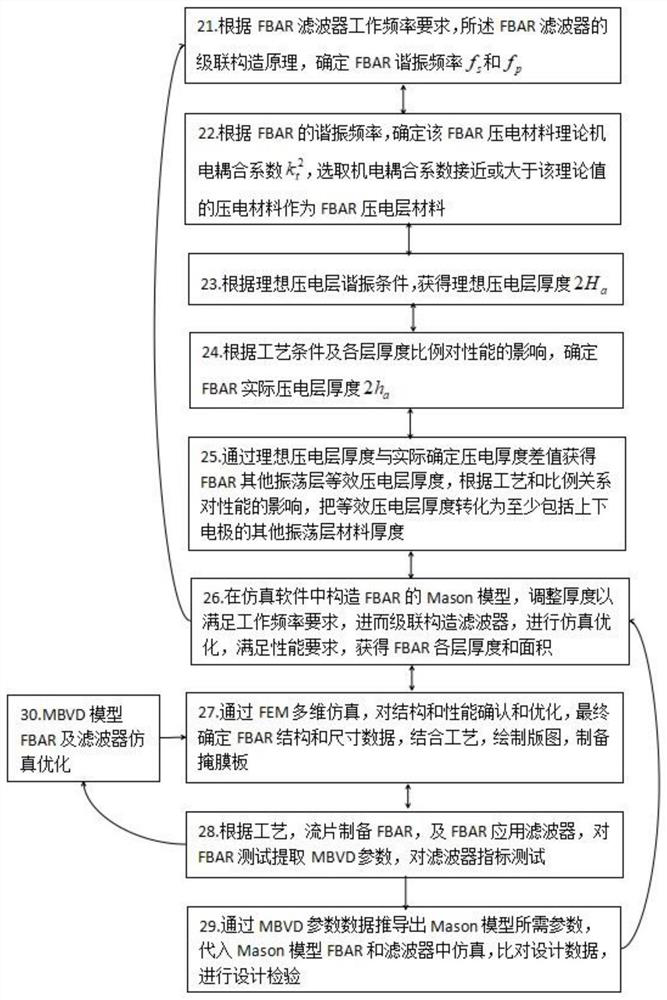

An FBAR design and design inspection method

ActiveCN109766571ALower Design BarriersRapid positioningImpedence networksSpecial data processing applicationsEngineeringInspection method

The invention discloses an FBAR design and design inspection method. The method comprises the following steps of converting an application demand into input of a technical requirement, establishing asimulation model from a key index through a theoretical basis, optimizing, and preparing a prototype sample. The design parameters are deduced from theory to design and then to production, so that thedesign parameters can be compared with the design before preparation, the mutual deduction relationship between the design and the product is established, and the design and design inspection is realized. According to the invention, the FBAR is applied to the design of a filter and a power divider; a set of systematic and efficient method is provided to enable the FBAR to be designed and some problems existing in the design implementation process to be solved, and the process is considered in combination to enable the preparation implementation, so that by designing an inspection part, a recyclable process between the design and the preparation can be further improved.

Owner:广州市艾佛光通科技有限公司

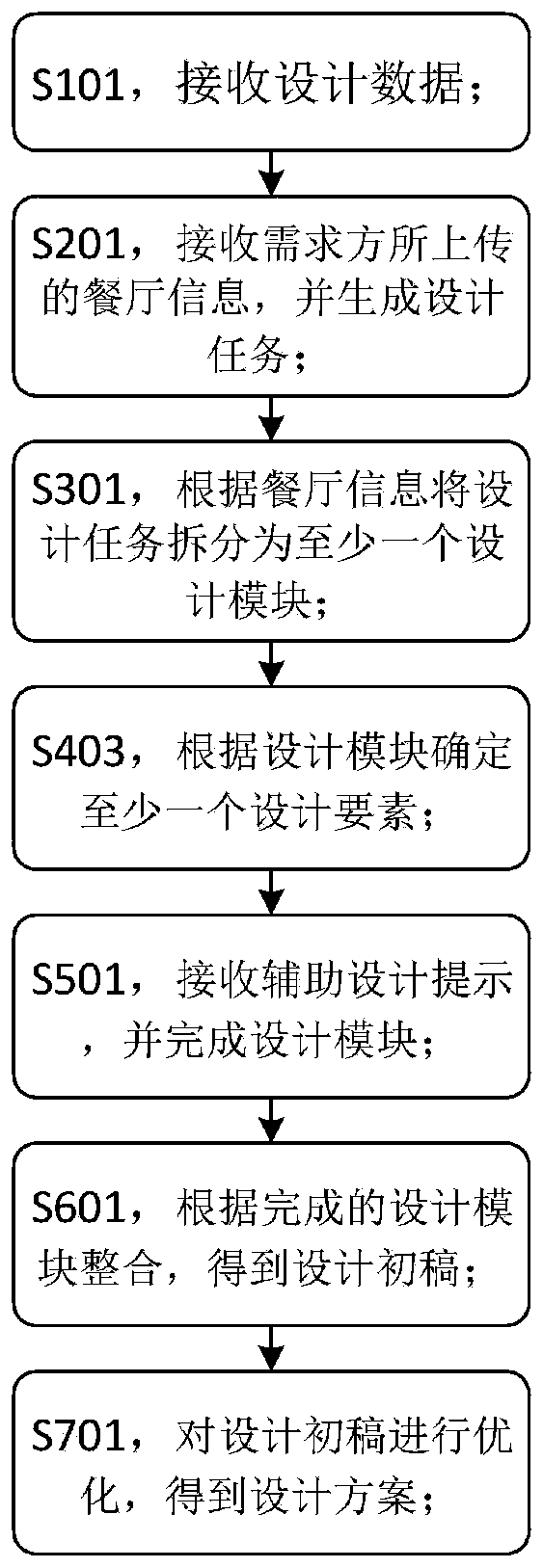

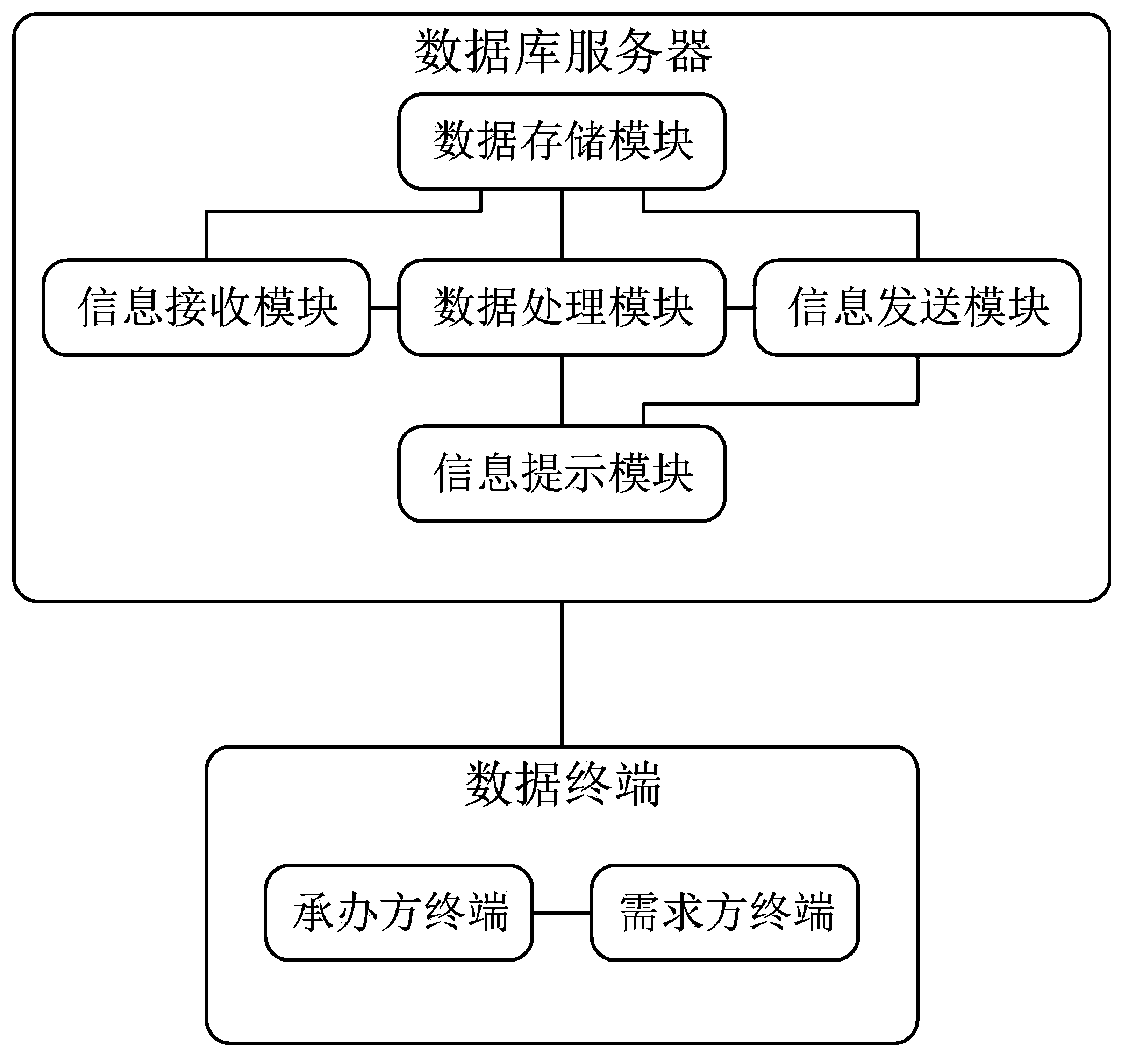

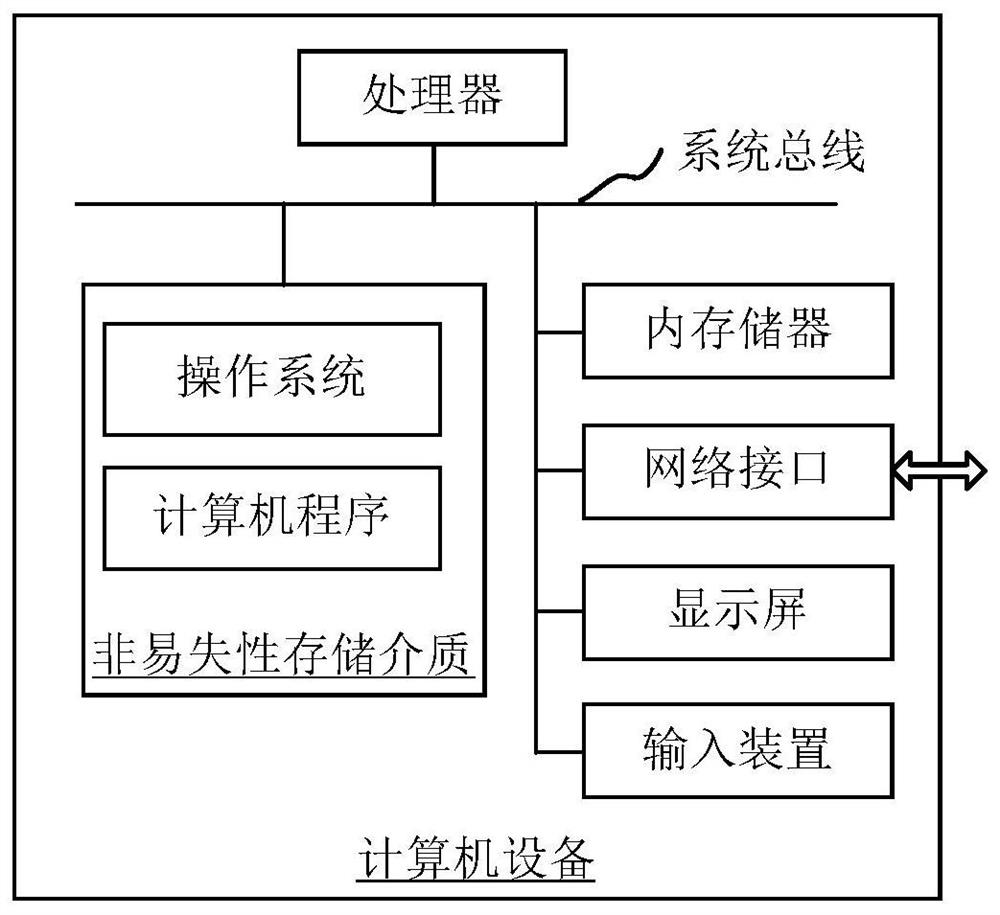

Restaurant aided design method and system

PendingCN110674547AEasy to usePrevent problems that cannot be practically implementedGeometric CADDesign planSoftware engineering

The invention provides a restaurant aided design method. The design method comprises the following steps: receiving design data; receiving restaurant information uploaded by a demand side, and generating a design task; splitting the design task into at least one design module according to the restaurant information; determining at least one design element according to the design module; receivingan auxiliary design prompt, and completing a design module; according to the completed design module integration, obtaining a design first draft; and optimizing the design first draft to obtain a design scheme. According to the invention, a complex design process is simplified, a design task is split into one or more design modules, and then the design module is added and perfected, so that the demand side with low professional degree can fully participate in the design process, the demand side can be fully helped to complete the design scheme, and the problem that the design scheme has irreparable design loopholes and cannot be practically implemented due to the low professional degree of the design of the demand side is prevented.

Owner:北京子然永创装饰设计有限公司

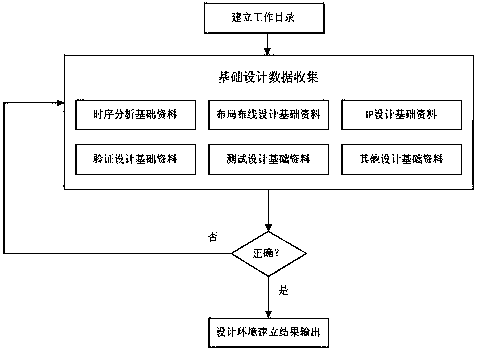

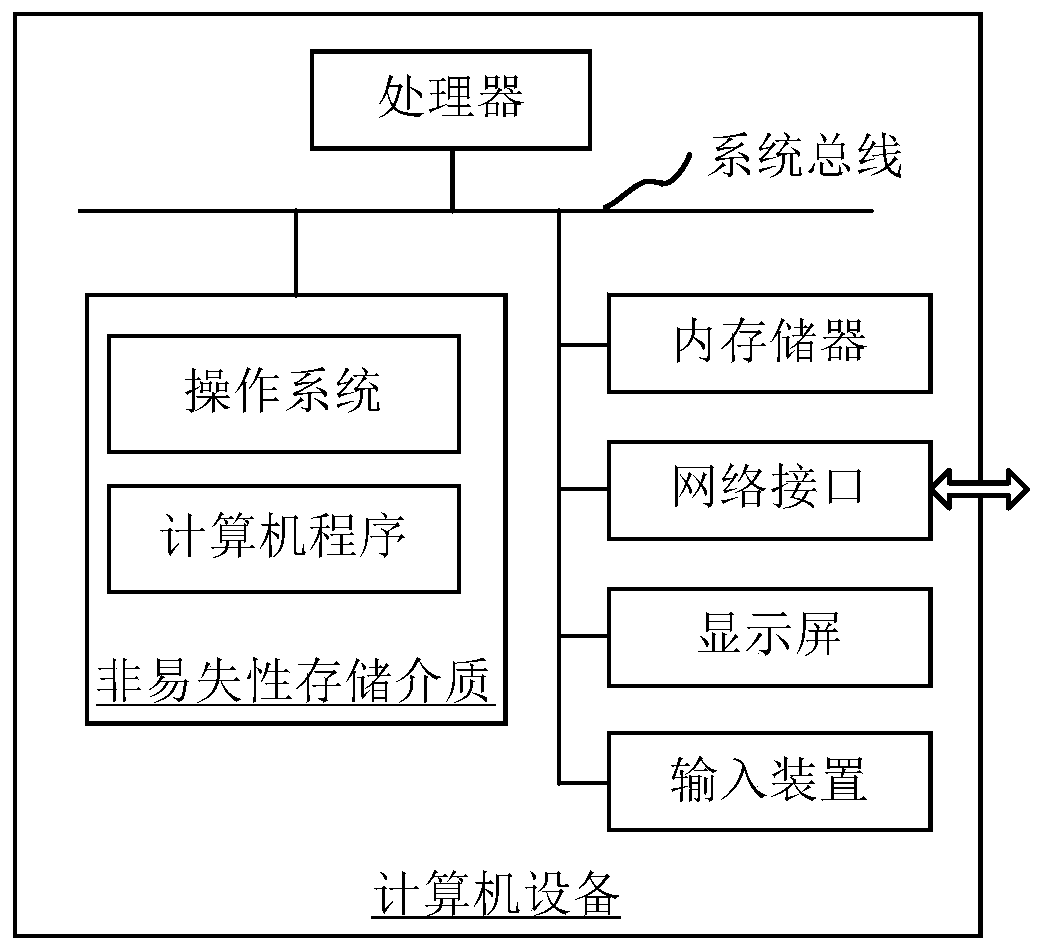

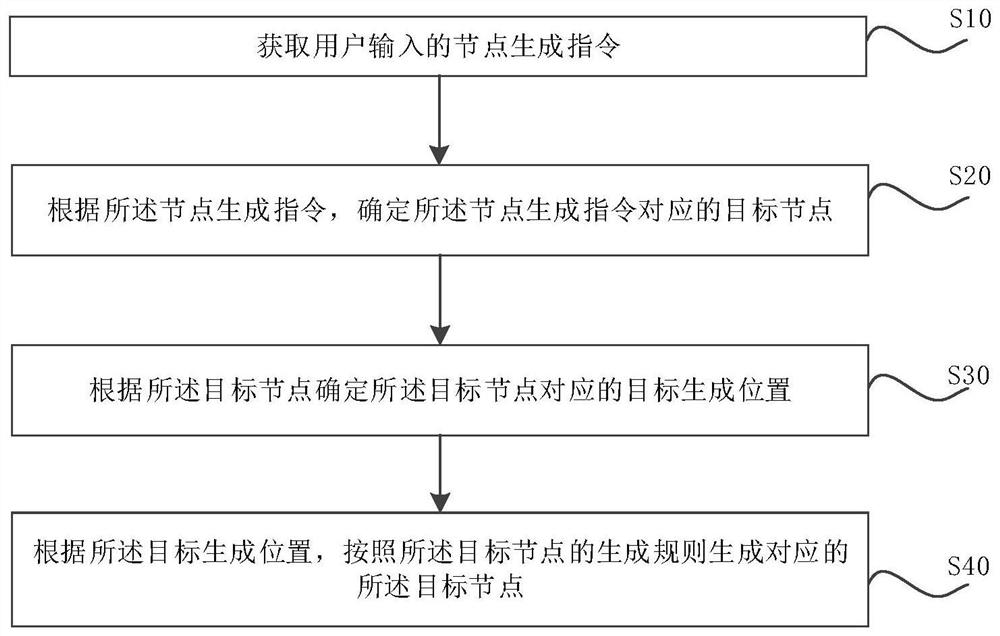

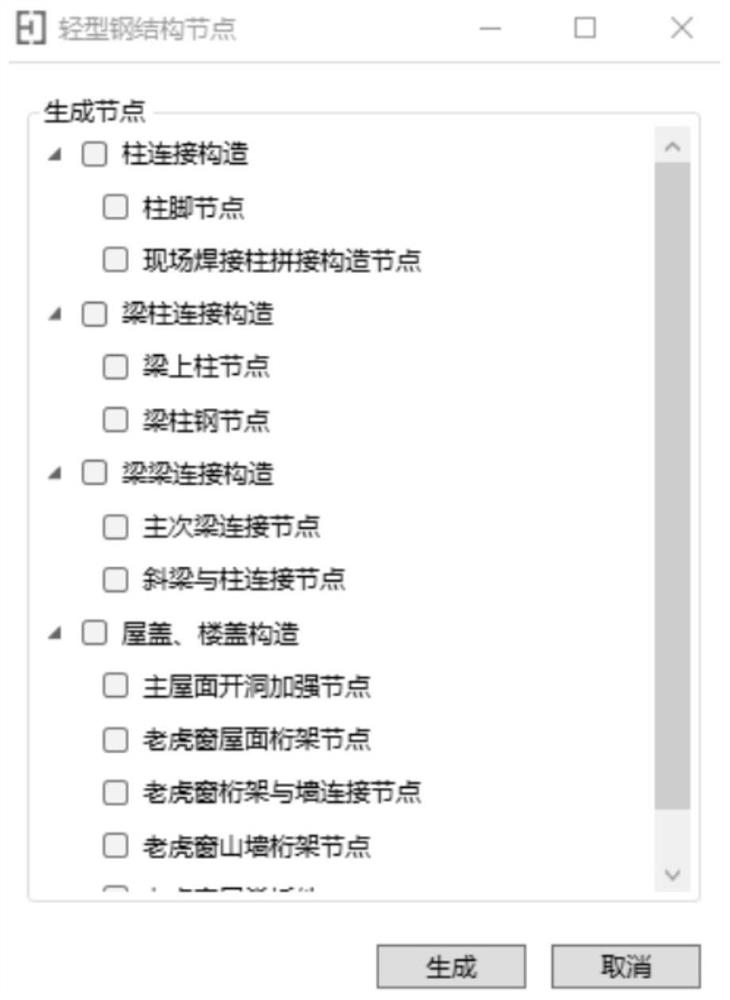

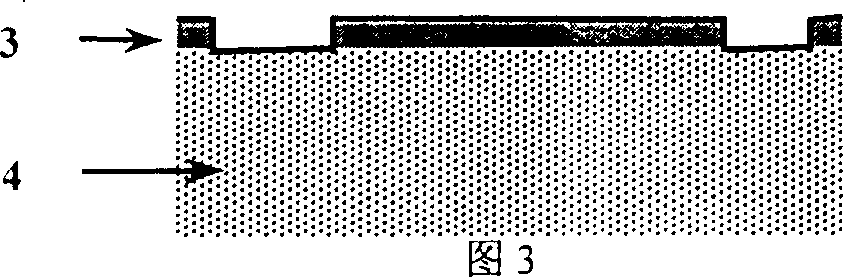

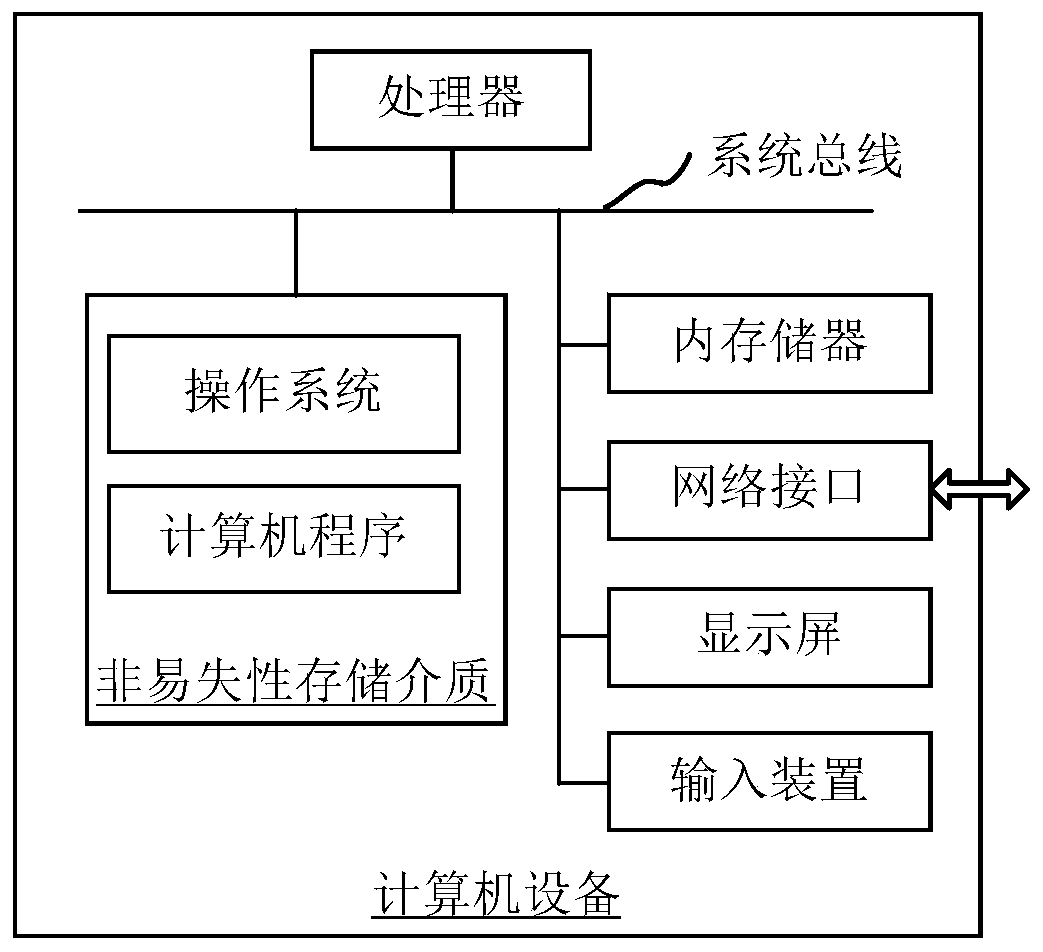

Node generation method and device, computer equipment and storage medium

The invention relates to a node generation method and device, computer equipment and a storage medium. The method comprises the following steps: acquiring a node generation instruction input by a user; determining a target node corresponding to the node generation instruction according to the node generation instruction; determining a target generation position corresponding to the target node according to the target node; and according to the target generation position, generating the corresponding target node according to the generation rule of the target node. By adopting the method, the node generation efficiency and accuracy can be improved.

Owner:久瓴(上海)智能科技有限公司

Detecting method and structure for microstructure binding process

InactiveCN1313813CImprove processing yieldMeet the needs of bond strength testingScanning probe techniquesMaterial strength using steady shearing forcesBonding processSilicon chip

The present invention relates to detection method and detection structure for micro structure bonding process result. The detection method includes first designing silicon structure pattern; preparing micro structure with silicon structure bonded with silicon substrate or glass substrate via bonding technological process, with the silicon structure having at least one end separated from the bonding surface and the bonding area being recorded; pushing the silicon structure on the no-bonding end with micro probe to make the silicon structure deform until the monocrystal silicon chip breaks from the bonding surface and recording the distance between the probe pushed point and the bonding surface, deformation and the breaking process parameters; and calculating the bonding strength based on the recorded data. The present invention completes MEMS device detection in a simple process.

Owner:PEKING UNIV

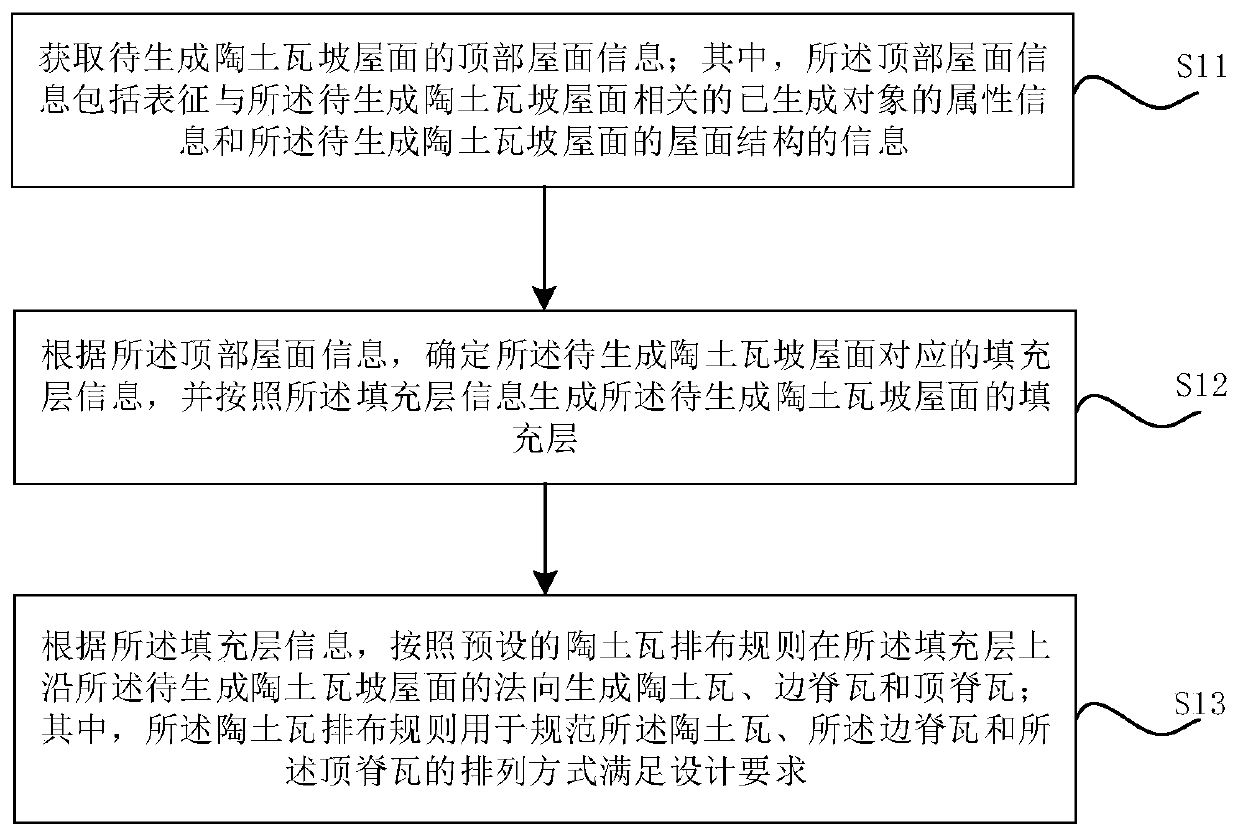

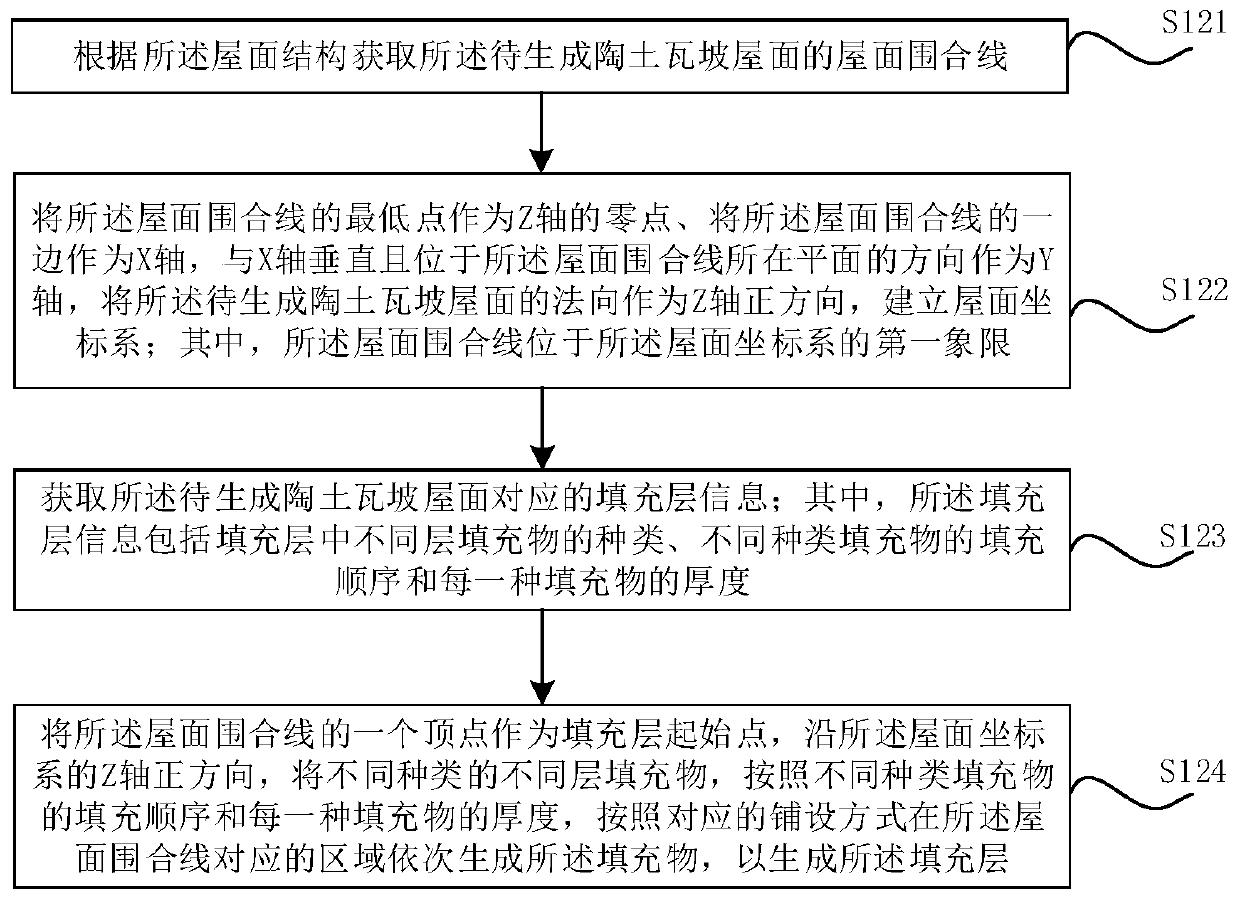

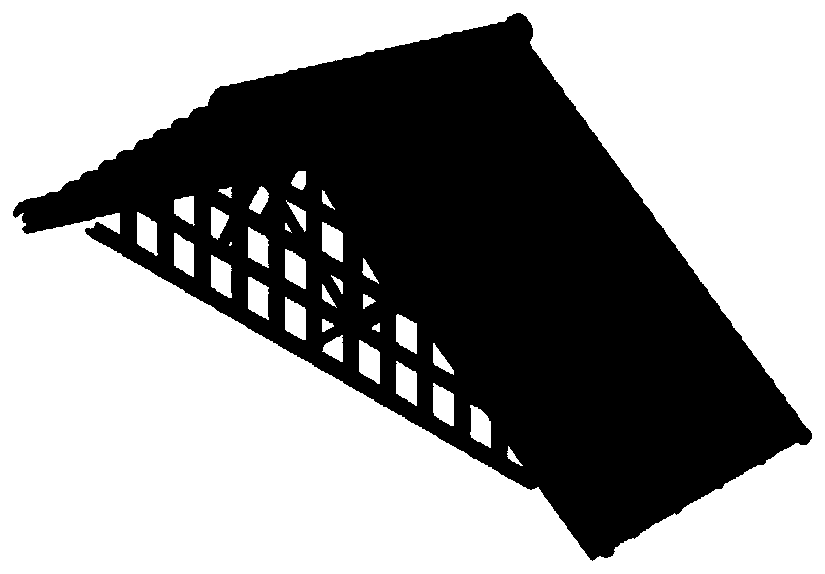

Argil tile sloping roof generation method and device, computer equipment and storage medium

PendingCN111274642AImprove design qualityImprove accuracyGeometric CADComputer equipmentEnvironmental geology

The invention relates to an argil tile sloping roof generation method and device, computer equipment and a storage medium. The method comprises the steps: acquiring that top roof information of a to-be-generated argil tile sloping roof, wherein the top roof information comprises attribute information representing a generated object related to the to-be-generated argil tile sloping roof and information of a roof structure of the to-be-generated argil tile sloping roof; determining filling layer information corresponding to the to-be-generated argil tile sloping roof according to the top roof information, and generating a filling layer of the to-be-generated argil tile sloping roof according to the filling layer information; generating argil tiles, side ridge tiles and top ridge tiles on thefilling layer in the normal direction of the to-be-generated argil tile sloping roof according to the filling layer information and a preset argil tile arrangement rule, wherein the argil tile arrangement rule is used for standardizing the arrangement mode of the argil tiles, the edge ridge tiles and the top ridge tiles to meet the design requirement. By adopting the method, the generation efficiency of the argil tile sloping roof can be improved.

Owner:久瓴(江苏)数字智能科技有限公司

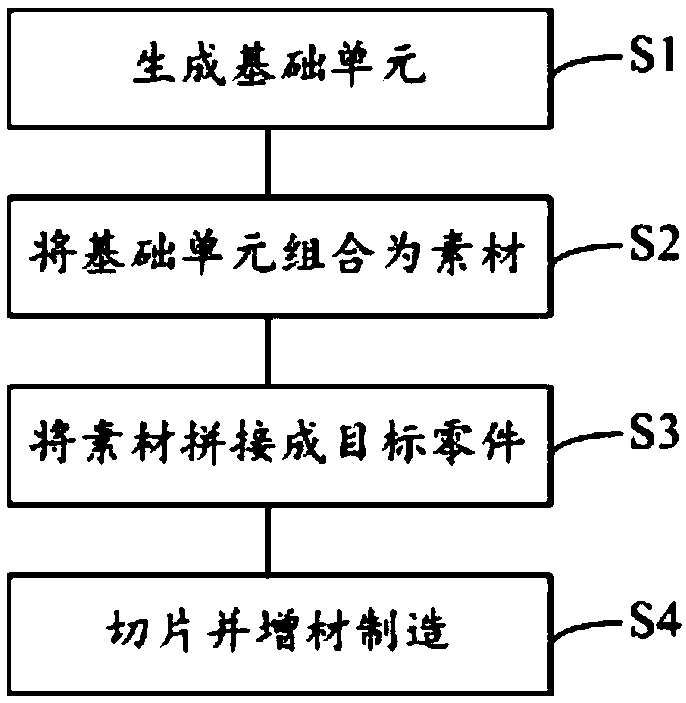

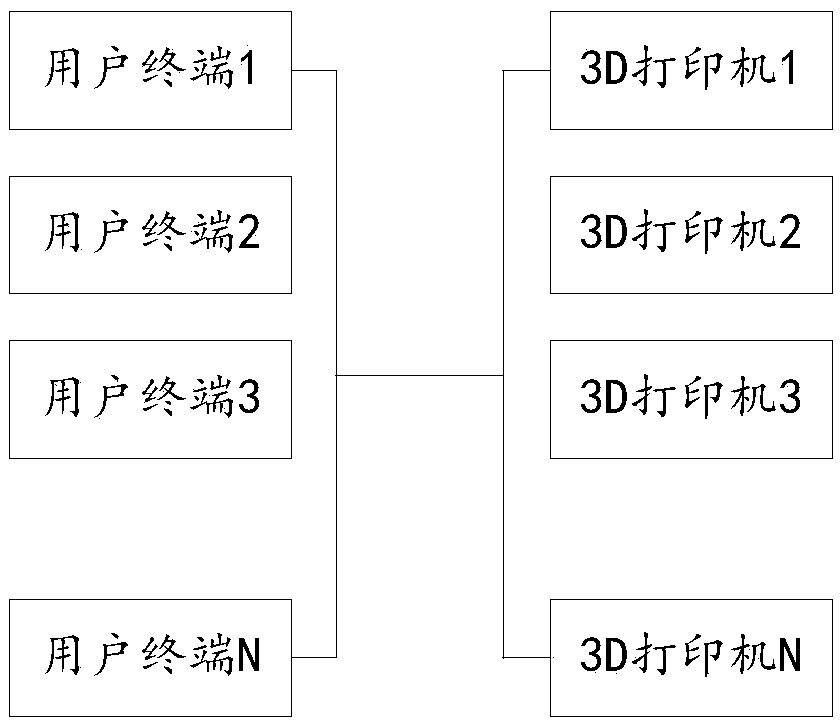

A part manufacturing method and device based on modularization

InactiveCN109445725ALower Design BarriersReduce manufacturing wasteAdditive manufacturing apparatusManufacturing data aquisition/processingCrowdsComputer terminal

The invention belongs to the technical field of part manufacturing and discloses a part manufacturing method based on modularization. The method comprises the following steps of S1 defining a basic unit, making it have the common characteristics of the part, generating a basic unit file and storing the file; 2 customizing and combining the plurality of base units into at least one material havinga basic shape, generating a corresponding material file and storing the material file for standby; S3 selecting a plurality of required materials to be stitched into a complete target part, generatinga target part file and storing the target part file; S4 slicing the target part file to generate instruction code, and implementing material addition manufacturing according to the instruction code to obtain the product of the target part. The invention also discloses a part manufacturing device based on modularization, comprising at least one user terminal and at least one 3D printer. The invention lowers the design threshold so as to improve the creativity of the whole crowd and strengthen the atmosphere of social innovation.

Owner:WUHAN BEIEN THREE DIMENSIONAL TECH CO LTD

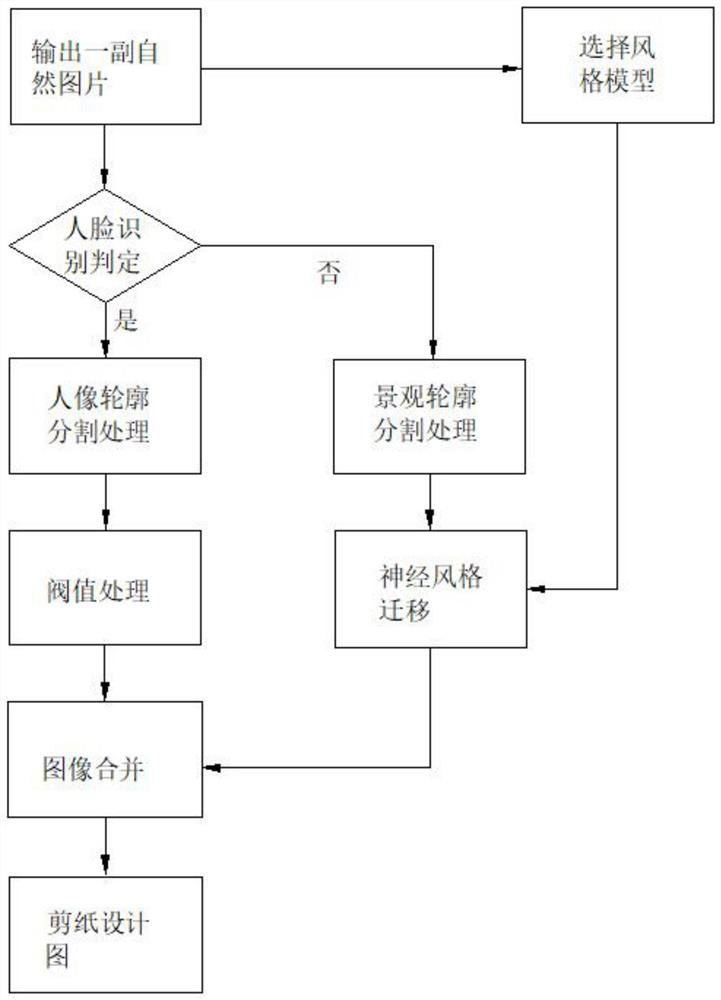

An intelligent design method for color-coated kirigami based on deep learning

InactiveCN110210347BLower Design BarriersReduce design costImage enhancementImage analysisContour segmentationComputer graphics (images)

The invention discloses an intelligent design method for color jacket paper-cutting based on deep learning, comprising the following steps: A: inputting a pair of high-definition natural pictures; B: performing face recognition on the high-definition natural pictures; C: identifying Face contour segmentation processing is performed on the image part of the human face, and landscape contour separation processing is performed on the image part that does not recognize the human face; D: select a style model for the high-definition natural picture in step A, and then use the selected style model The image is used as a style image, and the part of the image that has been processed by the landscape contour is used as the content image for neural style transfer, and the generated image of the same layer is corrected by a norm function to obtain the final image of neural style transfer. The invention adopts the intelligent technology to replace the traditional paper-cut technology, thereby reducing the design threshold and design cost of paper-cut, and greatly shortening the design and production cycle of paper-cut works.

Owner:赵森

Data management system

ActiveCN111324319AImprove design efficiencyShorten the timeAdditive manufacturing apparatusManufacturing data aquisition/processingWorkloadCloud storage

The invention relates to a data management system. The system comprises a cloud storage server, a model design terminal and a cloud printing terminal, wherein the model design terminal is in communication connection with the cloud storage server; the cloud storage server is used for decomposing the design task into a plurality of sub-design tasks according to a preset decomposition rule and distributing the plurality of sub-design tasks to the model design terminal; the model design terminal is used for running a plurality of brace design processes and performing brace generation on the plurality of sub-design tasks by adopting the plurality of brace design processes to obtain a plurality of sub-brace models; the cloud storage server is used for receiving the plurality of sub-brace modelsand combining the plurality of sub-brace models by adopting a preset synthesis rule to obtain a brace model; and the cloud printing terminal is used for carrying out three-dimensional printing according to the brace model. According to the system, the design threshold is reduced, and the design workload of each designer is reduced.

Owner:WUHAN UNITED IMAGING HEALTHCARE CO LTD

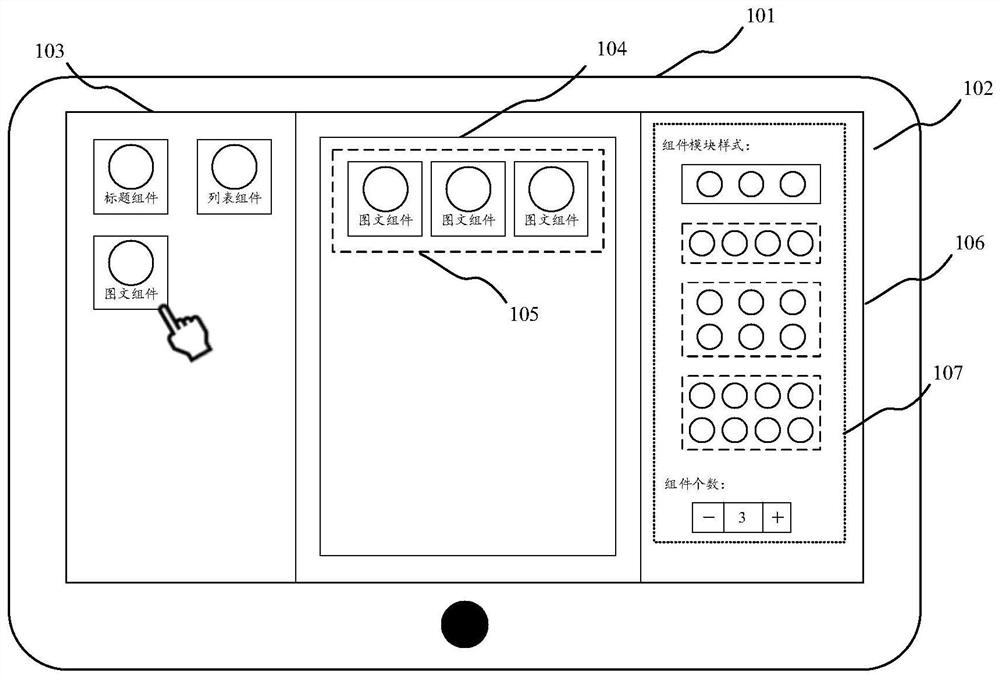

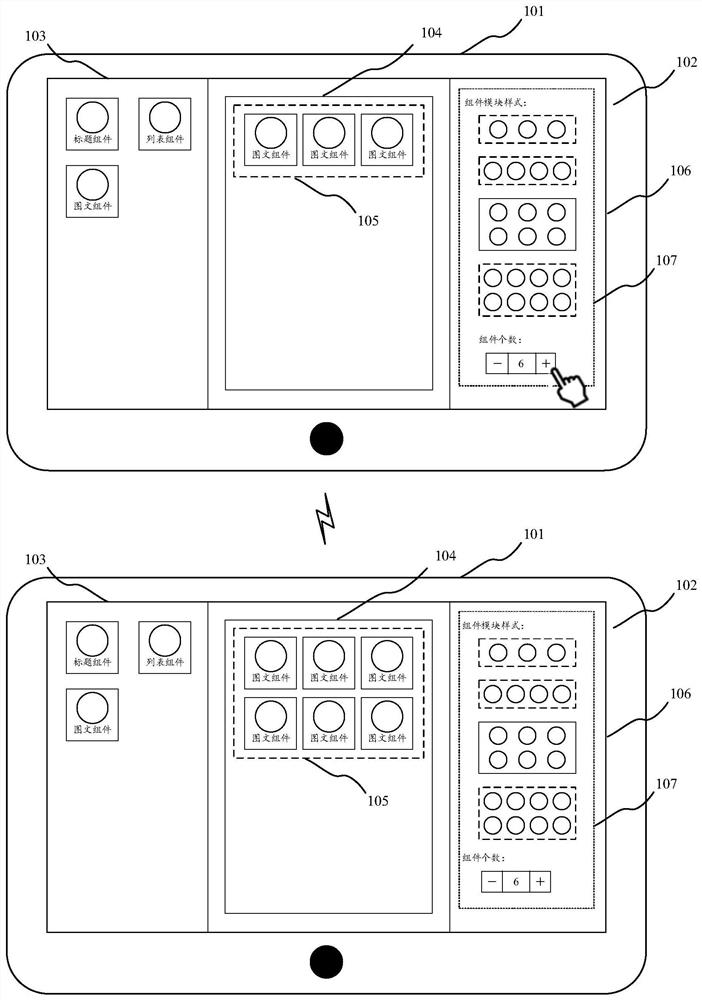

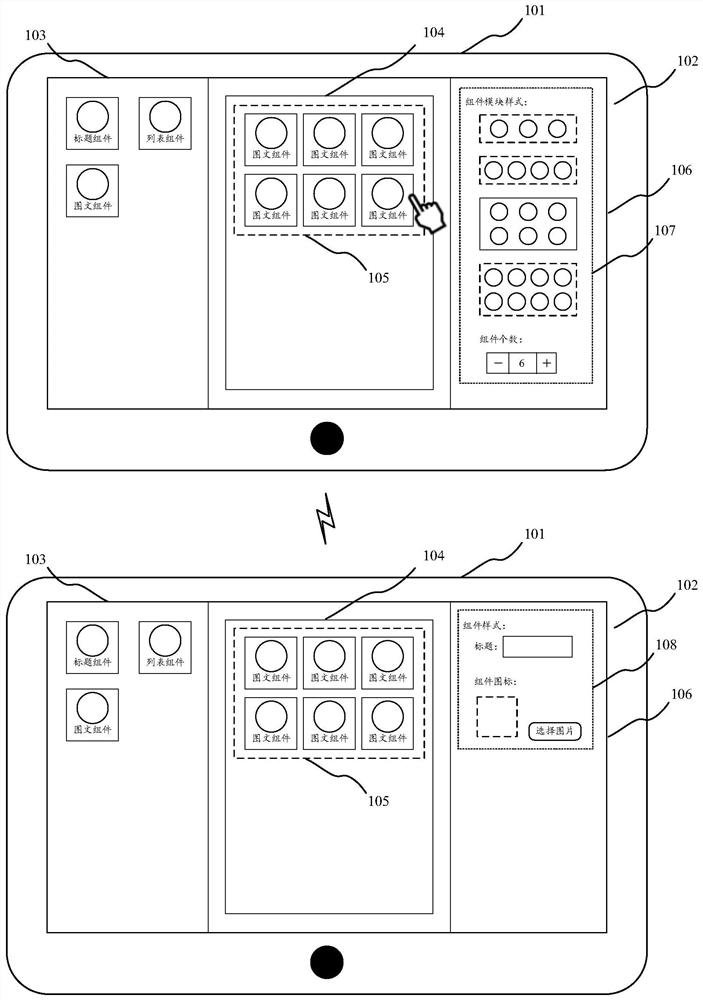

Landing page design interface display method and device, equipment and computer readable medium

PendingCN113110838AImprove design efficiencyLower Design BarriersVisual/graphical programmingInput/output processes for data processingHuman–computer interactionComputer engineering

The embodiment of the invention discloses a landing page design interface display method and device, equipment and a computer readable medium. A specific embodiment of the method comprises the following steps: in response to detection of a selection operation acting on a component selection area in a landing page design interface, displaying a component module in a landing page design area in the landing page design interface, and displaying component module style information in a style editing area in the landing page design interface; in response to the detected editing operation acting on the style information of the component module, adjusting a display style of the component module in the landing page design area; in response to detection of a selection operation acting on any component in the component module, displaying component style information in the style editing area; and in response to detection of an editing operation acting on the component style information, adjusting a display style of the selected component in the component module. According to the implementation mode, the technical threshold of landing page design is greatly reduced, and the landing page setting efficiency is improved.

Owner:BEIJING CHENGSHI WANGLIN INFORMATION TECH CO LTD

fbar design and design inspection method

ActiveCN109766571BLower Design BarriersRapid positioningImpedence networksDesign optimisation/simulationProcess engineeringComputer engineering

Owner:广州市艾佛光通科技有限公司

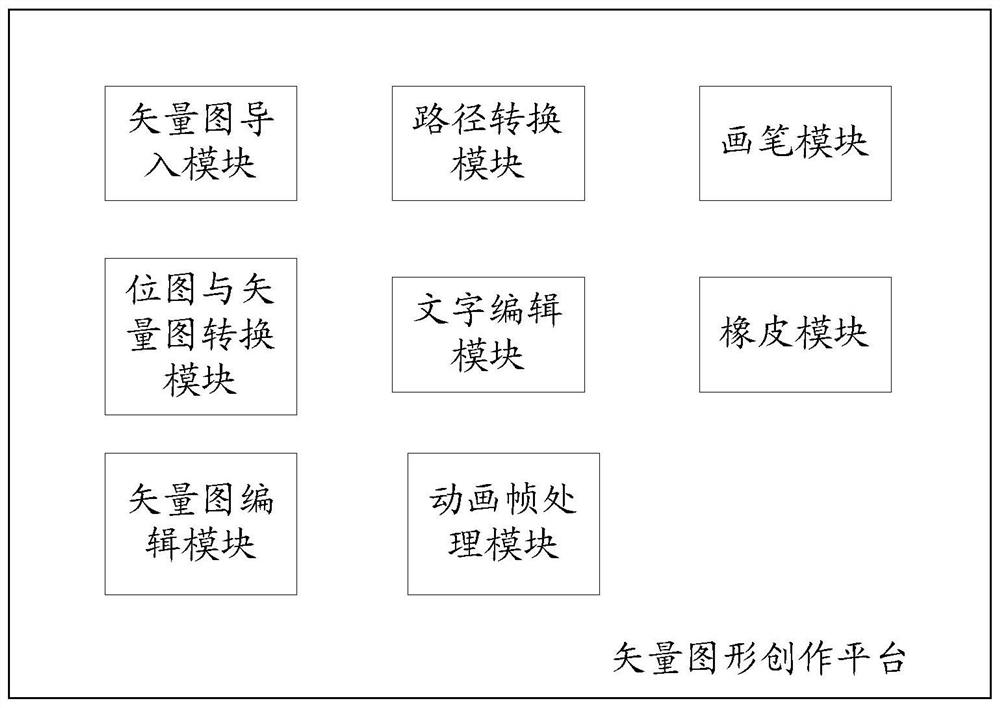

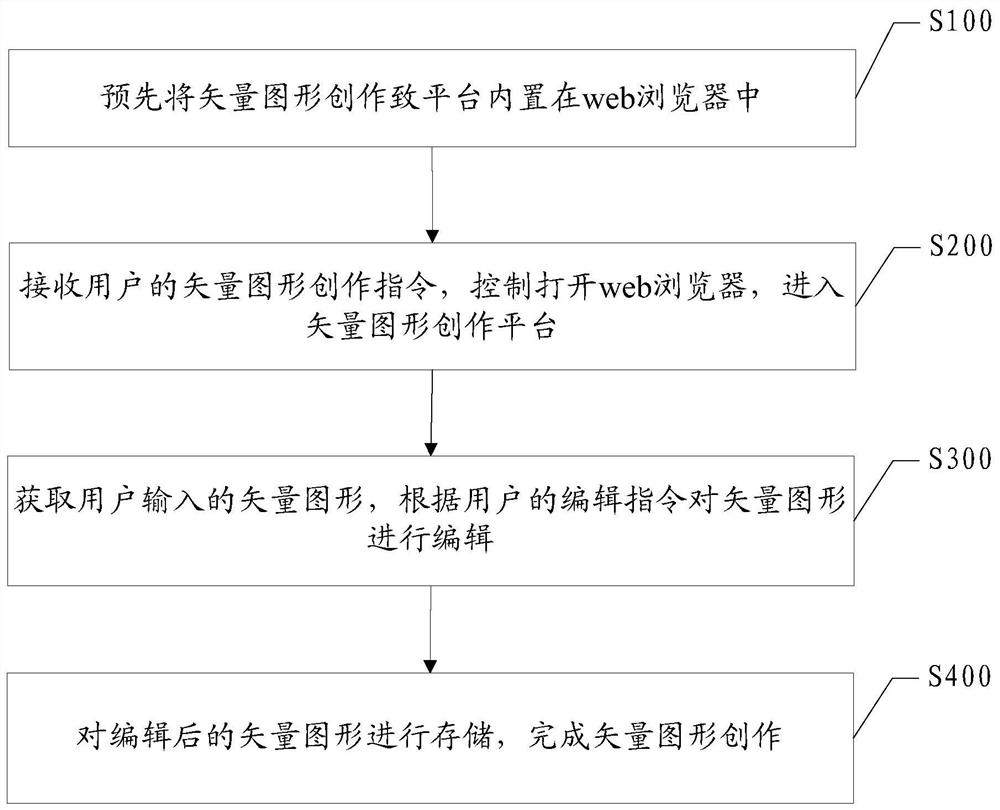

Vector graphic creation platform and creation method based on web browser

PendingCN112001985AReduce creationLower Design BarriersImage enhancementImage analysisWeb browserSoftware engineering

The invention discloses a vector graphic creation platform and creation method based on a web browser. The method comprises the steps of building the vector graphic creation platform in the web browser in advance; receiving a vector graphic creation instruction of a user, controlling to open the web browser, and entering a vector graphic creation platform; obtaining a vector graph input by a user,and editing the vector graph according to an editing instruction of the user; and storing the edited vector graph to finish vector graph creation. According to the embodiment of the invention, basedon a browser environment, a WEB front-end technology stack is used for development, and a tool capable of carrying out vector graphic creation and editing under various environmental conditions such as a PC end and a mobile end is realized. The threshold of vector diagram creation and design of common users is greatly reduced, and the method is efficient and convenient.

Owner:SHENZHEN DIANMAO TECH CO LTD

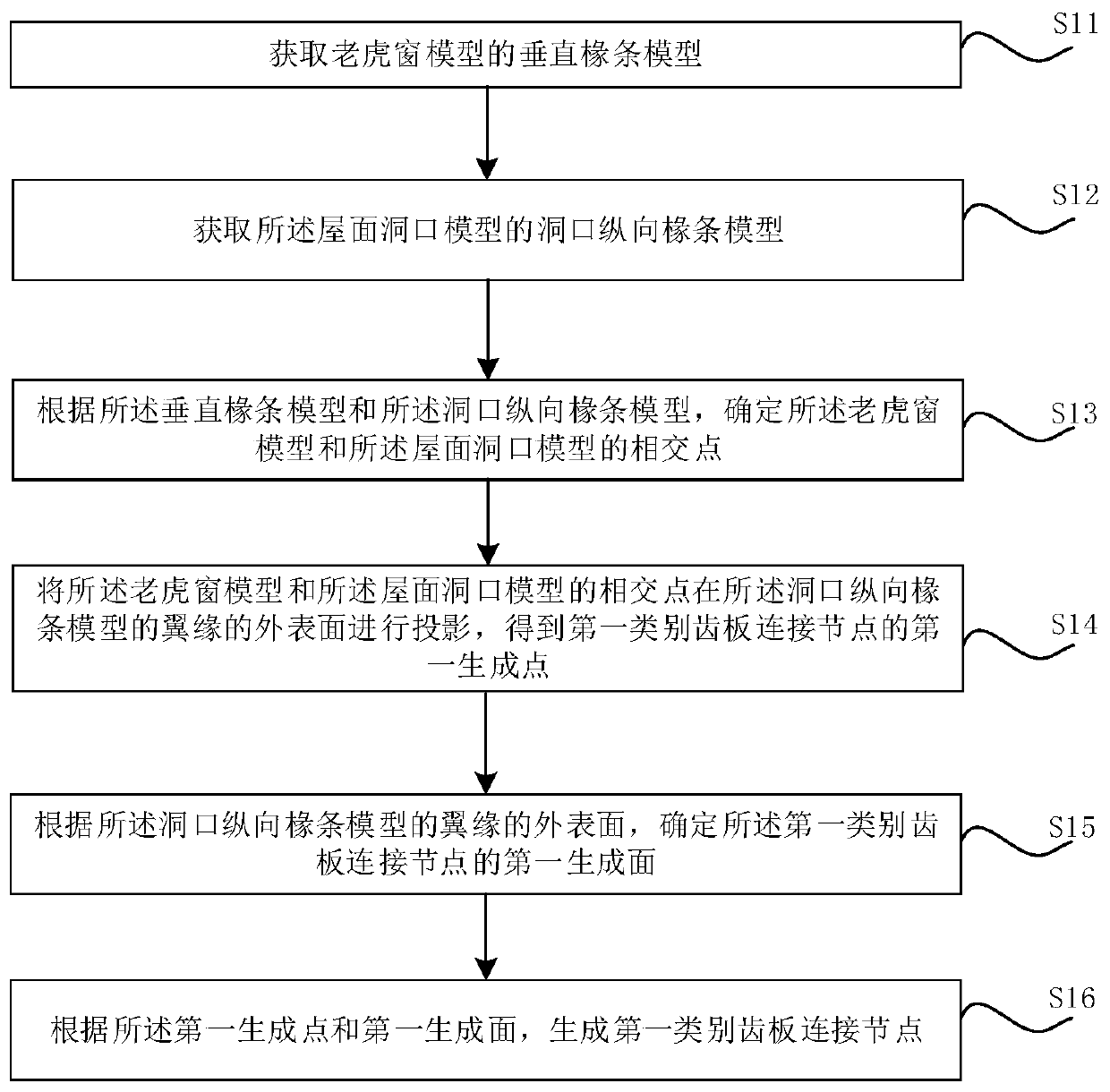

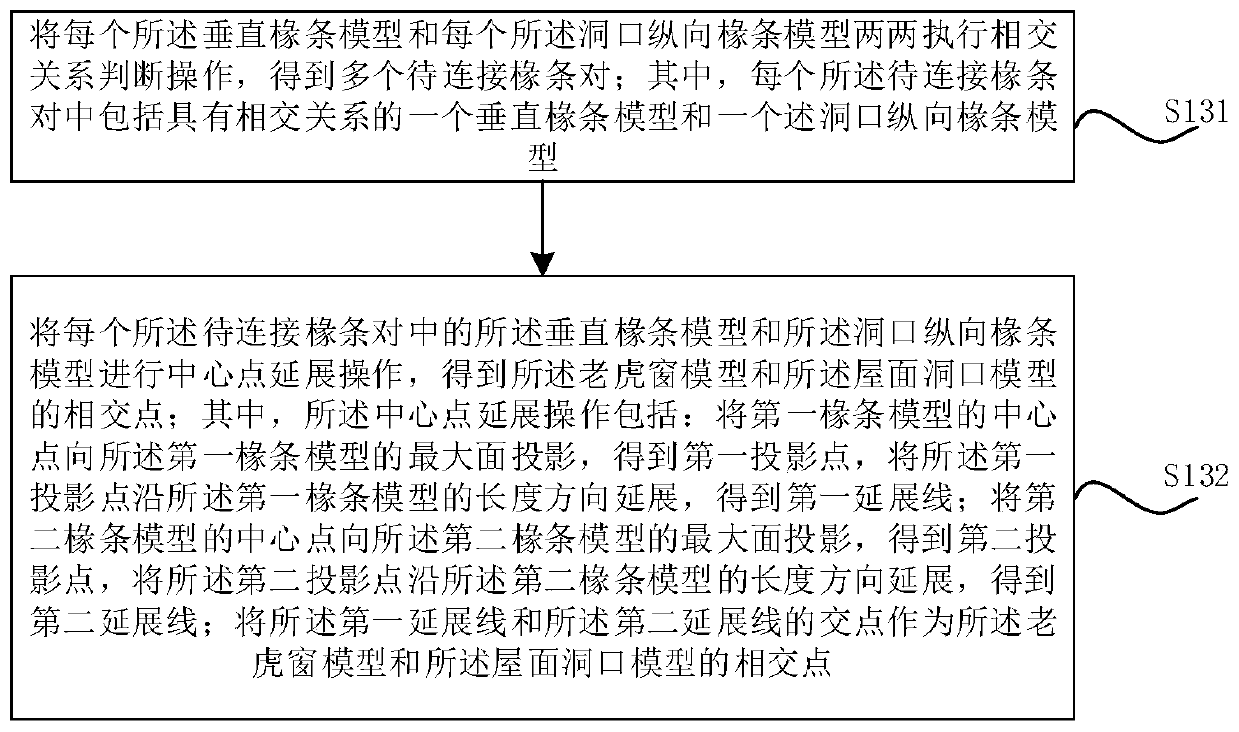

Connecting joint placement method of tiger window model and roof opening model and product

PendingCN110704899AAvoid inefficiencyIncrease the difficultyGeometric CADDesign optimisation/simulationRafterStructural engineering

The invention relates to a connecting joint placement method of a tiger window model and a roof opening model and a product. The method comprises the following steps: acquiring a vertical rafter modelof a tiger window model; obtaining a hole longitudinal rafter model of the roof hole model; determining an intersection point of the tiger window model and the roof opening model according to the vertical rafter model and the opening longitudinal rafter model; projecting an intersection point of the tiger window model and the roof opening model on the outer surface of a flange of the opening longitudinal rafter model to obtain a first generation point of a first type of toothed plate connection node; according to the outer surface of the flange of the hole longitudinal rafter model, determining a first generation surface of the first type of toothed plate connection node; and according to the first generation point and the first generation surface, generating a first type of toothed plateconnection node. By adopting the method, the placement efficiency of the connection nodes can be improved.

Owner:久瓴(江苏)数字智能科技有限公司

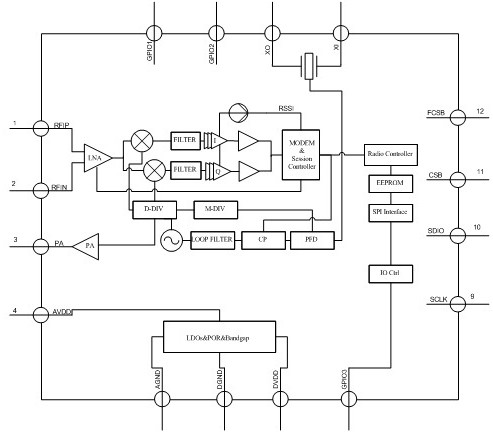

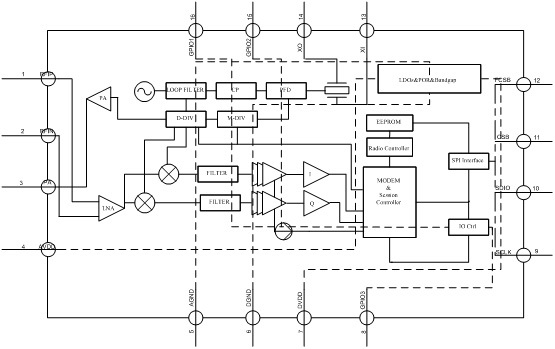

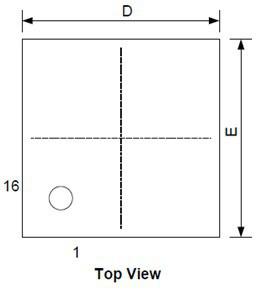

Optimized digital wireless communication chip system

PendingCN113139358ASimplify layout rulesImprove stabilityComputer aided designSpecial data processing applicationsFrequency mixerOperating system

The invention relates to the field of digital wireless communication chips, in particular to an optimized digital wireless communication chip system, which comprises a radio frequency controller, and an EEPROM, a data cache FIFO, an SPI interface, an IO controller, an RSSI detector, an IQ demodulator, an LNA, a mixer, a PA, a PLL, a VCO and a QFN16 package connected with the radio frequency controller. The SPI interface is a logic main SPI interface, and is connected to the radio frequency controller through four lines, namely a CSB, an FCSB, an SCLK and an SDIO; the IO controller comprises a logic input circuit and a logic output circuit which are connected with chip packaging pins GPIO1, GPIO2 and GPIO3; the RSSI detector is connected with the radio frequency controller, the IQ demodulator is connected with the radio frequency controller through an IPC channel, the LNA is directly connected to an antenna input end, the mixer is connected with the LNA and the VCO through a chip internal shielding circuit, and the PA is connected with an antenna output end and the VCO. The board arrangement and wiring rule of chip application is greatly simplified.

Owner:武汉工控仪器仪表有限公司

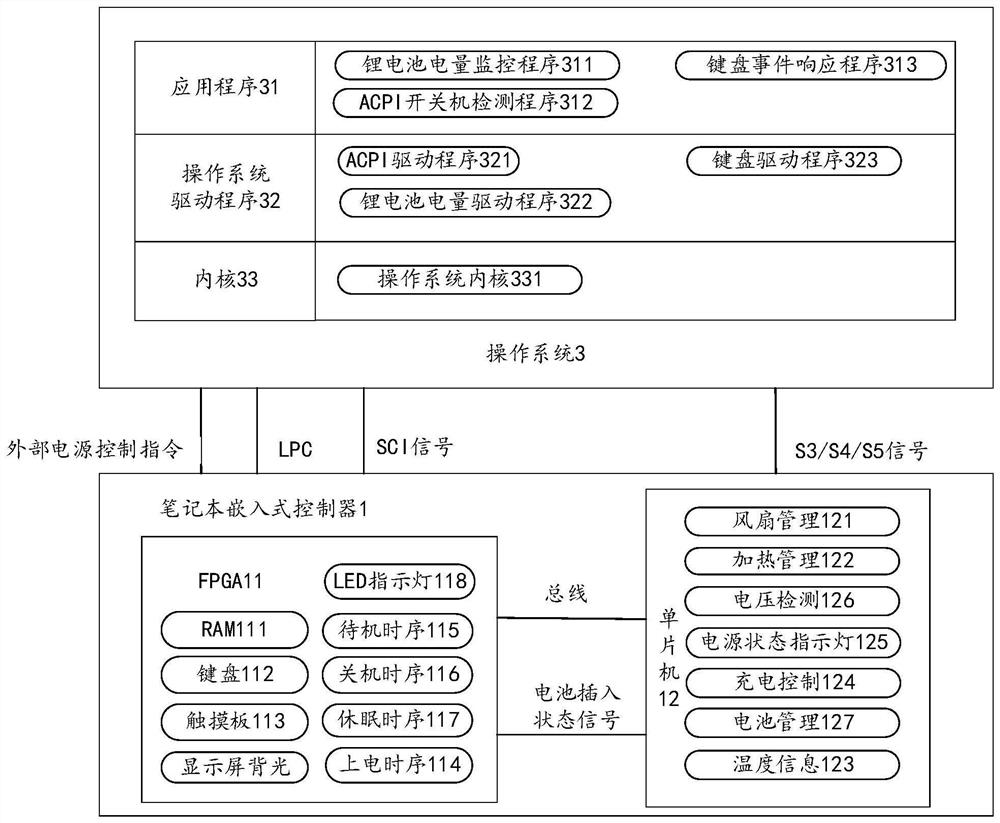

Notebook computer embedded controller and design method thereof

PendingCN113268448AReduce design difficultyLower Design BarriersVolume/mass flow measurementPower supply for data processingRandom accessField programmable logic

The invention discloses a notebook computer embedded controller, which comprises a field programmable logic gate array connected with an operating system, the field programmable logic gate array comprises a random access memory, and the field programmable logic gate array performs data interaction with the operating system through the random access memory; a single-chip microcomputer which is connected with the random access memory, the single-chip microcomputer is connected with the peripheral equipment, and the single-chip microcomputer is used for carrying out logic control on the notebook computer embedded controller and the peripheral equipment; wherein the random access memory is used for data interaction among the operating system, the field programmable logic gate array and the single chip microcomputer. The localization of the notebook embedded controller is realized, the special hardware platform of the existing notebook embedded controller is abandoned, the design difficulty of the notebook embedded controller is reduced, and the design threshold is reduced. The embodiment of the invention further discloses a method for designing the notebook computer embedded controller.

Owner:烟台北方星空自控科技有限公司

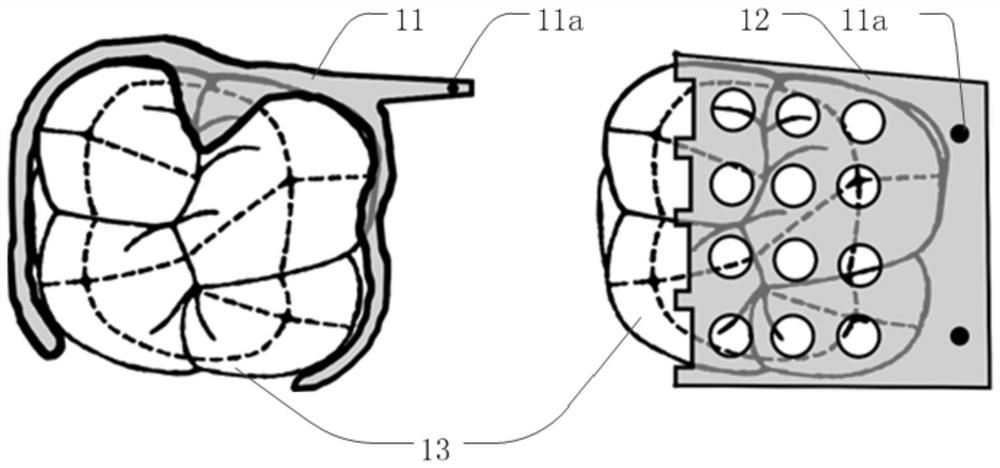

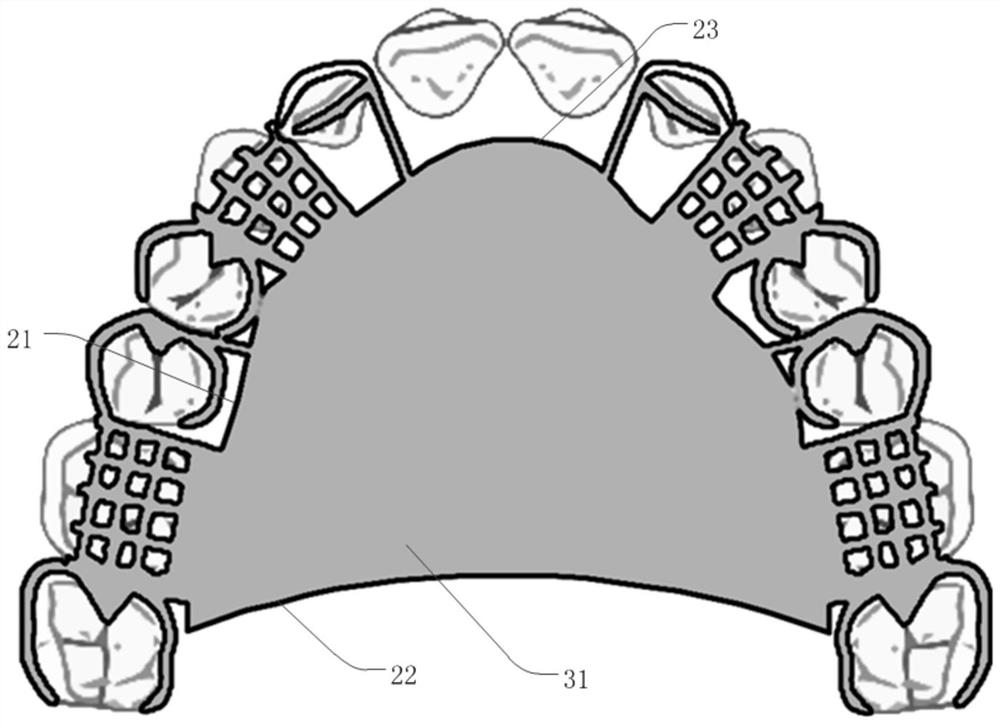

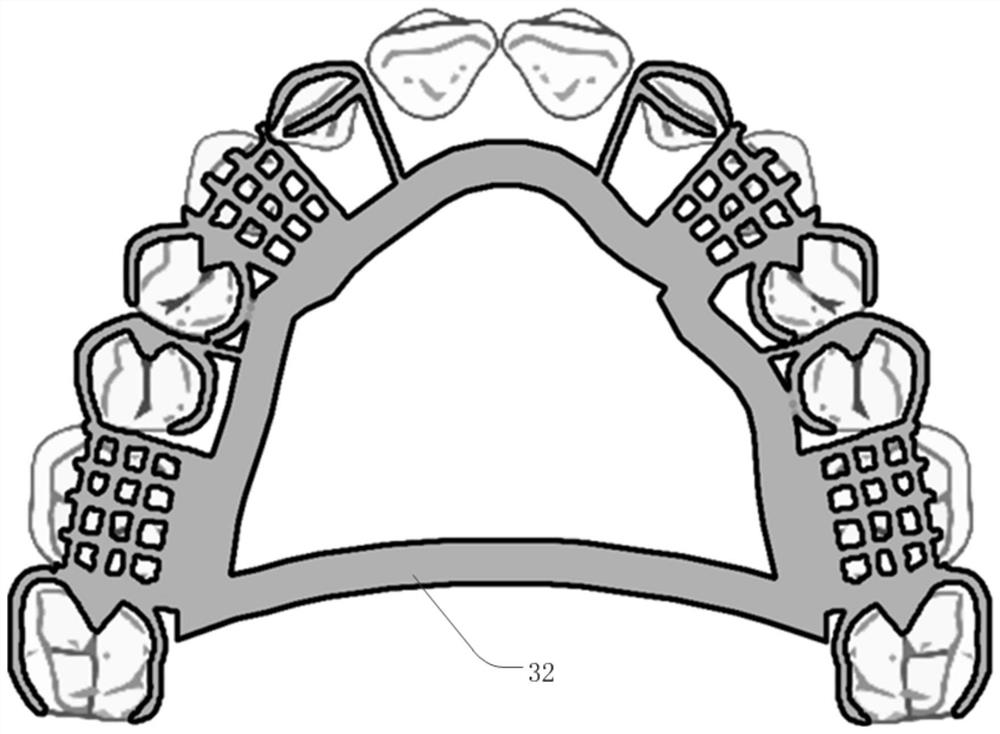

A Method of Using Bezier Curves to Design Large Connectors

The invention discloses a method for designing a large connecting body by using a Bezier curve. It includes the following steps: the step of importing the patient's oral data into the modeling system, the step of designing the clasp, the step of determining the connection point of the clasp, producing the anchor point according to the quantity information, position information and oral data of the clasp connection point, and based on the anchor A step of drawing the contour curve of the large connective body, and a step of drawing the large connective body according to the determined shape of the large connective body. The invention realizes the unified style design of the large connecting body through a simple and efficient design method, and is convenient for industrial processing. The large connector designed according to the method is highly matched with the patient's oral cavity, which can improve the user experience of the patient. The design scheme based on the invention facilitates seamless connection with other denture component designs.

Owner:SICHUAN UNIV