Integrated circuit clock tree comprehensive optimization method

A clock tree synthesis and optimization method technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as difficult to learn to the essence, improve design efficiency, increase the probability of getting it right, and reduce labor costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

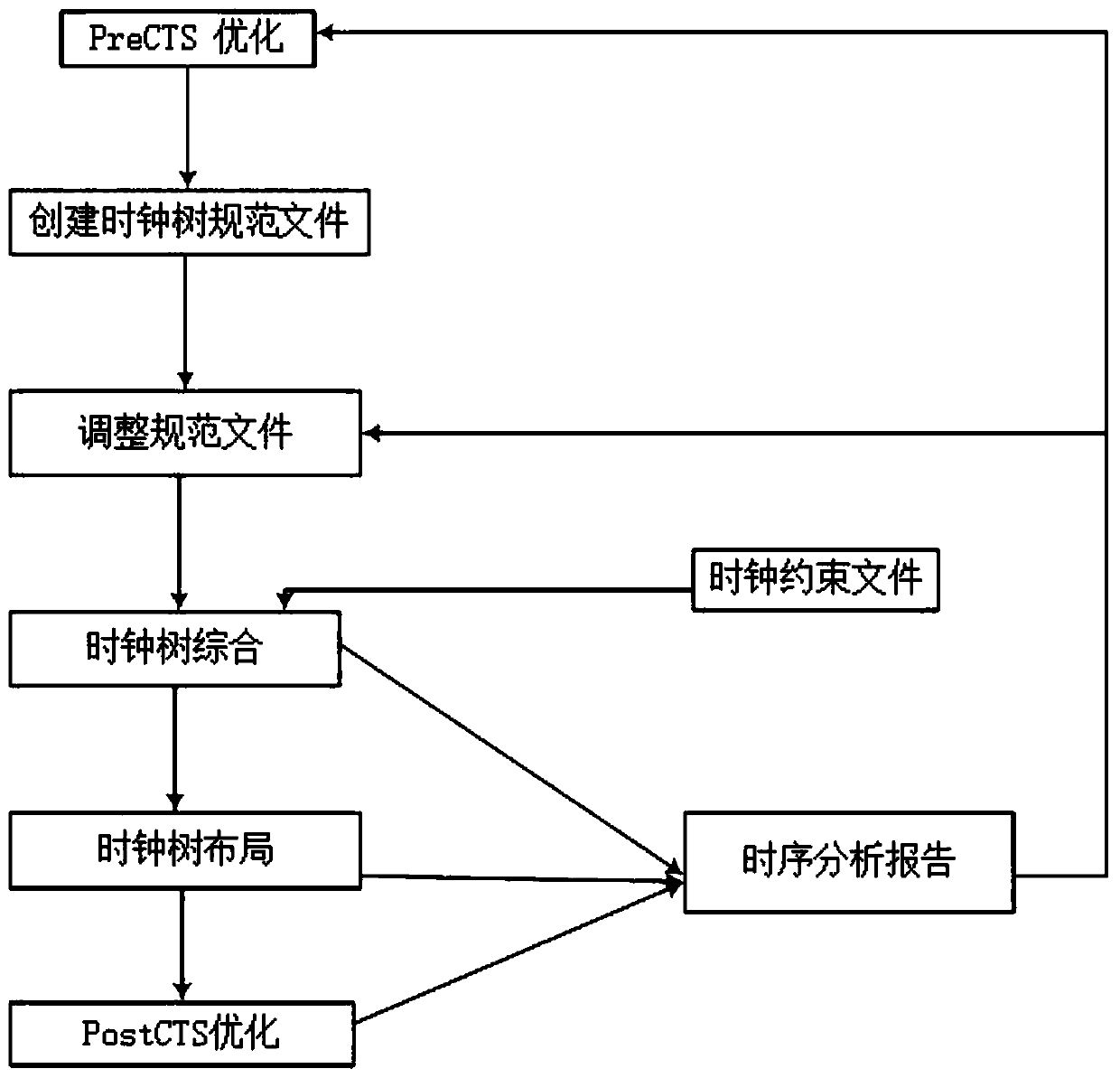

[0018] In the first embodiment of the present application, an integrated circuit clock tree synthesis optimization method is provided, such as figure 1 shown, including the following steps:

[0019] S1. Presetting the parameters in the clock tree constraint file;

[0020] S2. Automatically generate line layout according to parameters;

[0021] S3. Adjust the position of the register in the circuit layout, so that the difference between the clock source and the wiring length of each register is within a preset range;

[0022] S4. setting several driving units at the clock signal source to drive the load of the clock tree;

[0023] S5. Replace the driving unit so that the driving capacity of each driving unit is the same.

[0024] Among them, in step S1, these parameters include basic parameters such as buffer type, target value of clock skew, maximum delay, minimum delay, maximum fan-out, and clock tree wiring rules. As long as these parameters are set, you can Automaticall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More