Analog-to-digital converter device and clock pulse skew correction method

An analog-to-digital conversion and analog-to-digital technology, which is applied in the field of time-interleaved analog-to-digital converters and clock skew correction, can solve problems affecting resolution or linearity, gain error, and high cycle required for ADC power consumption correction. Achieve the effect of reducing power consumption and calibration cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] Embodiments of the present invention will be described below in conjunction with related drawings. In the drawings, the same reference numerals represent the same or similar elements or method flows.

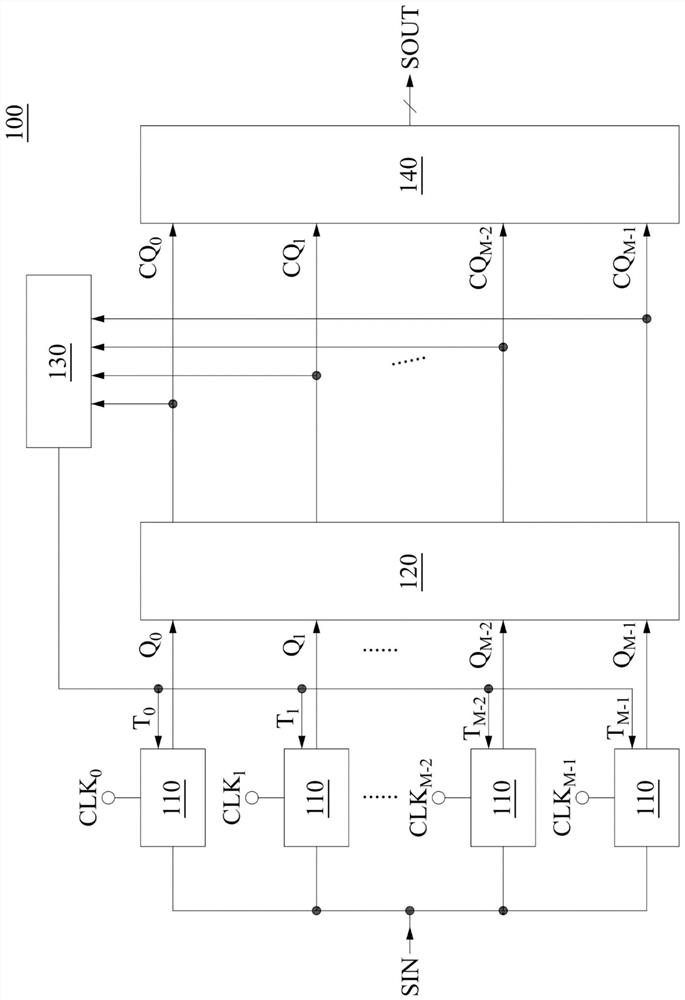

[0068] see Figure 1A and Figure 1B , Figure 1A It is a schematic diagram of an analog-to-digital converter (analog-to-digital converter, ADC) device 100 according to some embodiments of the present application. Figure 1B according to some embodiments of this case Figure 1A Multiple clock signals CLK in 0 ~CLK M-1 The schematic diagram of the waveform. In some embodiments, the ADC device 100 operates as a time-interleaved ADC with multiple channels.

[0069] In some embodiments, the ADC device 100 includes a plurality of analog-to-digital conversion circuits 110 , a correction circuit 120 , a skew adjustment circuit 130 and an output circuit 140 . It should be noted that each ADC circuit 110 operates as a single channel. In other words, in this example, the ADC ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More