Digital-assisted direct-current offset cancellation circuit and digital control method thereof

A DC offset elimination circuit technology, applied to electrical components, transmission systems, etc., can solve the problems of large chip area, high-pass bandwidth of signals, and difficulty in compromising the response speed of the DC offset elimination loop, so as to eliminate DC offset and avoid large chip area. big effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

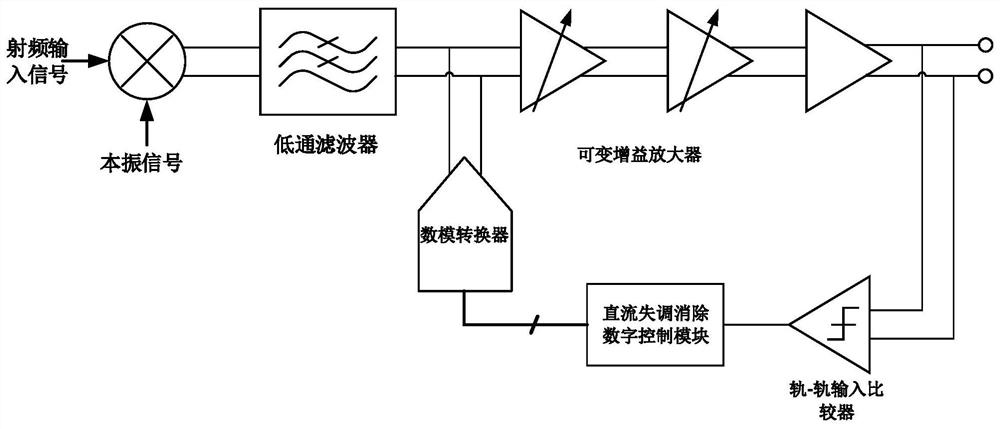

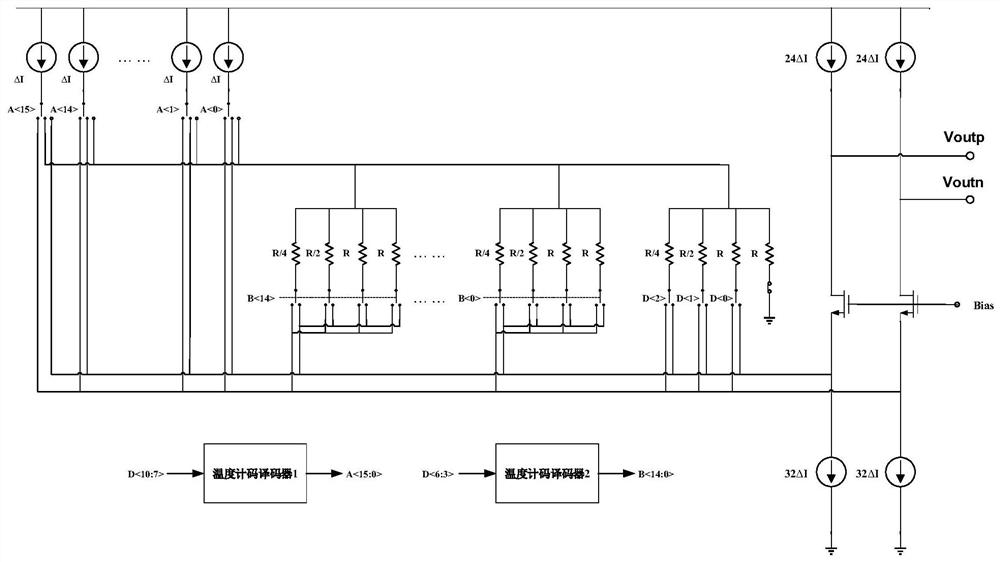

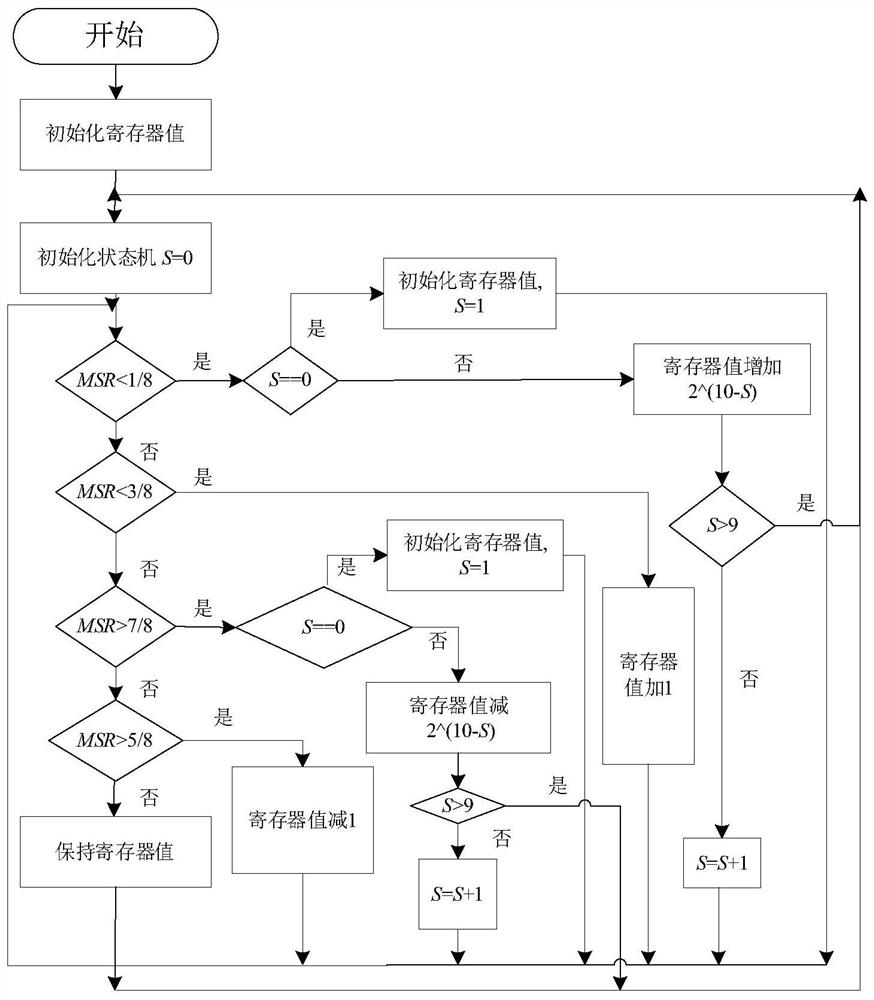

[0030] The present invention proposes a digital-assisted DC offset elimination circuit, including a variable gain amplifier, a comparator with a rail-to-rail input voltage range, a digital control module and an 11-bit digital-to-analog converter, and the electrical signal is input to the variable gain amplifier , a comparator with a rail-to-rail input voltage range samples the variable gain amplifier output differential voltage within a given time window, and r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More