Integrated memory cell and memory array

A technology of storage unit and storage transistor, which is applied in the field of memory, can solve the problem of unreliable data transfer, achieve high reliability, reduce production cost, and save the overall area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

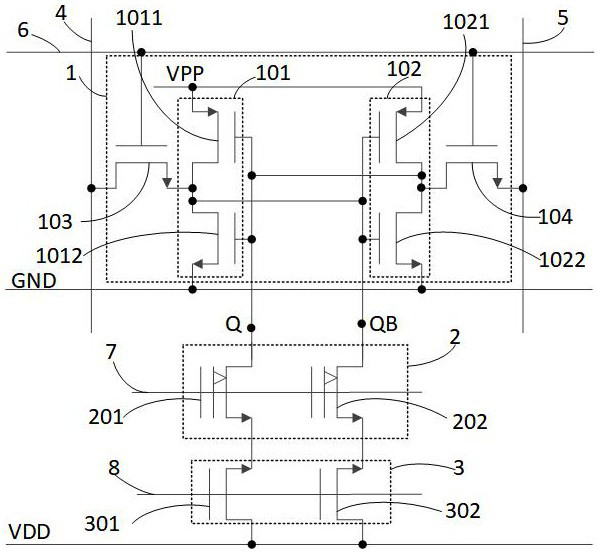

[0041] As a preferred embodiment of the present invention, the first inverter 101 includes a first PMOS transistor 1011 and a first NMOS transistor 1012, and the source of the first PMOS transistor 1011 is connected to the programming and erasing voltage terminal VPP, so The drain of the first PMOS transistor 1011 is connected to the drain of the first NMOS transistor 1012, the gate of the first PMOS transistor 1011 is connected to the gate of the first NMOS transistor 1012, and the first NMOS transistor 1012 The source is grounded. The second inverter 102 includes a second PMOS transistor 1021 and a second NMOS transistor 1022, the source of the second PMOS transistor 1021 is connected to the programming and erasing voltage terminal VPP, and the drain of the second PMOS transistor 1021 The pole is connected to the drain of the second NMOS transistor 1022, the gate of the second PMOS transistor 1021 is connected to the gate of the second NMOS transistor 1022, the source of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More