Three-dimensional semiconductor memory devices

A memory and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of increasing the integration of two-dimensional or planar semiconductor devices, and being extremely expensive

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

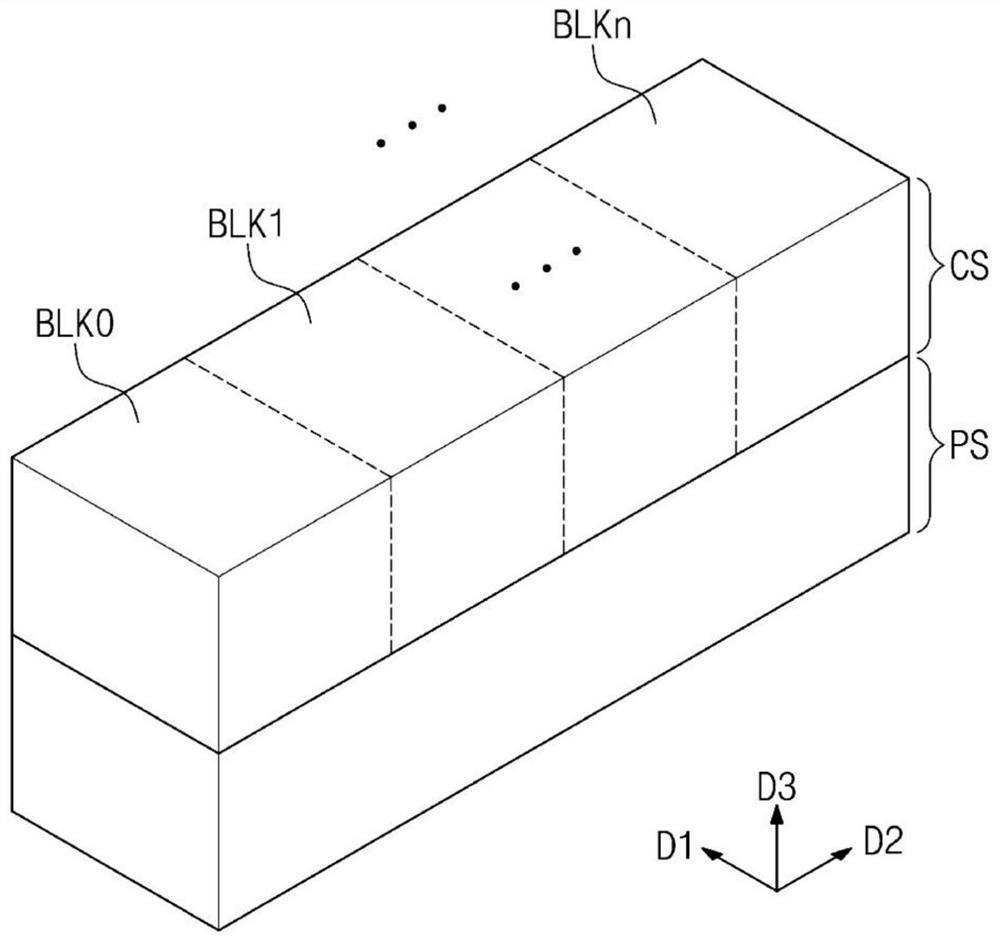

[0027] figure 1 is a schematic perspective view illustrating a three-dimensional semiconductor memory device according to some embodiments of the inventive concept.

[0028] refer to figure 1 A three-dimensional semiconductor memory device according to some embodiments of the inventive concepts may include a peripheral circuit structure PS, a cell array structure CS on the peripheral circuit structure PS, and through contacts ( not shown). The cell array structure CS may overlap the peripheral circuit structure PS when viewed in a plan view.

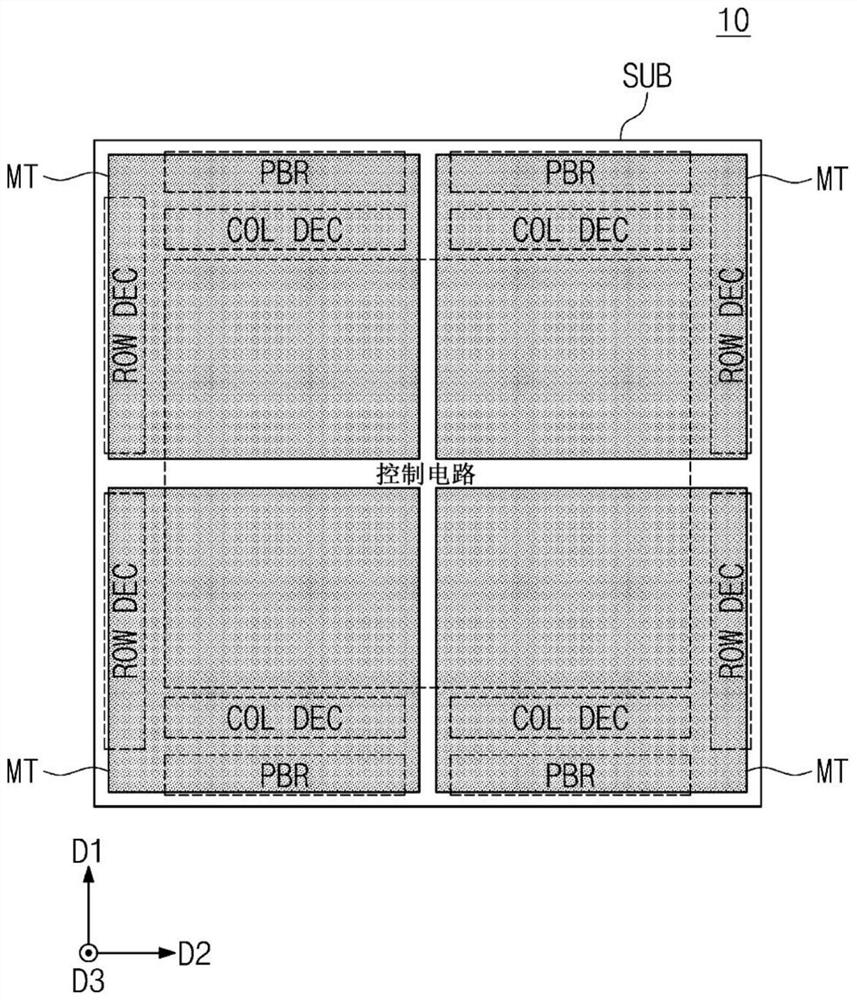

[0029] In some embodiments, the peripheral circuit structure PS may include row and column decoders, page buffers, control circuits, and peripheral logic circuits. Components of the peripheral circuit structure PS (eg, peripheral logic circuits) may be integrated on a semiconductor substrate.

[0030] The cell array structure CS may include a cell array including a plurality of memory cells three-dimensionally arranged on a semicondu...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap