Multi-chip packaging structure and packaging method

A multi-chip packaging and packaging method technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve problems such as affecting product reliability, unfilled space, touch, etc. Risk, relative height reduction, size reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to enable those skilled in the art to better understand the technical solutions of the present invention, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

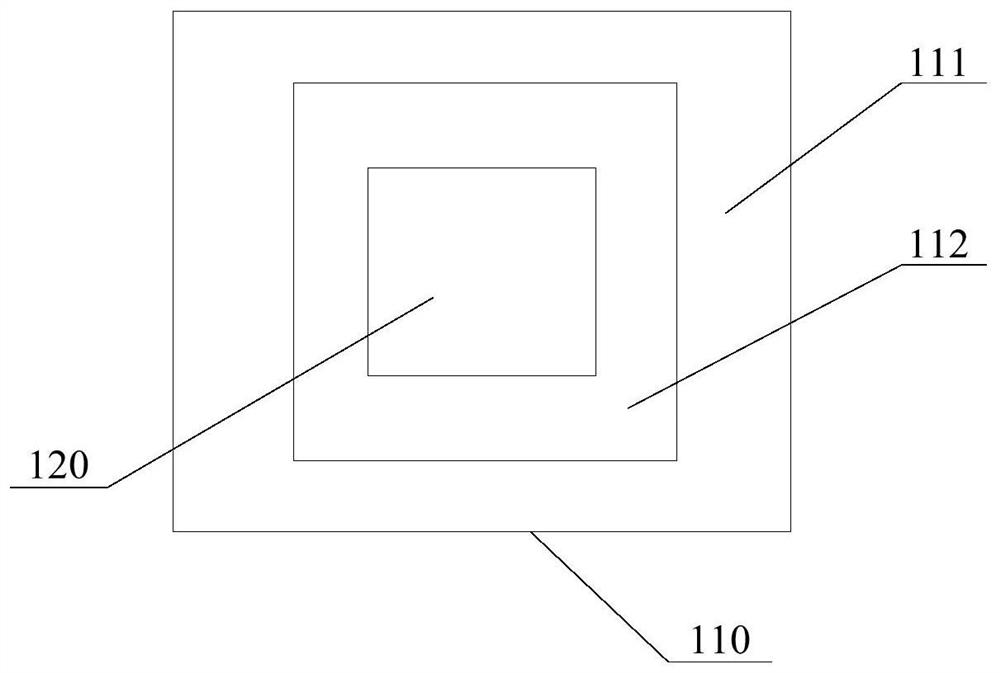

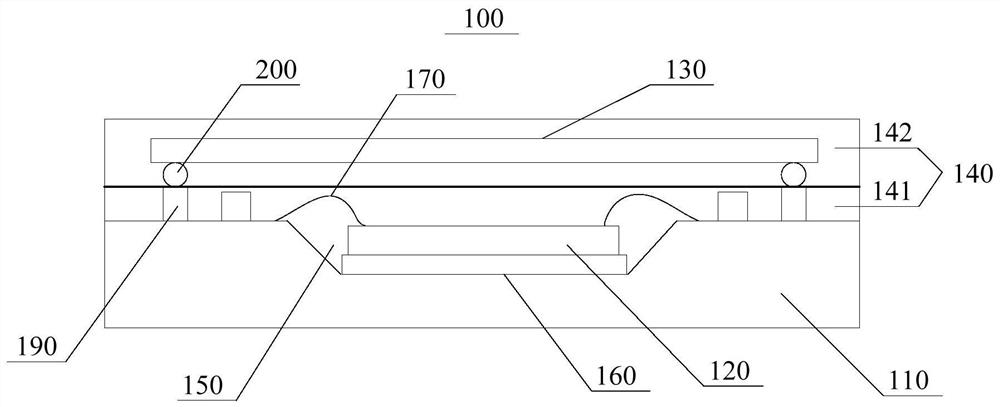

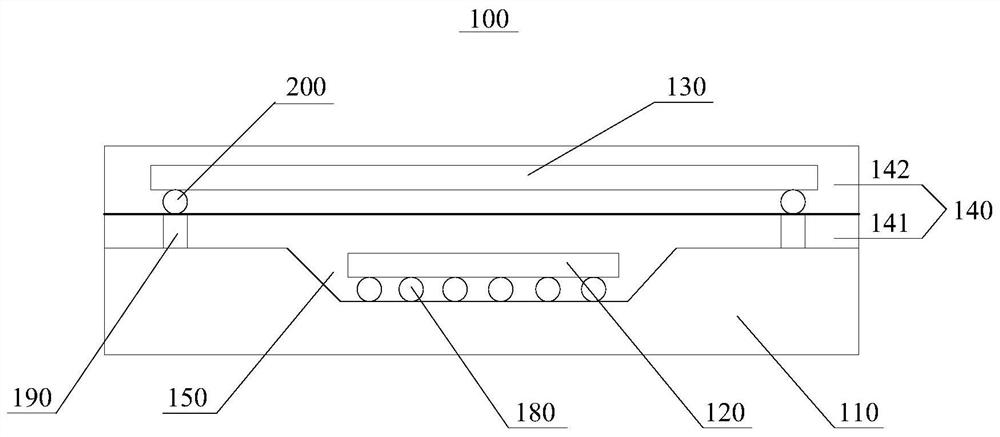

[0028] Such as figure 1 , figure 2 and image 3 As shown, one aspect of the present invention provides a multi-chip packaging structure 100 , including a substrate 110 , a first chip 120 , a second chip 130 and a plastic encapsulation layer 140 . The first chip 120 and the second chip 130 are sequentially stacked on the substrate 110, that is, as figure 2 As shown, the first chip 120 is disposed toward the substrate 110, the second chip 130 is disposed away from the substrate 110, and both the first chip 120 and the second chip 130 are electrically connected to the substrate 110. For example, the first chip 120 can be connected to the substrate 110 by wire bonding. The substrate 110 is electrically connected. In addi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com