High-density static random access memory bit unit structure and process method thereof

A bit cell, static random technology, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problems of unreasonable bit cell structure, high power consumption and cost, and poor high-density characteristics of static random access memory. Achieve the effect of reducing active area area, reducing power consumption and cost, and improving high-density characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

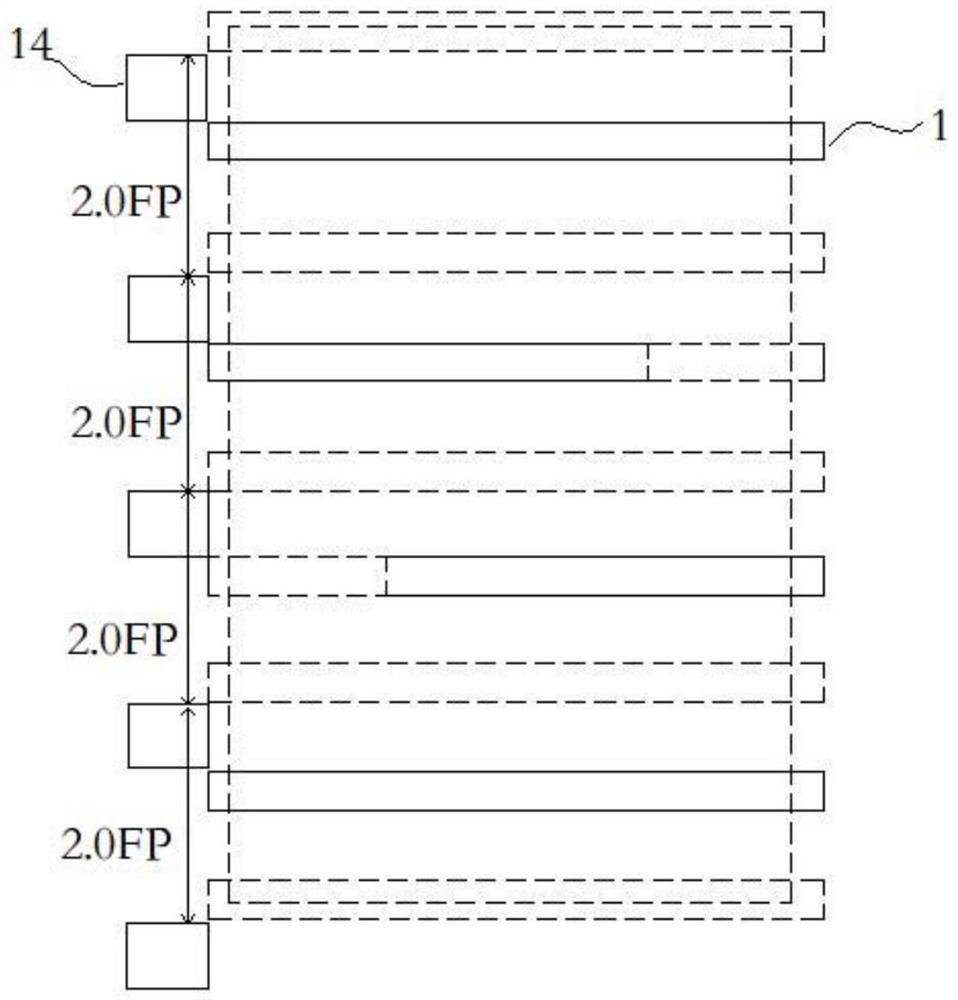

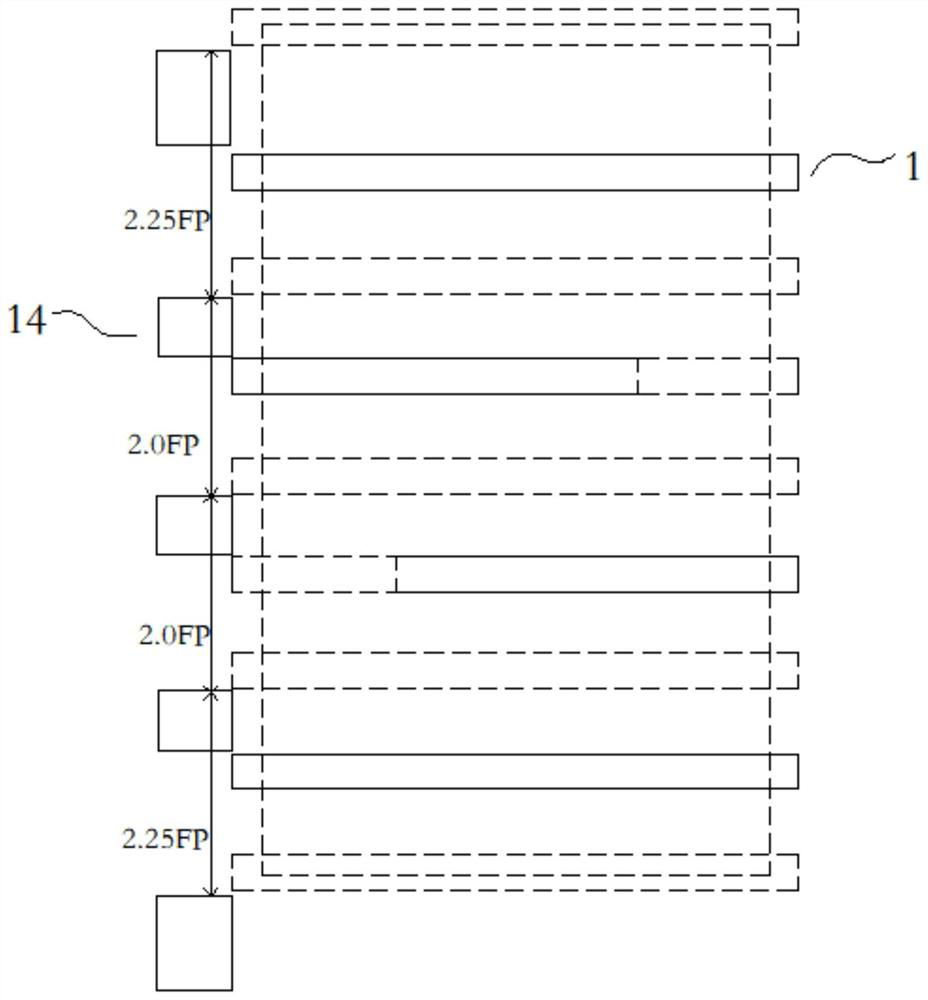

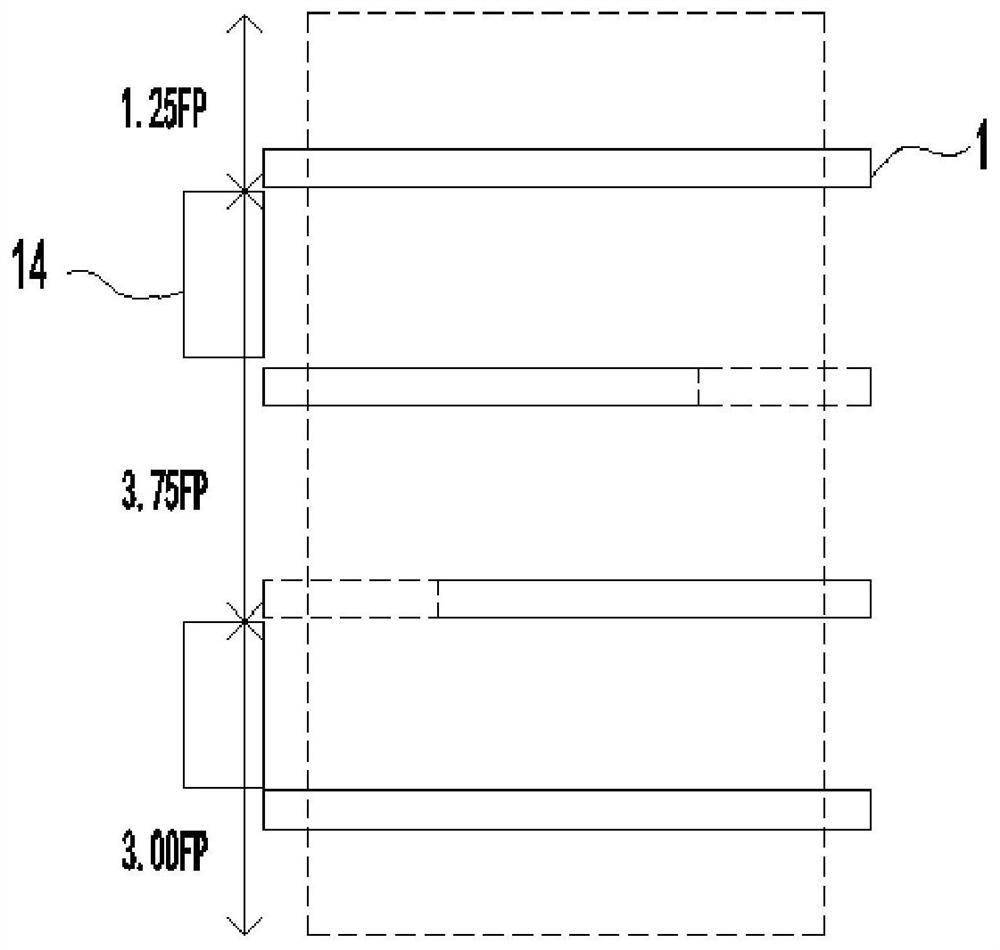

[0033] See image 3 and Figure 4 , a high-density SRAM bit cell structure, which includes a substrate, fins 1 distributed on the surface of the substrate, gate regions 2 distributed on the fins 1, a photoresist layer 14, a contact layer 4, a read The bit line 5, the substrate is silicon, the bit unit includes a 22nm fin field effect transistor 6, the fin field effect transistor 6 is a PMOS transistor, including two fins, a gate region, a contact layer, and a part for reading the bit line Area; fin 1 includes four: the first fin, the second fin, the third fin, and the fourth fin, and are distributed in parallel at intervals in sequence, wherein the tail of the second fin and the head of the third fin are cutting areas. Assuming that the fin pitch between two adjacent fins 1 is FP, and the contact layer pitch is CPP, then the total vertical width of the active area of the bit cell is 8*FP, and the total vertical width of the active area is the total fin pitch direction. Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More