Semiconductor structure and forming method thereof

A semiconductor and isolation structure technology, applied in the field of semiconductor structure and its formation, can solve the problems of insufficient remaining thickness of the hard mask layer, narrowing of the sacrificial layer, uneven trench depth, etc., to reduce the impact of the etching process and avoid The effect of narrowing and consistent groove depth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] As mentioned in the background, the prior art CFET formation method needs to be improved.

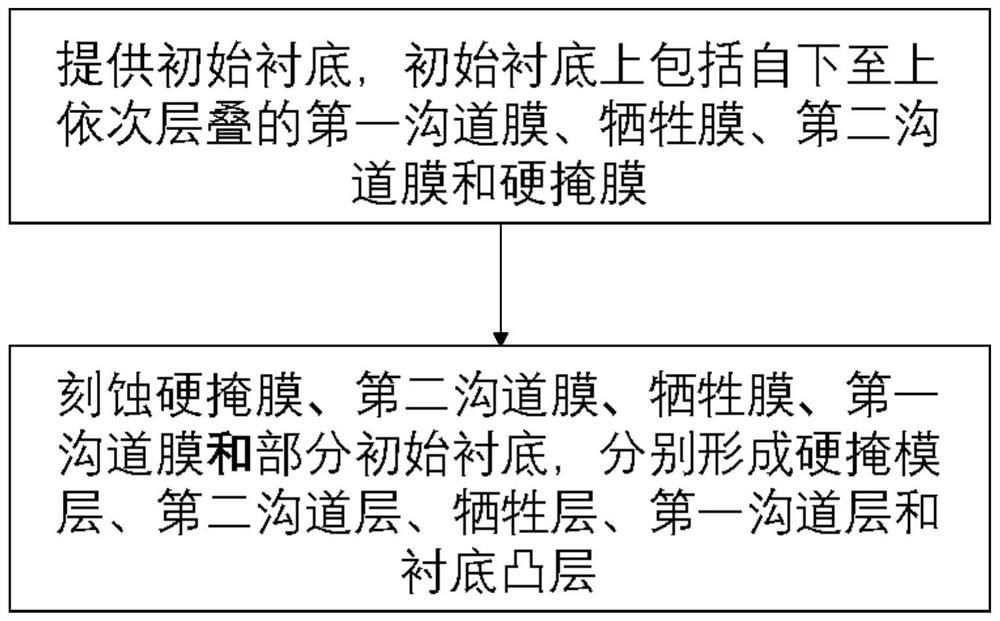

[0041] figure 1 A flowchart of a method for forming a semiconductor structure is shown, the method includes: providing an initial substrate, the initial substrate includes a first channel film, a sacrificial film, a second channel film and a first channel film stacked sequentially from bottom to top. Hard mask: etching the hard mask, the second channel film, the sacrificial film, the first channel film and part of the initial substrate to form a hard mask layer, a second channel channel layer, sacrificial layer, first channel layer and substrate convex layer.

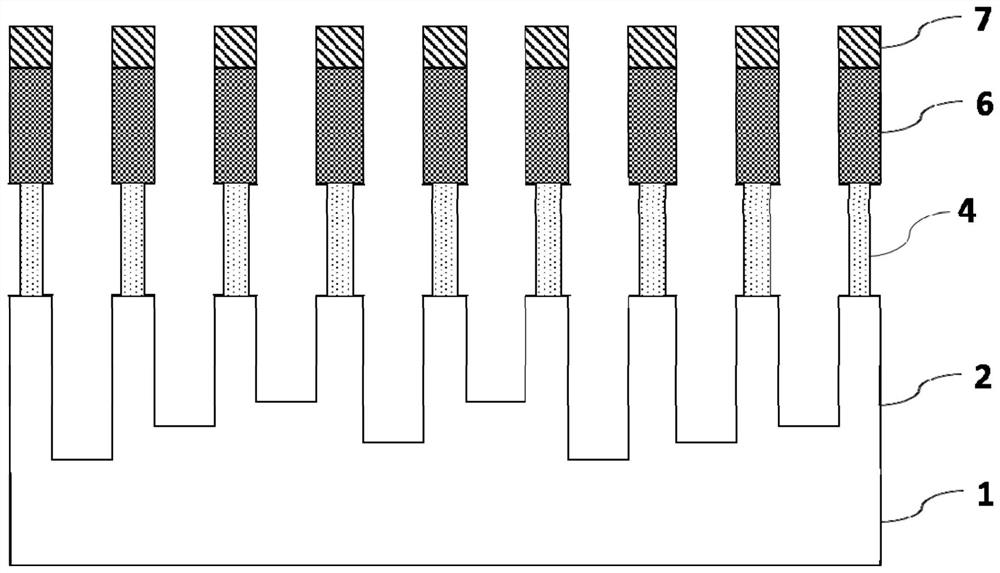

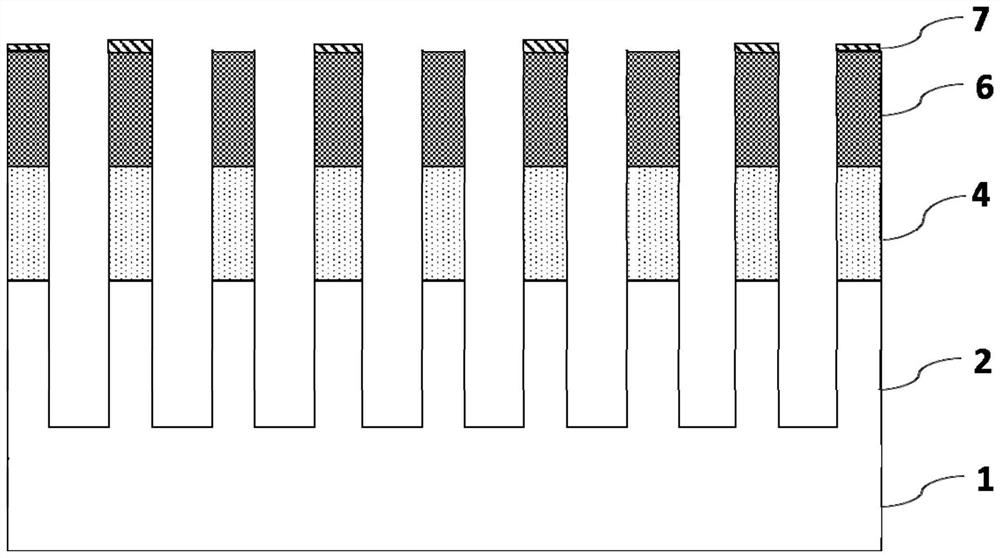

[0042] Through the above method can be formed as figure 2 The semiconductor structure shown includes a substrate 1, a substrate convex layer 2 above the substrate 1, a first channel layer 4 above the substrate convex layer 2, and a channel layer above the first channel layer 4. The second channel layer 6 and the hard m...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More