Preparation method of low-trigger and low-capacitance chip type electrostatic suppressor

An electrostatic suppression and low triggering technology, applied in the direction of protection against damage caused by electrostatic discharge, electric solid devices, circuits, etc., can solve problems such as low capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

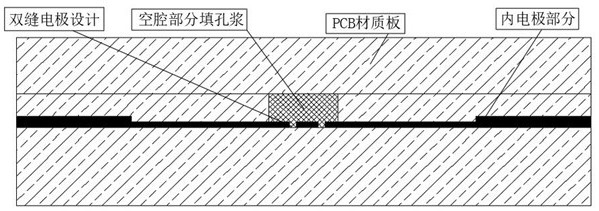

[0026] Such as figure 1 As shown, a preparation method of a low-trigger, low-capacity chip electrostatic suppressor comprises the following steps:

[0027] S1: Slurry selection: A combination of nano-material preparation technology, semiconductor materials, polymer materials and PCB board technology is used to print a functional material layer with a loose skeleton structure and semiconductor characteristics on the electrode grooving part. There are sharp edges and The functional paste is a gap formed by a loose skeleton structure to achieve low voltage characteristics;

[0028] S2: Laser cutting: the electrode gap prepared by laser precision cutting, the width of the gap is controlled, and the electrode is prepared through the copper clad laminate to combine with the substrate to ensure the triggering performance of the device and provide a convenient channel for electron transmission;

[0029] S3: Double slit design: use double slit cutting electrode, the cutting slit is 12~1...

Embodiment 1

[0040] The width of the slit in the step S2 is controlled to be 13um, and the sum of the slit widths of the double slits is 28um.

[0041] In step S3, the electrode is cut with a double slit design, and the cut slit is 13um.

[0042] In step S2, on the basis of ensuring no leakage, the device minimizes the trigger voltage to 280V and the operating voltage to 2KV to achieve better ESD responsiveness.

[0043] In step S3, a double-slit electrode design is used to achieve low capacitance, which solves the problem of ultra-small capacitance, and the capacitance is reduced from the existing 0.15pf to 0.07pf.

Embodiment 2

[0045] The width of the slit in the step S2 is controlled to be 14um, and the sum of the slit widths of the double slits is 29um.

[0046] In step S3, the electrode is cut with a double slit design, and the cut slit is 14um.

[0047] In step S2, on the basis of ensuring no leakage, the device minimizes the trigger voltage to 290V and the operating voltage to 2KV to achieve better ESD responsiveness.

[0048] In step S3, a double-slit electrode design is used to achieve low capacitance and solve the problem of ultra-small capacitance. The capacitance is reduced from the existing 0.15pf to 0.071pf.

[0049] Working principle: Combining nano-material preparation technology, semiconductor materials, polymer materials and PCB board technology, printing a functional material layer with a loose skeleton structure and semiconductor characteristics on the electrode grooving part, and there are sharp and functional pastes in the grooving part of the electrode The gap formed by the loos...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More