SOC (system on chip) simulation verification method and device, verification server and storage medium

A verification server and simulation verification technology, which is applied in the field of SOC verification test, can solve the problems of long loading time, low communication rate between emulator and simulation verification equipment, waiting in line, etc., so as to save hardware equipment cost, shorten verification test time, reduce The effect of labor intensity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

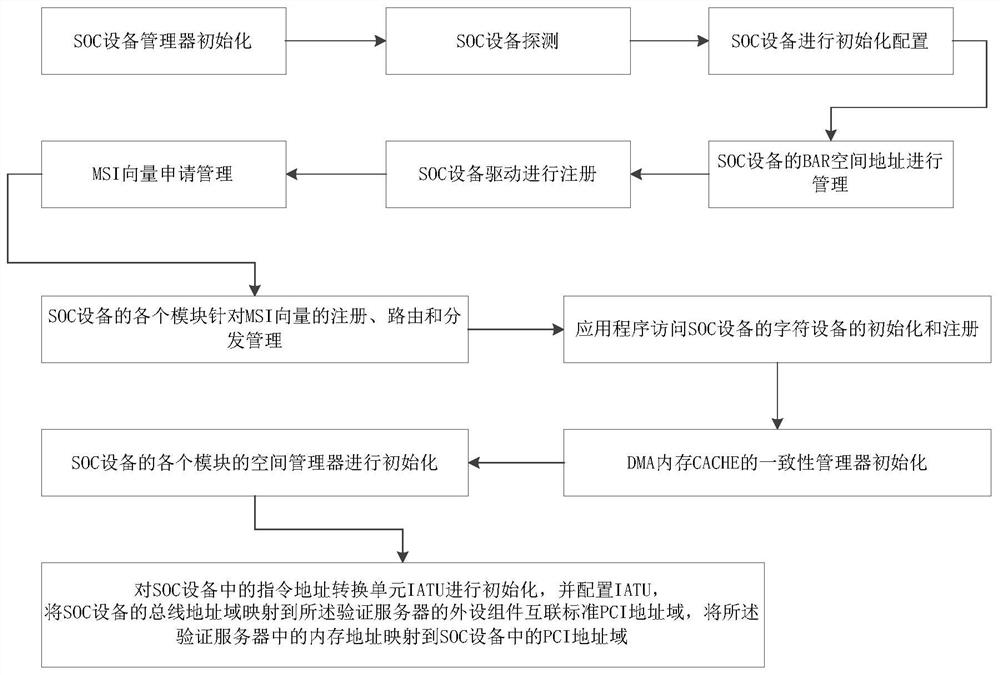

[0026] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only some structures related to the present invention are shown in the drawings but not all structures.

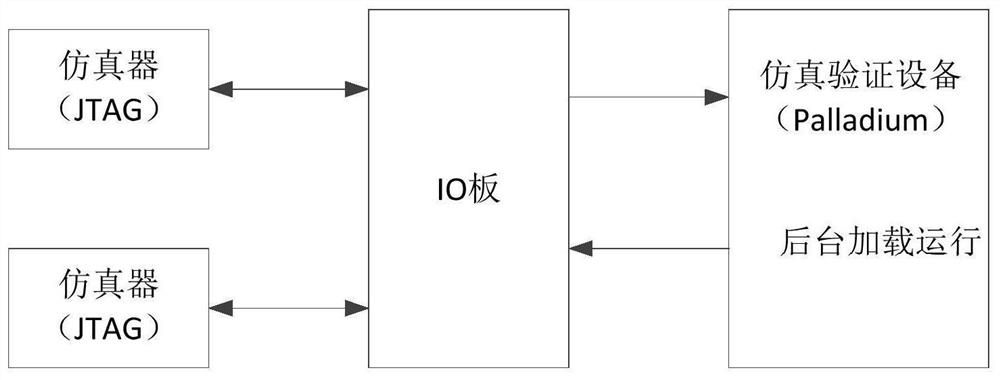

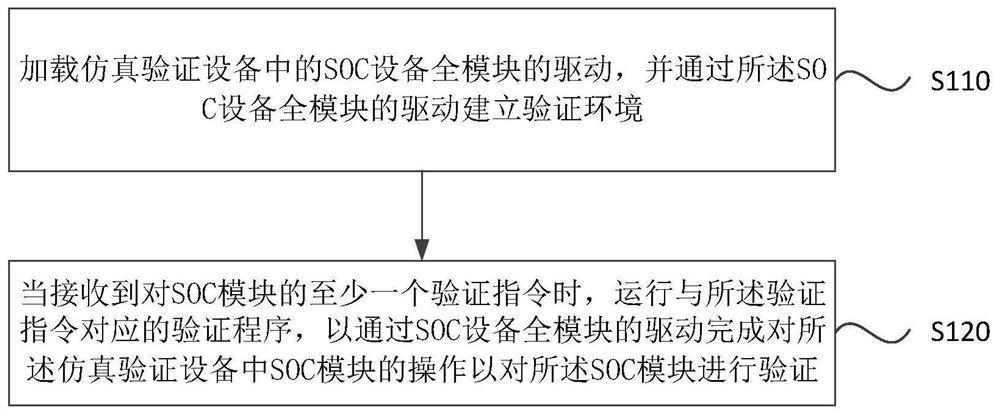

[0027] Figure 1b It is a flow chart of a system-on-chip SOC simulation verification method provided by an embodiment of the present invention. The method can be executed by a system-on-chip SOC simulation verification device. The device can be configured on a verification server, and the verification server is installed with an operation system, and the method can be applied to the scenario where multiple users perform verification tests on the SOC module on the simulation verification device in parallel.

[002...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More