Negative capacitance L-shaped gate tunneling field effect transistor and preparation method thereof

A technology of tunneling field effect and negative capacitance, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc. It can solve the problems of limited improvement of device characteristics, difficulty in increasing the tunneling probability of LG-TFET, etc., and increase the channel surface The effect of electric potential, large band-to-band tunneling rate, and large on-state current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

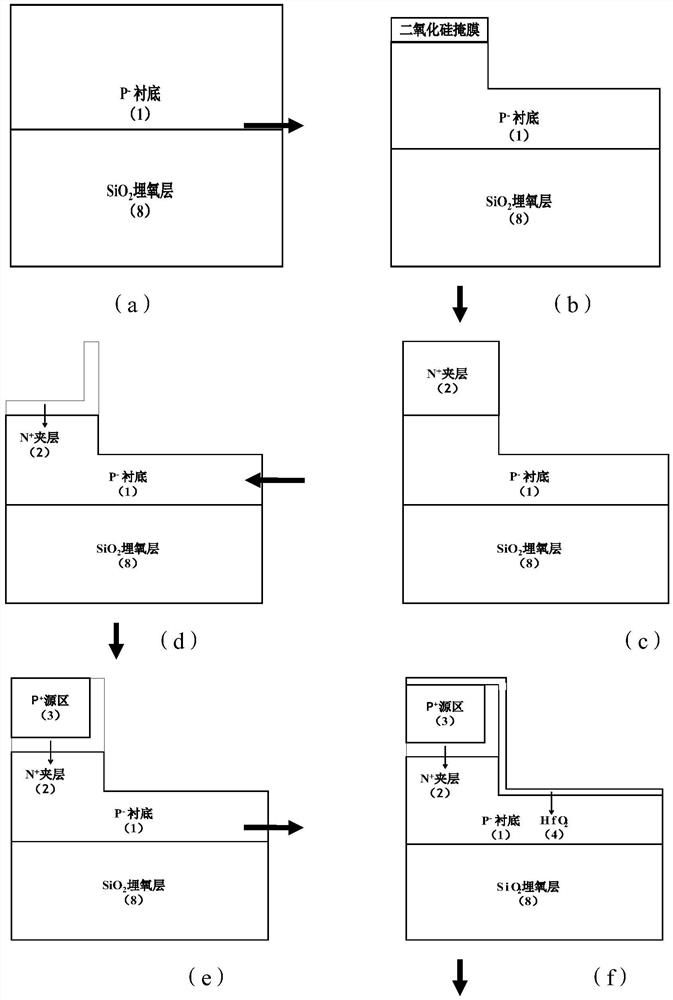

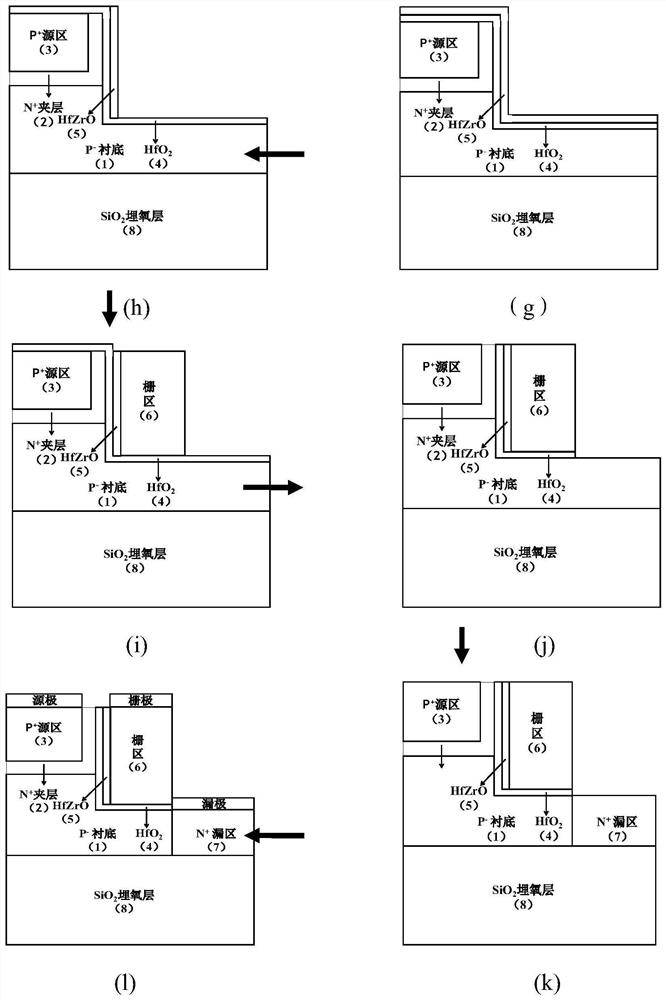

[0042] Embodiments of the present invention will be described in detail below in conjunction with examples, but those skilled in the art will understand that the following examples are only used to illustrate the present invention, and should not be considered as limiting the scope of the present invention.

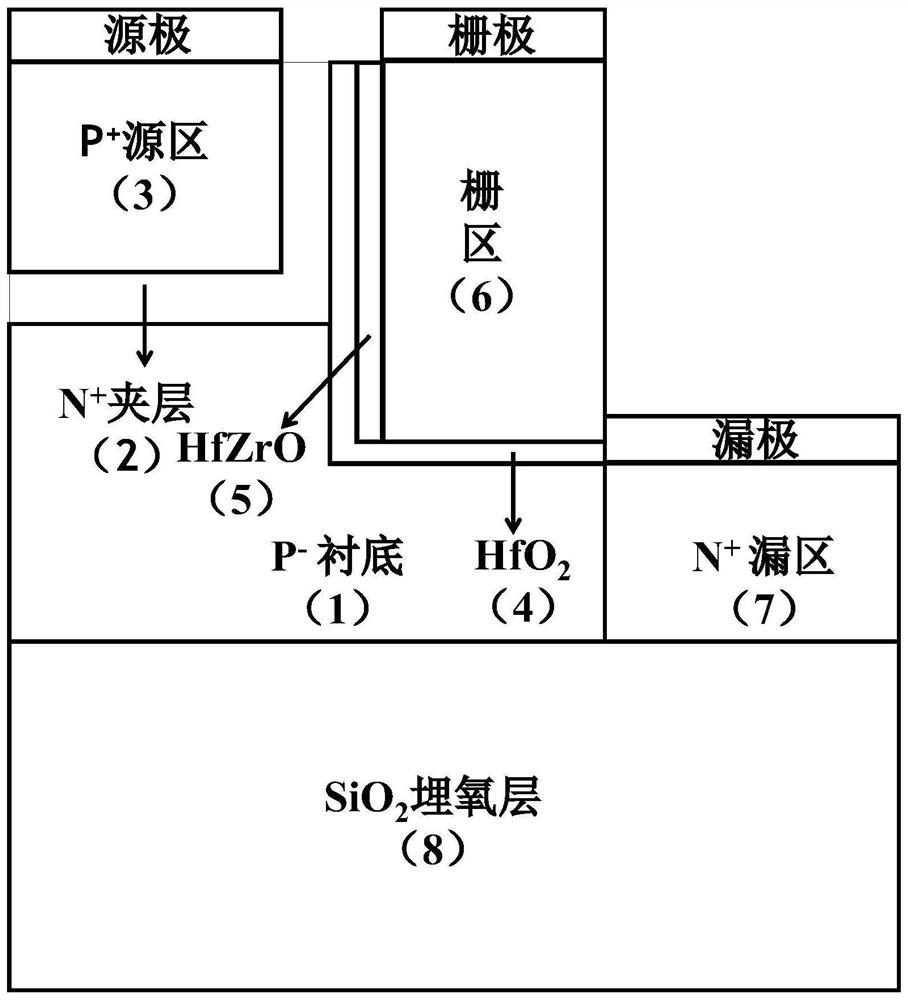

[0043] refer to figure 1 , is a negative capacitance L-type gate tunneling field effect transistor of the present invention, comprising: a P-substrate 1, a P+-type source region 3, a gate region 6, and a drain region 7, wherein, the bottom of the P-substrate 1 is provided with Buried oxide layer 8, N+ type interlayer 2 is deposited on the upper left part of the P-substrate 1, a lower step is etched on the right side of the P-substrate 1, and the drain region 7 is located on the upper part of the lower step, and its thickness is the same as that of the P-substrate 1 same;

[0044] An upper step is etched on the N+ type interlayer 2, a P+ type source region 3 is deposited ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com