Method for screening MOS (Metal Oxide Semiconductor) device with electric leakage path

A MOS device and path technology, applied in the field of screening MOS devices with leakage paths, can solve problems such as affecting the electrical characteristics of the device, and achieve the effect of solving time-consuming and easy-to-occur omissions, avoiding unfavorable factors, and ensuring reliability and consistency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

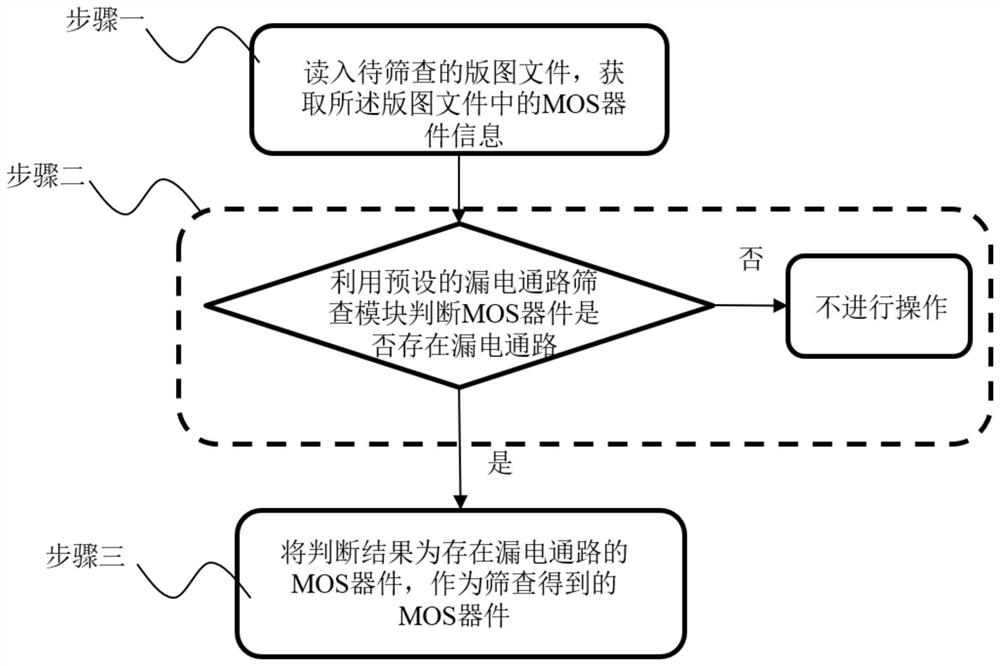

[0025] The method for screening MOS devices with leakage paths in this embodiment, such as figure 1 As shown, it includes: Step 1. Read in the layout file to be screened to obtain the MOS device information in the layout file; Step 2. Use the preset leakage path screening module to determine whether there is a leakage path in the MOS device; Step 3. The judgment result is that the MOS device with a leakage path is used as the screened MOS device. In this embodiment, the preset leakage path screening module defines the conditions for judging whether there is a leakage path in the MOS device. An example of the layout file to be screened is the gds file, and the information of the gds file is obtained to determine whether the source and / or drain of a MOS device is connected to the source and / or drain of other MOS devices. The judgment conditions of the example specifically include: if there is a source terminal and a drain terminal of a certain MOS device connected together with...

Embodiment 2

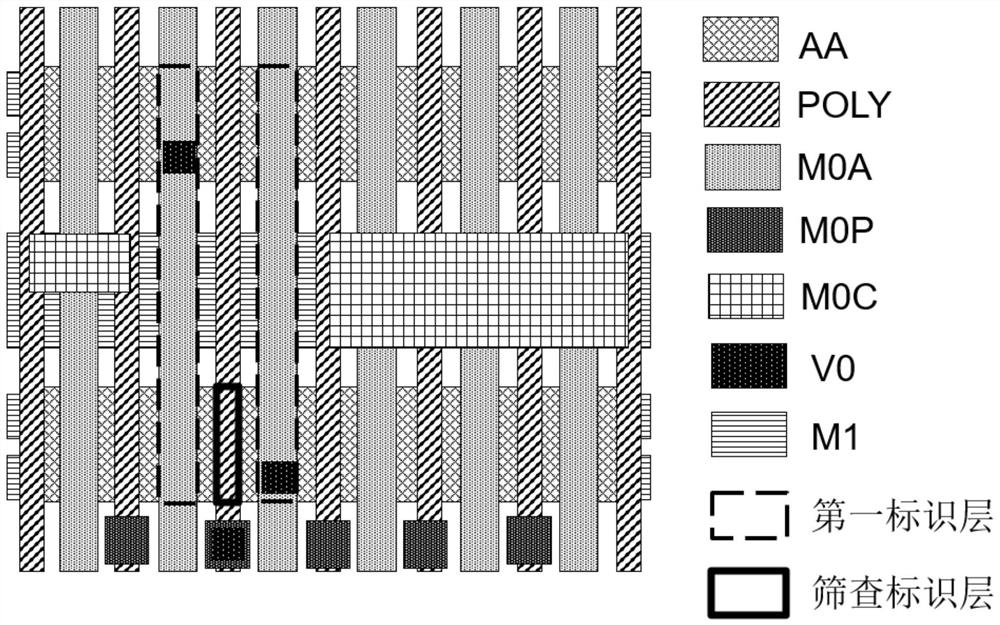

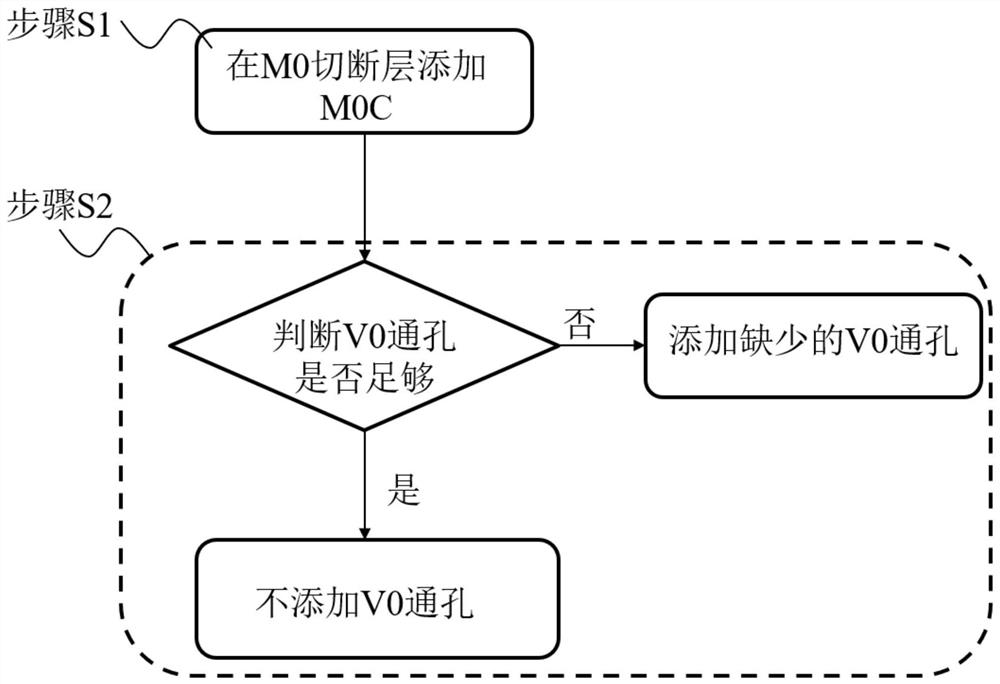

[0028] refer to figure 2In this embodiment, a first identification layer is added to the read-in layout file, and the first identification layer is added with first information for locating the target device; the first information includes: characterizing the source terminal and / or drain terminal of the target device Coordinate information and shape information of the M0 connection line connected to the source terminal and / or drain terminal of other MOS devices (floating gate). The shape information of the M0 connection line is exemplified by its length and width. Wherein, the M0 connection line is in the M0 layer, and is used to connect the active area (AA, ie source or drain) or gate of the MOS device. In this embodiment, the exemplary M0 includes M0A and M0P, M0A is used to connect to the active region (ie source or drain), and M0P is used to connect to the gate. The V0 via is connected to the gate through M0P. In this embodiment, the first identification layer is used ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More