Data transmission system of FPGA and DSP based on SRIO protocol

A data transmission system and data technology, applied in the field of data transmission, can solve the problems of difficulty in guaranteeing the stability of the synchronous sampling clock, affecting the accuracy of back-end data processing, etc., and achieve the effect of good versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

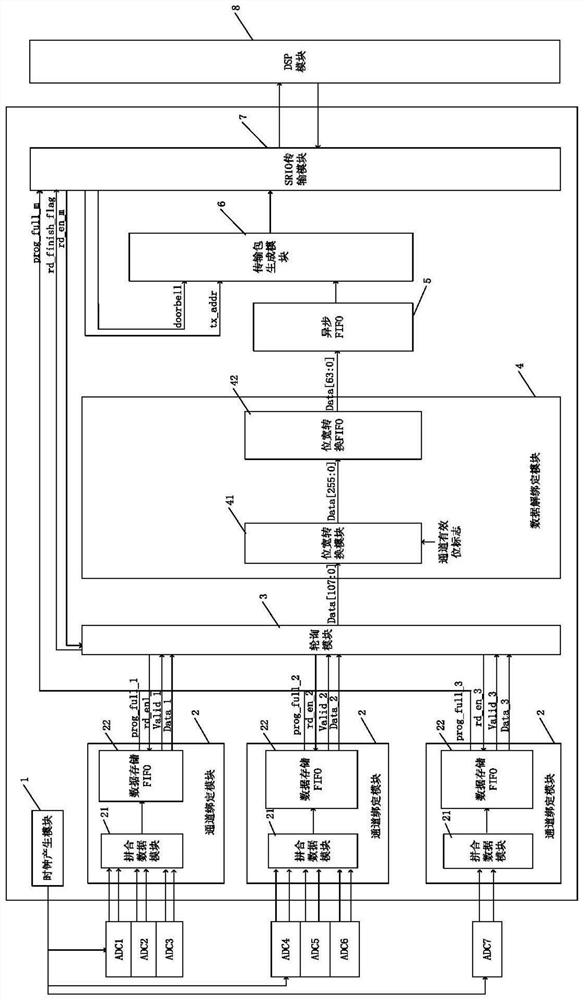

[0026] figure 1 It is a structural diagram of a specific embodiment of the data transmission system of the FPGA and DSP based on the SRIO protocol of the present invention. Such as figure 1 Shown, the present invention is based on the data transmission system between FPGA and DSP of SRIO protocol and comprises clock generation module 1, M channel binding modules 2, polling module 3, data unbinding module 4, asynchronous FIFO5 realized in FPGA , a transmission packet generation module 6 , an SRIO transmission module 7 , and a DSP module 8 . Each module is described in detail below.

[0027] The clock generating module 1 is used to generate M synchronous sampling clocks according to actual needs, for selection and use of acquisition boards, and the value of M is determined according to actual conditions.

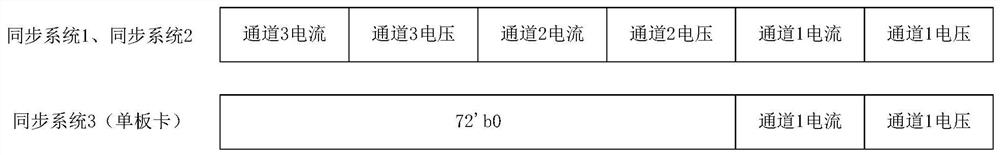

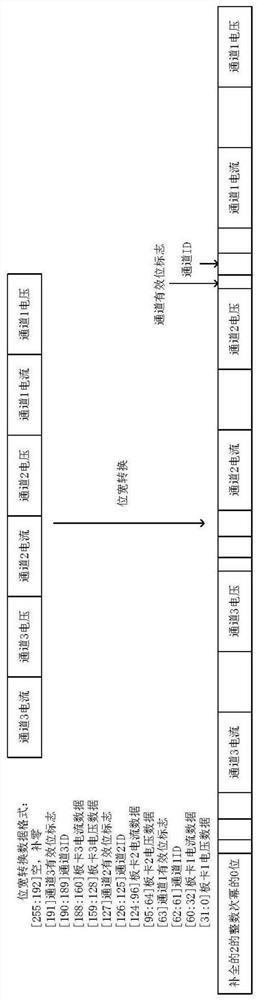

[0028]Each channel binding module 2 includes a splicing module 21 and a data storage FIFO22, and the splicing module 21 of the mth channel binding module will use the colle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More