Cache replacement system and method based on instruction stream and memory access mode learning

A technology of cache replacement and pattern learning, applied in memory systems, machine learning, computing models, etc., can solve the problems of reducing uncertainty and difficulty in learning memory access behavior patterns, and achieve the effect of reducing uncertainty and avoiding interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0058] The present invention will be described in further detail below through specific implementation examples and accompanying drawings.

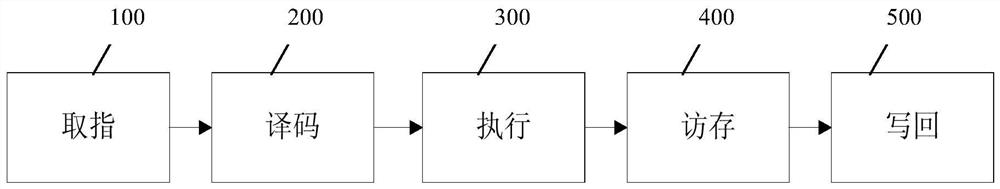

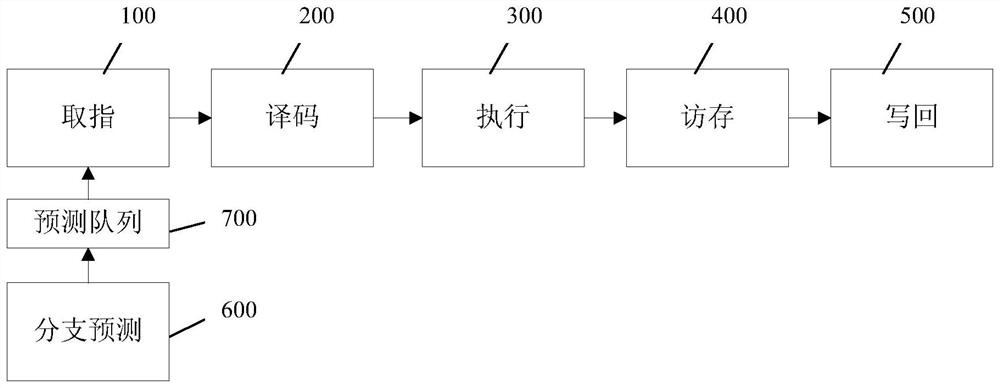

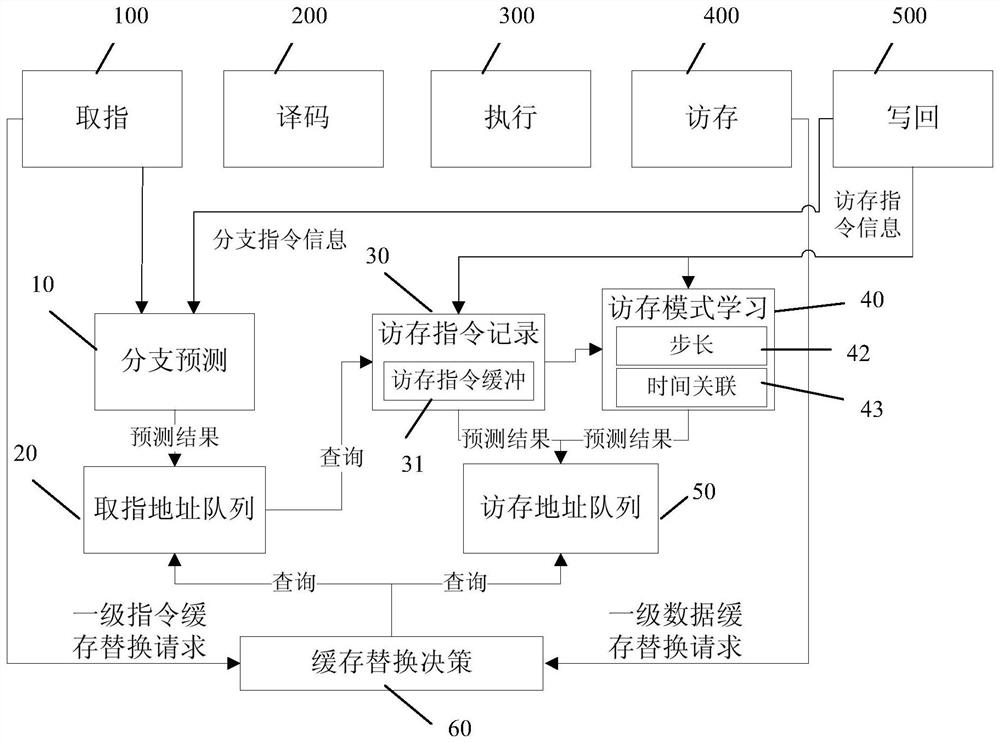

[0059] The cache replacement system and method based on instruction stream and memory access mode learning of the present invention are applicable to figure 1 in the processor microarchitecture shown. The processor microarchitecture includes at least five stages of instruction fetching, decoding, execution, memory access, and write-back, and these five stages correspond to the instruction fetch unit 100, the decoding unit 200, the execution unit 300, and the memory access unit 400 and write back to unit 500. The invention is equally applicable to figure 1 In a more complex processor microarchitecture with the functions shown, a certain stage may be refined in a more complex processor microarchitecture, for example, the execution stage may be split into three sub-stages: renaming, scheduling, and execution.

[0060] Such as figure 2 A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More