Mapping method applied to network-on-chip IP core mapping problem

A mapping method and network-on-chip technology, applied in the field of network-on-chip design and application, can solve problems such as insufficient premature convergence, achieve the effect of avoiding premature convergence, improving the ability of premature convergence, and improving quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

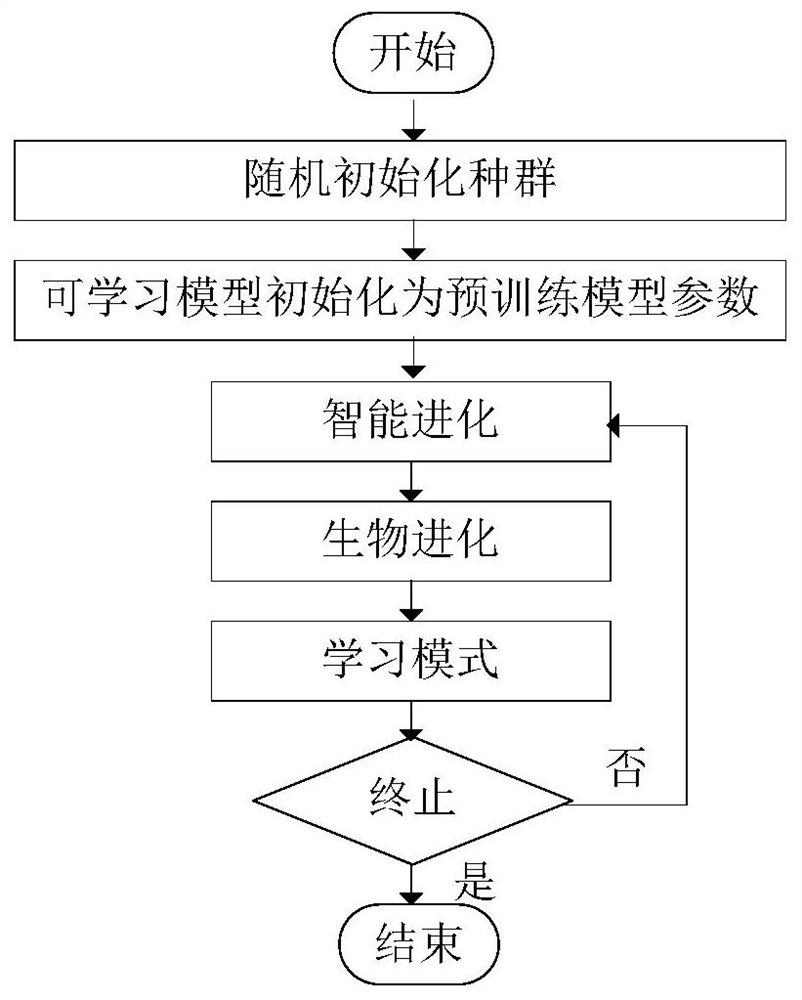

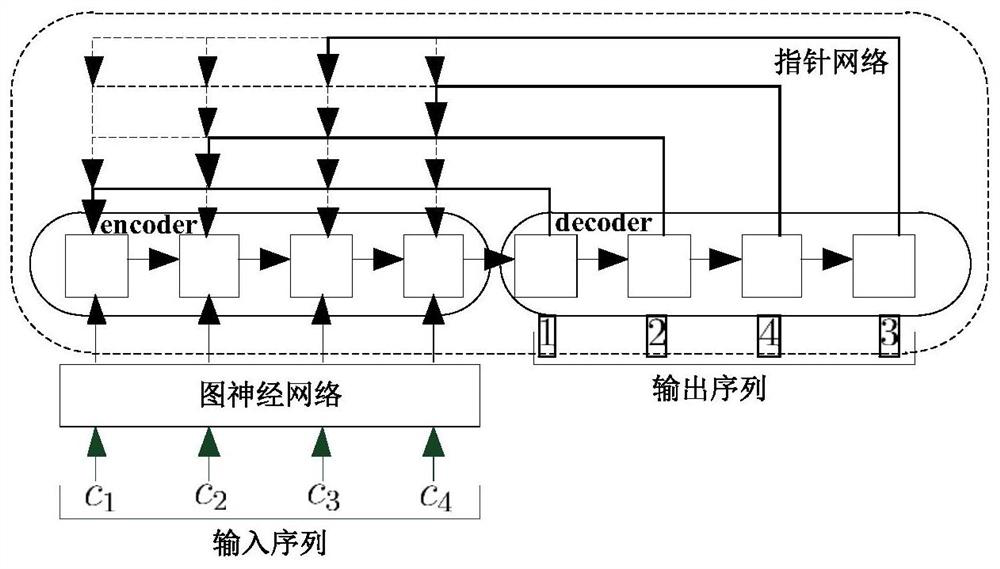

[0059] like figure 1 As shown, a mapping method applied to the network-on-chip IP core problem, this embodiment will be illustrated by applying the mapping method to solve the IP core mapping problem of 2Dmesh's communication power consumption awareness, and the entire solution includes the following steps:

[0060] S1: In the genetic algorithm, the chromosome of the individual is used as a feasible solution to mark, where each value m i Represents a gene in a chromosome and indicates the IP core Placed at NoC node r i , A represents the total number of IP cores, and A=4 is set in this embodiment. individual fitness The corresponding negative communication power consumption is evaluated. Then, the lower the fitness of the chromosome, the higher the corresponding communication power consumption. In this embodiment, a genetic algorithm is used to solve the IP core mapping problem.

[0061] S2: Randomly generate an initialization population, and initialize the learnable m...

Embodiment 2

[0106] A computer system includes a memory, a processor, and a computer program stored in the memory and operable on the processor. When the processor executes the computer program, the steps of the method are as follows:

[0107] S1: In the genetic algorithm, the chromosome of the individual is used as a feasible solution to mark, where each value m i Represents a gene in a chromosome and indicates the IP core Placed at NoC node r i , A represents the total number of IP cores;

[0108] S2: Randomly generate an initialization population, and initialize the learnable model as a pre-trained model parameter, and the learnable model estimates the probability distribution of the optimal solution in the entire solution space according to the prior knowledge obtained from the pre-training;

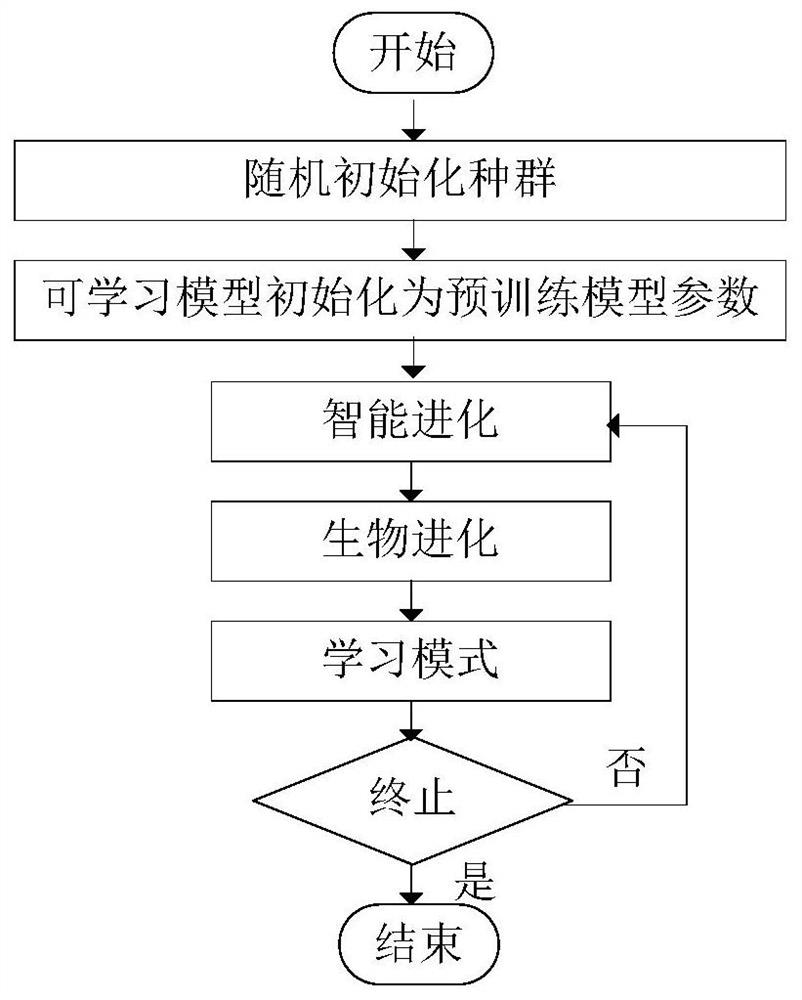

[0109] S3: Perform population iteration on the population initialized in step S2 sequentially through intelligent evolution, biological evolution, and learning modes, and repeat iterative ev...

Embodiment 3

[0111] A computer device, comprising a memory, a processor, and a computer program stored on the memory and operable on the processor. When the processor executes the computer program, the steps of the method are as follows:

[0112] S1: In the genetic algorithm, the chromosome of the individual is used as a feasible solution to mark, where each value m i Represents a gene in a chromosome and indicates the IP core Placed at NoC node r i , A represents the total number of IP cores;

[0113] S2: Randomly generate an initialization population, and initialize the learnable model as a pre-trained model parameter, and the learnable model estimates the probability distribution of the optimal solution in the entire solution space according to the prior knowledge obtained from the pre-training;

[0114]S3: Perform population iteration on the population initialized in step S2 sequentially through intelligent evolution, biological evolution, and learning modes, and repeat iterative ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More