Three-dimensional board-level fan-out type packaging structure and manufacturing method thereof

A packaging structure and manufacturing method technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as inability to meet multi-functional and other application requirements, high processing costs of packaging structures, and unstable dimensions. Achieve the effect of improving area utilization, low cost, offsetting bending and dimensional instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

[0042] like Figure 1 to Figure 10 A preferred embodiment of the manufacturing method of a three-dimensional board-level fan-out packaging structure shown, which includes the following steps:

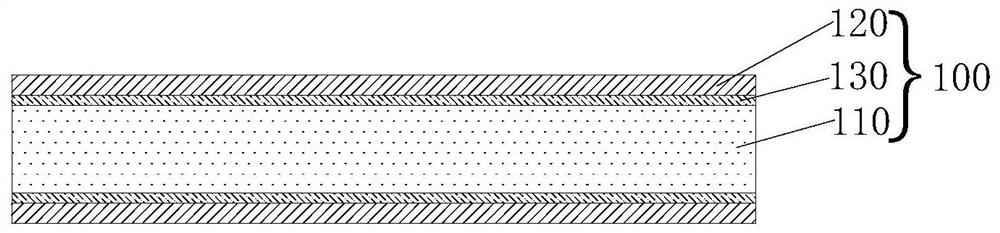

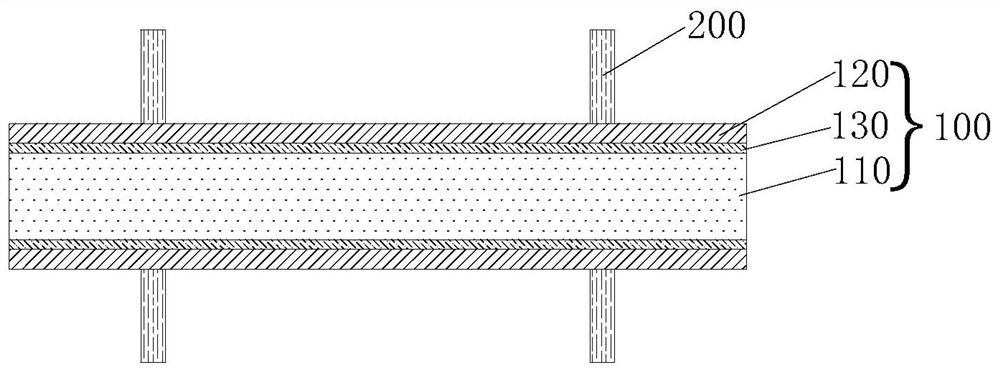

[0043] S1, take a carrier sheet 110, apply an adhesive on the front and back of the carrier sheet 110 respectively to form an adhesive layer 130; then bond the copper foil 120 to the adhesive layer 130 to form a composite carrier 100; The material of the carrier sheet 110 can be one of silicon, glass, metal or organic material or a combination of multiple materials; in this embodiment, the carrier sheet 110 is preferably made of silicon;

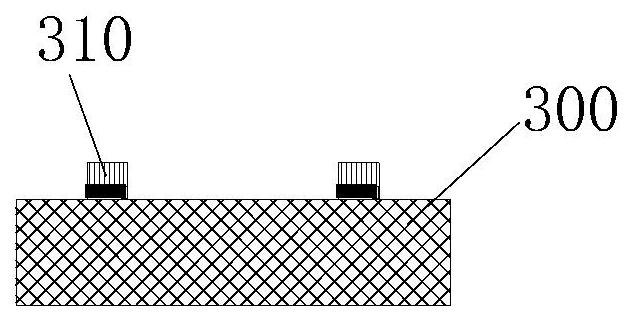

[0044] S2, maki...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More