EDA (Electronic Design Automation) hardware acceleration method and system based on Banyan network and multi-FPGA (Field Programmable Gate Array) structure

A hardware acceleration and network technology, which is applied in the direction of multi-program device, program startup/switching, resource allocation, etc., can solve the problem of occupying large resources, achieve efficient functions, realize simple structure, and reduce the effect of data exchange delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain related inventions, rather than to limit the invention. It should also be noted that, for the convenience of description, only the parts related to the related invention are shown in the drawings.

[0047] It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other. The present application will be described in detail below with reference to the accompanying drawings and embodiments.

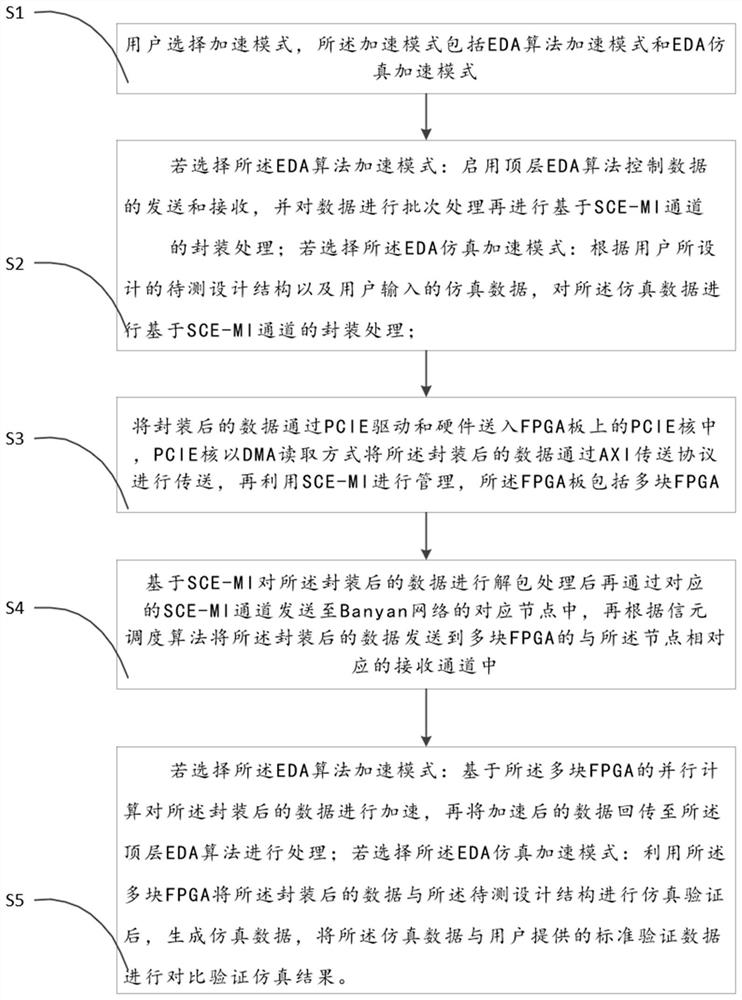

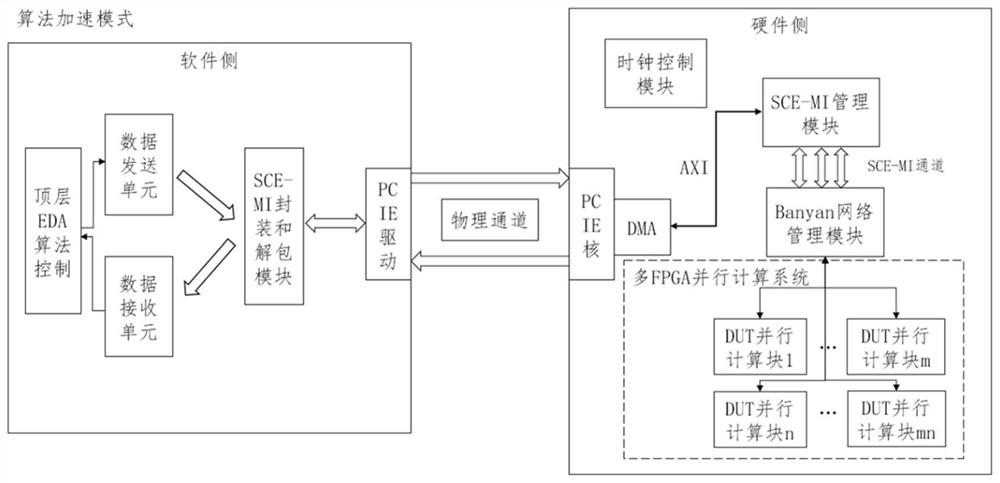

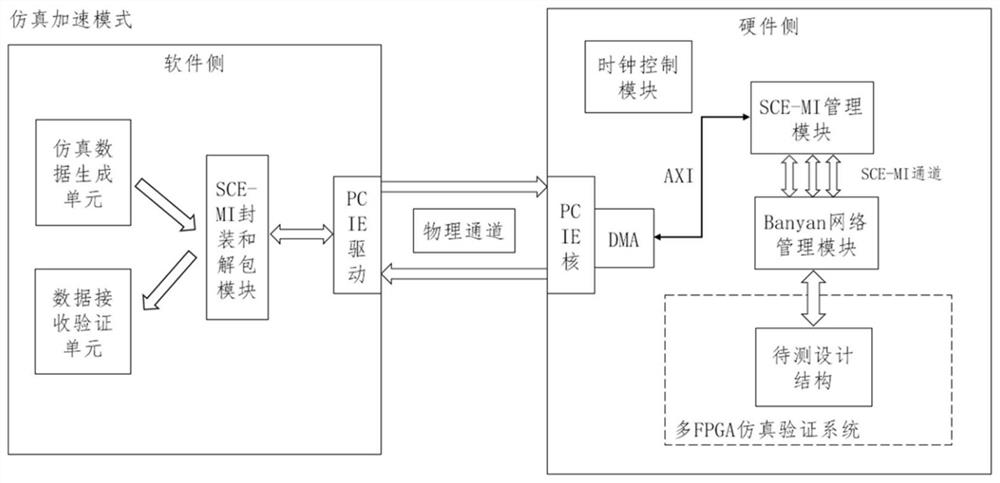

[0048] A kind of EDA hardware acceleration method based on Banyan network and multi-FPGA structure according to an embodiment of the present invention, figure 1 A flowchart of an EDA hardware acceleration method based on a Banyan network and a multi-FPGA structure is shown a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More